En el complejo terreno del diseño de hardware digital, la claridad es fundamental. Los ingenieros y diseñadores dependen de representaciones visuales para comunicar cómo se comportan las señales con el paso del tiempo. El diagrama de tiempo se erige como una de las herramientas más críticas para este propósito. Transforma la lógica abstracta en una línea temporal visual, revelando la danza entre estados altos y bajos a través de diversos componentes. Sin embargo, a medida que los sistemas crecen en complejidad, estos diagramas pueden volverse abrumadores. Esta guía explora una estrategia modular para descomponer y analizar diagramas de tiempo de manera efectiva, asegurando precisión y fiabilidad en la verificación de hardware.

Comprender el flujo de señales de datos y de control es esencial para prevenir fallos funcionales. Ya sea que esté diseñando una interfaz de microcontrolador o un protocolo de comunicación de alta velocidad, la capacidad de leer y crear estos diagramas separa un diseño robusto de uno frágil. Al adoptar una perspectiva estructurada y modular, los equipos pueden gestionar la complejidad y reducir el riesgo de violaciones de tiempo.

Comprendiendo los fundamentos de los diagramas de tiempo ⏱️

Un diagrama de tiempo es una representación gráfica de cómo cambian de estado las señales con el paso del tiempo. Representa el tiempo en el eje horizontal y los estados de las señales en el eje vertical. Esta forma visual permite a los ingenieros verificar la relación entre diferentes señales dentro de un circuito digital. El objetivo principal es asegurar que los datos estén estables y válidos cuando son muestreados por el componente receptor.

Varios elementos clave forman la base de cualquier diagrama de tiempo:

- Líneas de señal:Las líneas horizontales representan cables individuales o buses que transportan señales específicas como reloj, datos o control.

- Eje del tiempo:La progresión horizontal indica el paso del tiempo, a menudo marcado en nanosegundos o ciclos de reloj.

- Niveles lógicos:Las señales suelen ser binarias, representadas como Alto (1) o Bajo (0). A veces también se muestran estados indefinidos o estados de alta impedancia.

- Transiciones:Las líneas verticales indican el momento en que una señal cambia de un estado a otro, como bordes de subida o bajada.

- Anotaciones:Las etiquetas de texto suelen definir restricciones específicas, retrasos o bloques funcionales dentro del diagrama.

Sin una comprensión clara de estos fundamentos, interpretar interacciones complejas se vuelve difícil. Un diagrama de tiempo no es meramente un dibujo; es un contrato entre el transmisor y el receptor. Establece las reglas según las cuales los datos deben viajar para ser procesados correctamente.

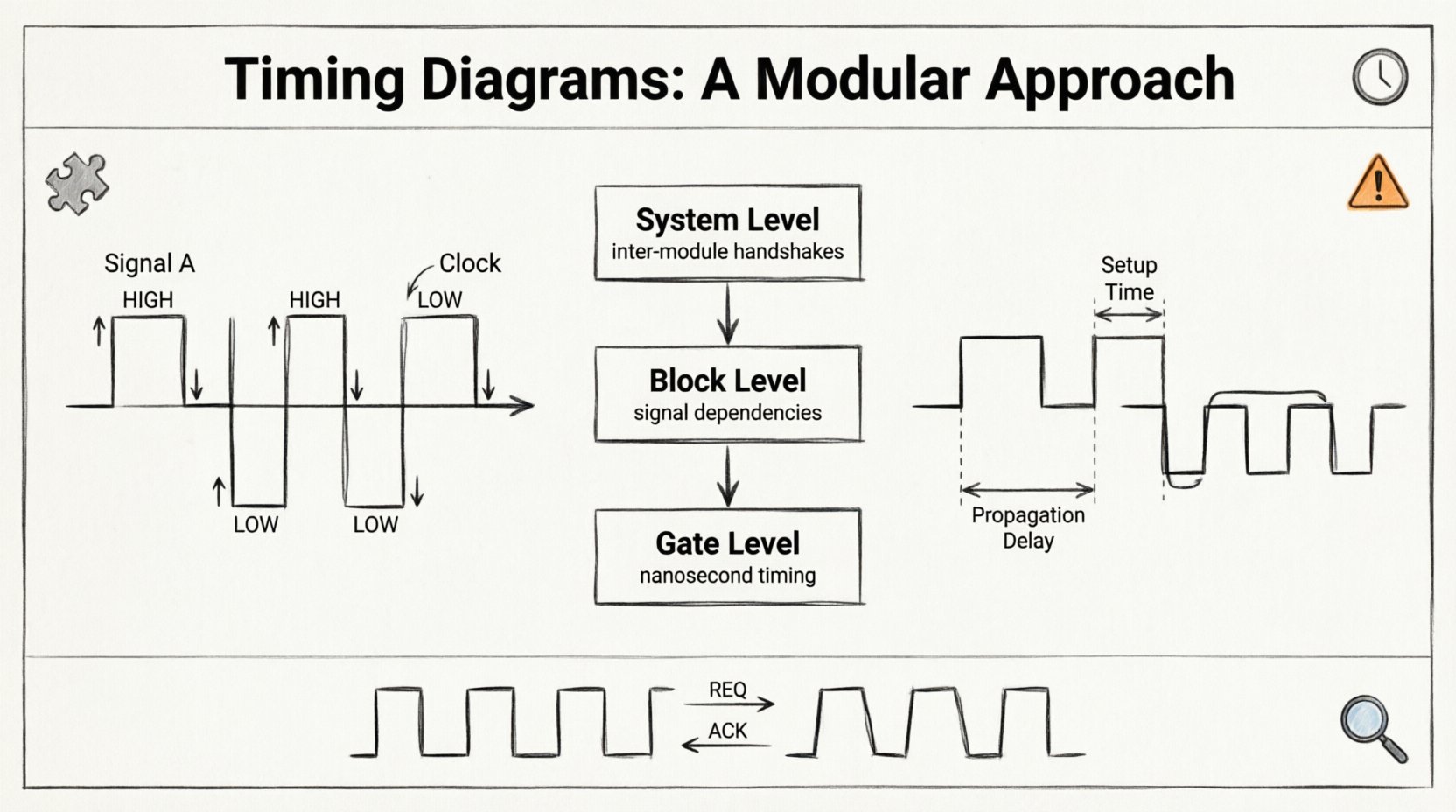

La estrategia modular para diseños complejos 🧩

Los sistemas digitales modernos rara vez son simples. Consisten en múltiples subsistemas, cada uno con sus propios requisitos de tiempo. Intentar dibujar todo el sistema en un solo diagrama suele llevar al desorden y la confusión. Un enfoque modular descompone el diseño en fragmentos manejables. Este método mejora la legibilidad y simplifica el proceso de depuración.

Por qué la modularidad importa

Dividir un sistema en módulos permite a los diseñadores centrarse en interfaces específicas sin perderse en el ruido de toda la arquitectura. Cuando ocurre una violación de tiempo, un diagrama modular facilita aislar la fuente del problema. Reduce la carga cognitiva y facilita la colaboración entre diferentes equipos de ingeniería que trabajan en bloques separados.

Los beneficios de este enfoque incluyen:

- Aislamiento de problemas:Los problemas pueden identificarse dentro de un bloque específico, en lugar de todo el sistema.

- Reutilización:Los patrones de tiempo estandarizados para módulos comunes pueden reutilizarse en diferentes proyectos.

- Escalabilidad:Nuevas funciones pueden añadirse como nuevos módulos sin tener que redibujar todo el diagrama.

- Eficiencia del equipo:Diferentes equipos pueden trabajar simultáneamente en sus respectivos diagramas de tiempo.

Definición de los límites del módulo

Para implementar esta estrategia de forma efectiva, deben establecerse límites claros. Cada módulo debe tener entradas y salidas definidas. El diagrama de temporización de un solo módulo debe centrarse en las señales que cruzan esa frontera. Los detalles internos pueden abstraerse, a menos que afecten directamente el tiempo de interfaz.

| Nivel de módulo | Área de enfoque | Grado de detalle |

|---|---|---|

| Nivel del sistema | Comunicación entre módulos | Saludos de alto nivel |

| Nivel de bloque | Rutas de datos internas | Dependencias específicas de señales |

| Nivel de puerta | Retardos de propagación | Temporalización exacta en nanosegundos |

Al organizar los diagramas según estos niveles, los ingenieros pueden mantener una jerarquía clara de la información. Esta estructura garantiza que el nivel adecuado de detalle esté disponible en la etapa adecuada del proceso de diseño.

Descifrando estados y transiciones de señales 📊

Una vez que la estructura modular está en su lugar, el siguiente paso es analizar las señales específicas. No todas las señales se comportan de la misma manera. Algunas son continuas, mientras que otras son disparadas por flancos. Comprender la naturaleza de cada señal es vital para la construcción precisa de los diagramas.

Las categorías comunes de señales incluyen:

- Señales de reloj: El latido del sistema. Son periódicas y provocan cambios de estado. Normalmente tienen requisitos estrictos de frecuencia y ciclo de trabajo.

- Señales de datos: La información real que se está transfiriendo. Deben permanecer estables durante ventanas específicas en relación con el reloj.

- Señales de control: Señales que habilitan o deshabilitan funcionalidades, como Chip Select o Enable.

- Señales de reinicio: Señales de inicialización que obligan al sistema a entrar en un estado conocido.

Las transiciones en estas líneas son críticas. Un flanco ascendente suele desencadenar una acción, mientras que un flanco descendente podría completarla. En sistemas asíncronos, la relación entre estos flancos es menos predecible, lo que requiere un análisis más detallado.

Visualización del retardo de propagación

Ninguna señal cambia instantáneamente. Las limitaciones físicas causan el retardo de propagación. Cuando una señal abandona un componente, tarda tiempo en viajar por el cable y llegar al siguiente componente. Los diagramas de temporización deben tener en cuenta esta latencia. Si un diagrama muestra que una señal cambia en el tiempo T, el extremo receptor podría no verlo hasta T + Δt.

Ignorar el retardo de propagación puede provocar errores significativos en la simulación y la implementación. Los ingenieros deben modelar estos retrasos para garantizar que se cumplan los tiempos de preparación y retención en toda la ruta.

Restricciones críticas de tiempo explicadas ⚠️

La causa más común de fallos en el diseño digital es la violación de tiempo. Estas violaciones ocurren cuando las señales no cumplen con las ventanas de estabilidad requeridas. Dos restricciones principales rigen este comportamiento: el tiempo de preparación y el tiempo de retención.

Tiempo de preparación

El tiempo de preparación es el tiempo mínimo durante el cual los datos deben permanecer estables antes del borde activo del reloj. Si los datos llegan demasiado tarde, el flip-flop podría no capturar el valor correcto. Esta restricción es crítica para determinar la frecuencia máxima de operación de un sistema. Si el período del reloj es más corto que la suma del retardo de propagación y el tiempo de preparación, el sistema fallará.

Las consideraciones clave para el tiempo de preparación incluyen:

- Se requiere un análisis de la ruta más larga para encontrar el peor caso posible.

- Las variaciones en el proceso, voltaje y temperatura afectan el retardo.

- El jitter del reloj puede reducir la ventana de tiempo de preparación disponible.

Tiempo de retención

El tiempo de retención es el tiempo mínimo durante el cual los datos deben permanecer estables después del borde activo del reloj. Si los datos cambian demasiado pronto, el flip-flop podría capturar un valor incorrecto o entrar en un estado metastable. A diferencia del tiempo de preparación, el tiempo de retención es independiente de la frecuencia del reloj. Depende del retardo interno del componente y de la ruta externa.

Las violaciones de tiempo de retención suelen ser más difíciles de corregir porque no se pueden resolver simplemente ralentizando el reloj. En su lugar, requieren agregar retardo en la ruta de datos o rediseñar la lógica.

Resumen de las restricciones de tiempo

| Restricción | Definición | Impacto en la frecuencia | Método de resolución |

|---|---|---|---|

| Tiempo de preparación | Estable antes del borde del reloj | Limita la frecuencia máxima | Optimizar la ruta lógica |

| Tiempo de retención | Estable después del borde del reloj | Independiente de la frecuencia | Agregar retardo de buffer |

| Retardo de propagación | Tiempo para viajar a través de la lógica | Afecta ambos | Optimización del circuito |

Errores comunes y violaciones 🚫

Incluso con un enfoque modular, los errores pueden aparecer. Reconocer los errores comunes ayuda a prevenirlos durante la fase de diseño. Varias tipos de violaciones se encuentran con frecuencia en la verificación de hardware.

- Metastabilidad: Ocurre cuando una señal cambia exactamente en el borde del reloj. La salida del flip-flop se vuelve impredecible. Esto es común al cruzar dominios de reloj.

- Glitches: Pulsos cortos e involuntarios causados por diferencias en las rutas lógicas. Estos pueden desencadenar cambios de estado falsos.

- Desviación de reloj: Cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Esto reduce la ventana de tiempo efectiva.

- Condiciones de carrera: Cuando el resultado depende de la secuencia de eventos, lo cual es impredecible en diseños asíncronos.

Resolver estos problemas requiere un análisis cuidadoso del diagrama de tiempos. Busque ventanas superpuestas donde la estabilidad no esté garantizada. Asegúrese de que las secuencias de reinicio se sigan correctamente para evitar estados indefinidos.

Implementando la metodología modular 🛠️

Para aplicar eficazmente esta metodología, siga una metodología estructurada. Esto garantiza que se cubra cada aspecto del tiempo sin redundancias.

- Defina interfaces: Liste claramente todas las entradas y salidas para cada módulo.

- Identifique dominios de reloj: Determine qué señales pertenecen a qué dominio de reloj.

- Mapa de rutas de datos: Rastree la ruta desde la fuente hasta el destino.

- Aplicar restricciones: Establezca los requisitos de setup y hold para cada flip-flop.

- Validar transiciones: Verifique la alineación de bordes y los anchos de pulso.

- Revisar integración: Asegúrese de que los diagramas de módulos se alineen al combinarse.

Cada paso se basa en el anterior. Saltar un paso puede provocar brechas en la cobertura. Por ejemplo, ignorar los dominios de reloj puede provocar fallas de sincronización que son difíciles de depurar más adelante.

Manejo de dominios de reloj múltiples 🌐

A medida que los diseños crecen, se vuelven necesarias múltiples frecuencias de reloj. Algunas partes del sistema funcionan rápido, mientras que otras funcionan lento. Sincronizar estos dominios es uno de los aspectos más desafiantes del análisis de tiempo.

Cuando las señales cruzan de un dominio de reloj a otro, el diagrama de tiempos debe reflejar la relación entre los dos relojes. Si los relojes son asíncronos, se necesita especial cuidado para prevenir la metastabilidad. Se utilizan técnicas como cadenas de sincronización o protocolos de intercambio de señales para gestionar esta transferencia de forma segura.

Las estrategias clave para diseños multi-reloj incluyen:

- Codificación de Gray: Usar códigos de Gray para transmitir contadores de múltiples bits de forma segura entre dominios.

- Búferes FIFO:Utilizando colas First-In-First-Out para desacoplar los relojes de lectura y escritura.

- Señales de handshake:Utilizando pares de solicitud/confirmación para garantizar la validez de los datos.

Los diagramas de tiempo para estas escenas deben mostrar explícitamente los bordes de reloj de ambos dominios. Esto permite a los ingenieros ver si los datos permanecen estables durante suficiente tiempo para que el reloj receptor los capture.

Depuración con datos visuales 🔍

Cuando un diseño falla, los diagramas de tiempo son el primer lugar al que hay que mirar. La depuración requiere paciencia y un enfoque sistemático. Comience aislando el módulo que falla. Compare el diagrama esperado con la forma de onda real.

Busque discrepancias en:

- Tiempo de señal respecto al reloj.

- Ancho de pulso de las señales de control.

- Transiciones de estado durante el reinicio.

- Glitches en las líneas de datos.

Las herramientas suelen ofrecer capacidades de acercamiento para inspeccionar detalles a nivel de nanosegundo. Utilice estas funciones para verificar el momento exacto en que ocurre una violación. Correlacione los datos visuales con la lógica para comprender la causa raíz.

Consideraciones finales sobre la integridad del diseño 💡

Los diagramas de tiempo son más que dibujos técnicos; son el plano maestro para sistemas digitales confiables. Al adoptar un enfoque modular, los ingenieros pueden gestionar la complejidad y mantener la claridad. Este método apoya la escalabilidad y reduce la probabilidad de errores costosos.

El éxito en el diseño de hardware depende de la atención al detalle. Cada nanosegundo cuenta. Cada transición importa. Al aplicar rigurosamente estos principios, los equipos pueden construir sistemas que funcionen de manera predecible en condiciones del mundo real. El análisis modular del tiempo garantiza que no se omita ningún detalle, lo que conduce a soluciones de hardware robustas y eficientes.

Es necesario un perfeccionamiento continuo de estas habilidades a medida que avanza la tecnología. Las nuevas normas y velocidades más rápidas requieren técnicas de análisis actualizadas. Manténgase informado sobre las mejores prácticas emergentes para mantener una ventaja competitiva en el campo de la ingeniería digital.