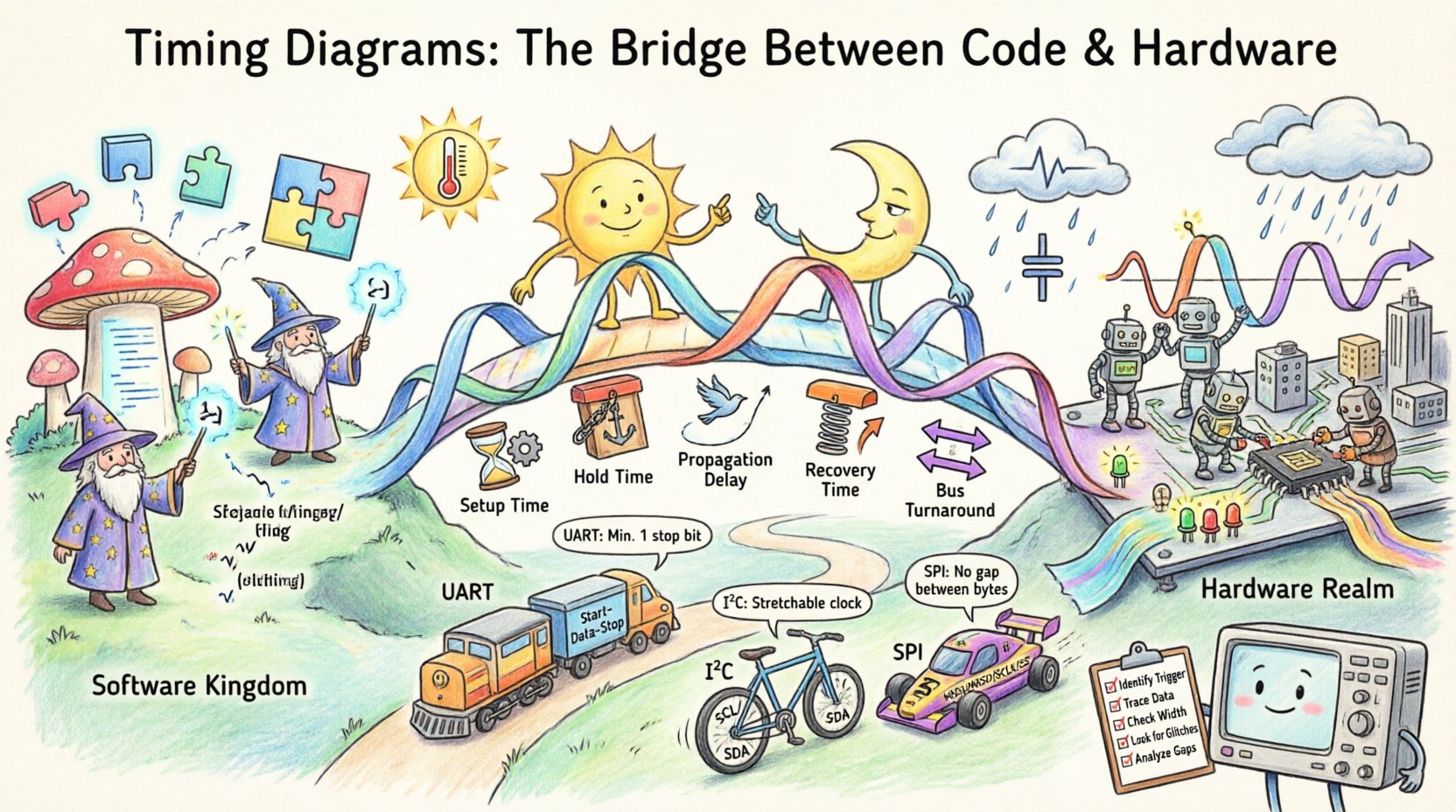

Cuando los ingenieros de software escriben código, piensan en instrucciones, variables y flujos lógicos. Cuando los ingenieros de hardware diseñan circuitos, piensan en niveles de voltaje, retardos de propagación y ciclos de reloj. Estos dos mundos a menudo existen en un estado de fricción. El código espera que una señal llegue en un momento lógico específico, pero el hardware opera en tiempo físico, que está sujeto a ruido, temperatura y resistencia eléctrica. El puente entre estos dos dominios es el diagrama de tiempo.

Un diagrama de tiempo no es meramente una imagen; es un contrato. Define la relación precisa entre eventos en el tiempo. Indica al firmware cuándo es seguro leer un pin y al silicio cuándo es seguro conducir una línea. Sin una comprensión clara de estos diagramas, los sistemas embebidos fallan de forma impredecible. La corrupción de datos, condiciones de carrera y colgamientos del sistema se convierten en problemas comunes. Esta guía explora la mecánica de los diagramas de tiempo, la física detrás de ellos y cómo leerlos y crearlos de forma efectiva.

📊 La anatomía de una señal

En esencia, la lógica digital depende de estados binarios. En el mundo físico, sin embargo, estos estados se representan mediante niveles de voltaje. Un «Alto» podría ser de 3,3 voltios, y un «Bajo» podría ser de 0 voltios. Pero las señales no cambian instantáneamente. Suben y bajan durante un período finito. Un diagrama de tiempo visualiza esta transición.

Comprender el lenguaje visual de estos diagramas es el primer paso hacia la maestría. Los elementos clave incluyen:

- Eje del tiempo:Generalmente horizontal, que avanza de izquierda a derecha. Puede ser lineal o logarítmico, aunque lo lineal es estándar para la mayoría del análisis lógico.

- Líneas de señal:Líneas verticales que representan cables específicos, pines o nodos internos.

- Transiciones:El movimiento de Bajo a Alto (borde ascendente) o de Alto a Bajo (borde descendente). Estos bordes a menudo desencadenan cambios de estado en la lógica secuencial.

- Niveles:El estado estable de una señal antes o después de una transición.

- Etiquetas:Anotaciones de texto que aclaran el significado de un pulso o intervalo específico.

Considere una señal de reloj simple. Oscila entre Alto y Bajo. El tiempo que tarda en completar un ciclo completo es el período. La inversa del período es la frecuencia. En un diagrama de tiempo, el reloj actúa como el latido del sistema. Cada una de las otras señales suele estar sincronizada con estos bordes.

🕰️ El dominio del reloj

La mayoría de los sistemas digitales operan dentro de un dominio de reloj. Este es un grupo de circuitos que comparten la misma referencia de tiempo. Sin embargo, las señales a menudo cruzan entre dominios diferentes. Esto introduce complejidad. Una señal generada en un dominio rápido podría llegar demasiado tarde para un dominio lento, o demasiado temprano, causando una violación de retención.

Al analizar el tiempo, debes considerar:

- Desviación del reloj:La diferencia en el tiempo de llegada de la señal de reloj en diferentes componentes. Si el reloj llega al emisor antes que al receptor, los márgenes de tiempo se reducen.

- Desfase:En algunos sistemas, las señales no están alineadas con el borde del reloj, sino que ocurren en medio del ciclo.

- Jitter:Variaciones en el tiempo de una señal. El jitter puede ser aleatorio o determinista. Reduce el margen de ruido y hace que el diagrama sea menos predecible.

El código escrito para interactuar con el hardware asume un reloj estable. Si el reloj físico se desvía debido a fluctuaciones de temperatura o voltaje, el diagrama de tiempo ya no coincide con la realidad. Por eso los diagramas de tiempo deben incluir bandas de tolerancia o escenarios de peor caso.

⚙️ Parámetros críticos de tiempo

Parámetros específicos definen los límites de la integridad de la señal. Estos valores a menudo se encuentran en las hojas de datos, pero se entienden mejor en el contexto de un diagrama de tiempo. La siguiente tabla enumera los parámetros más críticos que los ingenieros deben evaluar.

| Parámetro | Definición | Impacto en el sistema |

|---|---|---|

| Tiempo de preparación | El tiempo mínimo durante el cual los datos deben permanecer establesantes de el borde de reloj. | Si se viola, el flip-flop receptor no puede capturar el valor correcto. |

| Tiempo de retención | El tiempo mínimo durante el cual los datos deben permanecer establesdespués de el borde de reloj. | Si se viola, el flip-flop puede entrar en un estado metastable. |

| Retardo de propagación | Tiempo que tarda una señal en viajar desde la entrada hasta la salida. | Los retardos se acumulan a través de las puertas lógicas, posiblemente haciendo perder ciclos de reloj. |

| Tiempo de recuperación | Tiempo necesario para que una señal de control vuelva a su estado normal después de un evento asíncrono. | Afecta la rapidez con la que el sistema se recupera de reinicios o interrupciones. |

| Tiempo de cambio de sentido del bus | Tiempo necesario para cambiar un bus del modo de salida al modo de entrada. | Crucial para buses bidireccionales como I2C o 1-Wire. |

Violaciones de estos parámetros no siempre causan un fallo inmediato. A veces el sistema funciona el 99% de las veces y falla solo bajo condiciones específicas. Es por eso que el análisis de tiempos es un proceso iterativo. Debes verificar que el diagrama sea válido bajo condiciones extremas de voltaje y temperatura.

👀 Leyendo la forma de onda

Leer un diagrama de tiempos requiere un enfoque sistemático. Al depurar un problema de hardware, no mires solo los niveles de señal. Observa las relaciones entre las señales.

Sigue estos pasos para analizar una forma de onda:

- Identifica el disparador:Encuentra el evento que inicia la secuencia. Esto suele ser un borde de reloj o una interrupción externa.

- Rastrea los datos:Sigue las líneas de datos respecto al disparador. ¿Los datos aparecen antes o después del borde de reloj?

- Verifica la anchura Mida la duración de los pulsos. ¿Es suficientemente largo una señal de «Alto» para ser reconocida por la lógica receptora?

- Busque los parpadeos:Pulsos espurios que ocurren entre estados estables. Pueden ser causados por crosstalk o riesgos lógicos.

- Analice el espacio:Observe el tiempo entre el final de una transacción y el inicio de la siguiente. ¿Hay suficiente tiempo para que el hardware se reinicie?

A menudo, el problema radica en el espacio. Si un microcontrolador termina de escribir datos en un periférico, podría necesitar una demora específica antes de enviar el siguiente byte. Si el diagrama muestra estos bytes uno tras otro sin espacio, es probable que el código sea demasiado agresivo para el hardware.

🔌 Protocolos comunes y temporización

Diferentes protocolos de comunicación imponen diferentes restricciones de temporización. Comprender estas restricciones es esencial para escribir firmware que se comunique de forma confiable.

| Protocolo | Característica clave de temporización | Modo común de fallo |

|---|---|---|

| UART | Bit de inicio seguido por bits de datos y bit de parada. Depende de la tasa de baudios. | Errores de bit debido al desplazamiento de reloj entre el emisor y el receptor. |

| I2C | Líneas SCL y SDA. Requiere resistencias de tirar hacia arriba. SDA debe ser estable durante el estado alto de SCL. | Problemas de retención de bus o estiramiento de reloj que causan tiempos de espera. |

| SPI | Las líneas de reloj y datos son separadas. Disparadas por flanco (configuraciones CPOL/CPHA). | Los esclavos respondiendo demasiado lentamente para la velocidad del reloj maestro. |

| Interrupciones de GPIO | Sensibilidad al flanco. Requiere tiempo mínimo de procesamiento en la rutina de servicio de interrupción. | Interrupciones perdidas debido a la larga ejecución de rutinas de servicio previas. |

Por ejemplo, en SPI, la temporización del flanco del reloj respecto a la línea de datos determina si los datos se capturan en el flanco ascendente o descendente. Si el firmware asume un modo y el hardware está configurado para el otro, los datos se leerán incorrectamente. Un diagrama de temporización aclara esta relación visualmente, evitando errores de configuración.

🔍 Depuración de problemas con temporización

Cuando un sistema se comporta de forma errática, la primera herramienta que debe usarse no es un depurador, sino un diagrama de temporización. Depurar con temporización implica capturar el comportamiento eléctrico real y compararlo con el diseño esperado.

Los problemas comunes relacionados con la temporización incluyen:

- Metastabilidad:Cuando una señal llega a un flip-flop demasiado cerca del borde del reloj, la salida se vuelve impredecible. Puede estabilizarse en Alto, Bajo o permanecer en un estado intermedio durante un tiempo indeterminado.

- Condiciones de carrera: Cuando el resultado depende del tiempo relativo de los eventos. Si dos señales cambian simultáneamente, el orden de procesamiento importa.

- Integridad de señal: Las reflexiones y el rebote en trazados largos pueden causar transiciones falsas. El diagrama puede mostrar oscilaciones donde debería haber una onda cuadrada limpia.

- Violaciones de setup/hold: Los datos cambian demasiado cerca del borde del reloj. Esto suele deberse a que la velocidad del reloj es demasiado alta para la ruta lógica.

Para resolver estos problemas, es posible que deba agregar retardos en el código, cambiar la frecuencia del reloj o ajustar la disposición del hardware. El diagrama de tiempos proporciona la evidencia necesaria para realizar estos cambios con confianza.

📝 Mejores prácticas para la documentación

Crear diagramas de tiempo para la documentación es tan importante como leerlos. Una documentación deficiente del tiempo conduce a pesadillas de mantenimiento. Los ingenieros futuros tendrán dificultades para entender por qué se agregó un retardo específico en el código.

Siga estas pautas al crear sus propios diagramas:

- Use símbolos estándar:Evite íconos personalizados a menos que estén definidos en una leyenda. Use la notación estándar de borde ascendente/bajada.

- Etiquete todo:No asuma que el lector sabe lo que representa cada línea. Etiquete claramente pines, señales y estados.

- Incluya contexto:Muestre el estado de las señales de control (como Chip Select o Enable) junto con las líneas de datos.

- Especifique unidades:Indique siempre la escala de tiempo. ¿Es microsegundos, nanosegundos o ciclos de reloj?

- Resalte las rutas críticas:Use líneas en negrita o colores diferentes para resaltar las señales que determinan la estabilidad del sistema.

- Control de versiones:Actualice los diagramas cuando cambie el hardware o el firmware. Un diagrama desactualizado es una carga.

La documentación no debe mostrar solo el «camino feliz». También debe mostrar los estados de error. ¿Cómo se ve el diagrama cuando ocurre un tiempo de espera? ¿Cómo se ve cuando se activa un reinicio? Estos escenarios son a menudo donde se esconden los mayores errores.

🌡️ Factores ambientales

Un diagrama de tiempo a menudo se genera bajo condiciones de laboratorio ideales. Los entornos del mundo real rara vez son ideales. La temperatura, el voltaje y la interferencia electromagnética afectan todos la propagación de la señal.

Considere los siguientes factores:

- Temperatura:El rendimiento del silicio se degrada a altas temperaturas. El retardo de propagación aumenta. Un sistema que funciona a 25 °C podría fallar a 85 °C.

- Voltaje:Un voltaje de alimentación más bajo aumenta el retardo. Un voltaje más alto podría reducir el retardo, pero aumenta el consumo de potencia y el calor.

- Capacitancia de carga:Los cables largos añaden capacitancia. Esto ralentiza los tiempos de subida y bajada de las señales, ampliando efectivamente la anchura del pulso pero ralentizando la transición.

Un diseño robusto tiene en cuenta estas variaciones. Al crear un diagrama de temporización para producción, considere la esquina de ‘peor caso’. Esto significa que el diagrama representa las transiciones de señal más lentas posibles y los bordes de reloj más rápidos posibles. Si el sistema funciona bajo estas condiciones, funcionará en la mayoría de los casos.

🛠️ Creación y validación de diagramas

Aunque el dibujo manual es posible, la ingeniería moderna depende de herramientas automatizadas para capturar y validar el tiempo. Sin embargo, los principios permanecen iguales sin importar la herramienta utilizada. El objetivo es visualizar el flujo del tiempo.

Al validar un diagrama:

- Compare con las hojas de datos:Asegúrese de que los valores de temporización en su diagrama coincidan con las especificaciones del fabricante para los chips utilizados.

- Ejecute simulaciones:Utilice entornos de simulación para modelar la lógica antes de construir el circuito físico.

- Mida el hardware real:Nada reemplaza la medición real. Capture las formas de onda de la placa física y superponlas sobre el diagrama de diseño.

- Verifique los márgenes:¿Hay suficiente tiempo de holgura entre las señales? Si el margen es cero, cualquier variación causará un fallo.

La validación es un proceso continuo. A medida que evoluciona el firmware, los requisitos de temporización pueden cambiar. Un nuevo manejador de interrupciones podría introducir una demora que empuje una señal más allá de su plazo. La verificación continua asegura que el puente entre el código y el hardware permanezca sólido.

🔗 La intersección de la lógica y la física

En última instancia, un diagrama de temporización representa la intersección de la lógica y la física. La lógica dicta lo que debería ocurrir; la física dicta lo que realmente ocurre. El trabajo del ingeniero consiste en alinear estas dos realidades.

Al dominar la interpretación y creación de estos diagramas, adquiere la capacidad de diagnosticar fallas complejas que otros podrían pasar por alto. Deja de adivinar por qué el sistema se queda colgado y empieza a ver exactamente dónde se violó la restricción de temporización. Este nivel de comprensión transforma a un desarrollador en un diseñador.

Ya sea que esté diseñando una interfaz de sensor simple o un bus de comunicación de alta velocidad, el diagrama de temporización es su referencia principal. Asegura que el código que escribe se ejecute en el tiempo que espera el hardware. Asegura que las señales que ve en la pantalla coincidan con los voltajes en los pines. Es el lenguaje de la sincronización.

Invierta tiempo en comprender estos diagramas. Trátelos con la misma seriedad que el código mismo. En los sistemas embebidos, el tiempo no es solo un detalle; es la base de la fiabilidad. Cuando el código y el hardware hablan el mismo idioma del tiempo, el sistema funciona con precisión y estabilidad.