Dans le monde de l’électronique numérique et du génie informatique, les signaux n’existent pas dans le vide. Ils voyagent à travers des pistes, à travers des portes logiques, puis dans les processeurs, avec des contraintes temporelles spécifiques. Pour comprendre le fonctionnement d’un système, les ingénieurs doivent visualiser comment ces signaux évoluent dans le temps. Cette visualisation est réalisée à l’aide d’un diagramme de timing. Pour un débutant, ces graphiques peuvent sembler des hiéroglyphes complexes, mais ils sont en réalité l’outil le plus fondamental pour le débogage et la conception de logique numérique.

Ce guide fournit une analyse approfondie des diagrammes de timing. Nous explorerons l’anatomie d’un signal, les paramètres critiques qui définissent la fiabilité, et les pièges courants qui mènent à l’échec du système. Que vous étudiiez pour un examen ou que vous conceviez votre premier circuit microcontrôleur, comprendre ces diagrammes est essentiel.

🧠 Qu’est-ce qu’un diagramme de timing ?

Un diagramme de timing est une représentation graphique de l’état des signaux numériques au fil du temps. Contrairement à un schéma de circuit, qui montrece quiest connecté àce qui, un diagramme de timing montrequandles choses se produisent. Il représente les niveaux de tension en fonction d’un axe temporel, permettant aux ingénieurs de voir la séquence des événements.

Ces diagrammes sont indispensables pour plusieurs raisons :

- Débogage : Ils révèlent les conditions de course où les signaux arrivent hors séquence.

- Vérification : Ils confirment qu’un circuit respecte les spécifications de vitesse requises.

- Documentation : Ils servent de référence pour la communication entre différents circuits intégrés.

- Conception : Ils aident à déterminer la fréquence d’horloge maximale qu’un système peut supporter.

Quand vous regardez un diagramme de timing, vous observez un instantané du comportement physique des électrons se déplaçant à travers un système. Il capte la réalité de la latence, de la propagation et de la synchronisation.

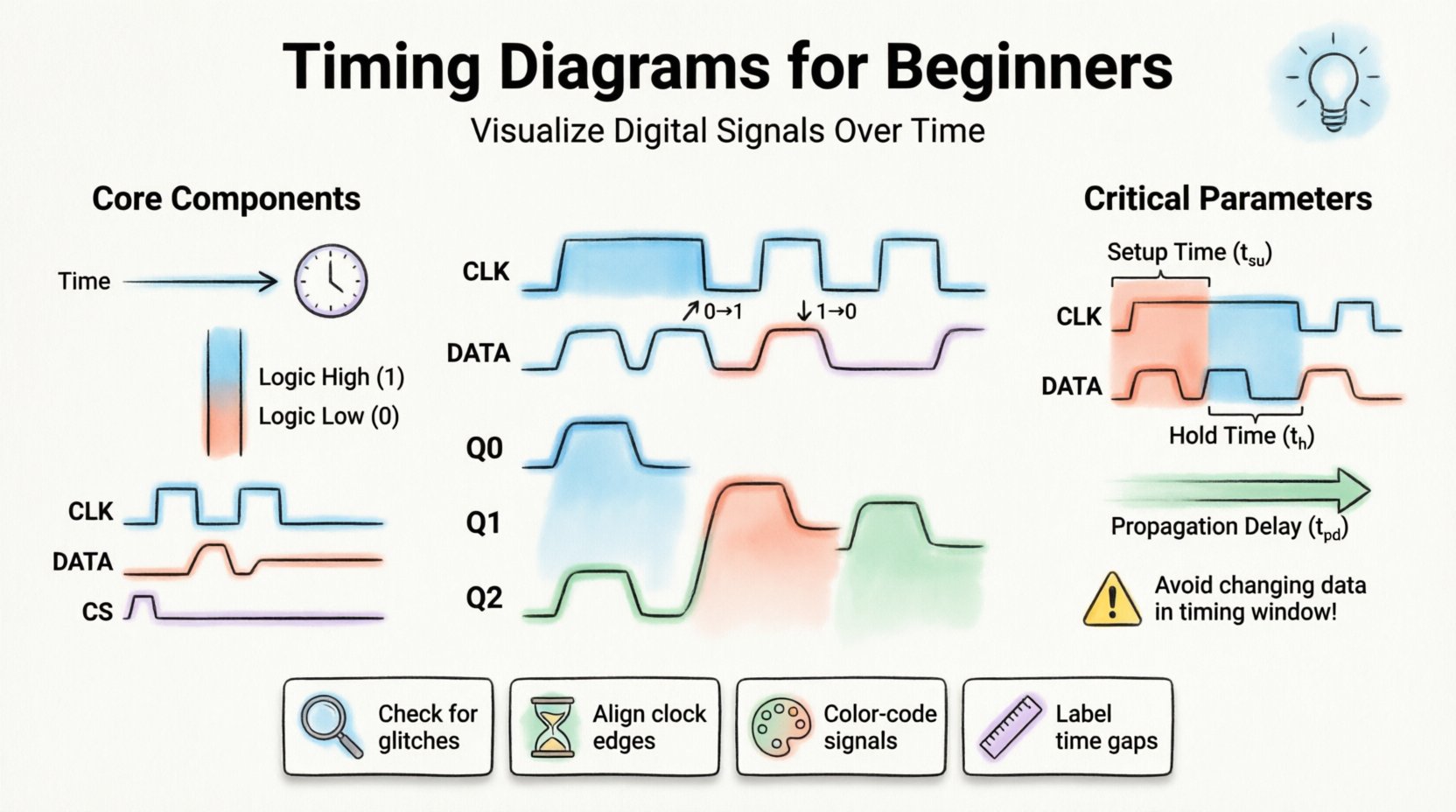

📊 Composants fondamentaux d’un diagramme de timing

Avant d’analyser des formes d’onde complexes, vous devez comprendre les éléments de base. Chaque diagramme de timing se compose de quelques éléments fondamentaux.

1. L’axe du temps

L’axe horizontal représente le temps. Il s’écoule de gauche à droite. En conception numérique, cet axe est souvent divisé en cycles d’horloge, marqués par des lignes verticales de grille. L’échelle peut varier de nanosecondes (ns) pour les processeurs à haute vitesse à millisecondes (ms) pour la logique de contrôle plus lente.

2. L’axe des niveaux de tension

L’axe vertical représente l’état logique du signal. Dans les familles logiques standards, il s’agit généralement d’une représentation binaire :

- État logique haut (1) :Souvent représenté par VCC ou 5V.

- État logique bas (0) : Souvent représenté comme la masse ou 0V.

- Haut-Z (Haut impédance) : Un état où la broche est effectivement déconnectée, courant dans les systèmes de bus.

3. Lignes de signal

Chaque ligne horizontale représente un fil spécifique ou un nom de signal. Ces lignes sont clairement étiquetées (par exemple, CLK, DATA_IN, CS) pour identifier quelle partie du circuit est surveillée.

🔄 Lecture des transitions de signal

Le mouvement de la ligne de signal vers le haut et vers le bas est là où se trouve les données. Comprendre la direction de ces mouvements est essentiel.

⬆️ Front montant

Un front montant se produit lorsque le signal passe de bas à haut. En logique binaire, c’est souvent le point de déclenchement de nombreuses opérations. Il représente un changement de 0 à 1.

⬇️ Front descendant

Un front descendant se produit lorsque le signal passe de haut à bas. Cela représente un changement de 1 à 0.

⚡ Déclenchement sur front

Beaucoup de composants numériques, tels que les bascules, ne réagissent qu’à ces fronts plutôt qu’à l’état stable. Une bascule peut capturer les données uniquement sur le front montantdu signal d’horloge. Si vous manquez le front, les données sont perdues.

| Transition | Direction | Changement binaire | Type de déclenchement courant |

|---|---|---|---|

| Front montant | Bas ➔ Haut | 0 ➔ 1 | Déclenchement sur front positif |

| Front descendant | Haut ➔ Bas | 1 ➔ 0 | Déclenchement sur front négatif |

| Niveau haut | Stable haut | Stable 1 | Sensible au niveau |

| Niveau bas | Stable bas | Stable 0 | Sensible au niveau |

⏳ Paramètres de temporisation critiques

Les diagrammes de temporisation ne sont pas seulement des images ; ils contiennent des mesures. L’espace entre les changements de signal est là où la fiabilité est déterminée. Trois paramètres spécifiques dominent l’analyse de temporisation numérique.

1. Retard de propagation (tpd)

Les signaux ne se propagent pas instantanément. Lorsqu’une entrée change, il faut un temps fini pour que la sortie reflète ce changement. C’est le retard de propagation. Il est causé par la résistance physique et la capacité des matériaux.

- Définition : La différence de temps entre le changement d’entrée et le changement de sortie.

- Impact : Dans une chaîne de portes logiques, les retards s’accumulent. Si le retard est trop long, le signal pourrait arriver après le début du cycle d’horloge suivant, provoquant des erreurs.

2. Temps de préparation (tsu)

Le temps de préparation est la condition pour qu’un signal de données soit stableavant l’arrivée d’un front d’horloge. Si les données changent trop près du front d’horloge, le circuit récepteur ne peut pas les capturer correctement.

- Règle : Les données doivent être valides pendant une durée spécifique avant que l’horloge ne déclenche.

- Visuel : Sur un diagramme, il s’agit de l’écart entre la stabilisation de la ligne de données et le front d’horloge.

3. Temps de maintien (th)

Le temps de maintien est la condition pour que le signal de données reste stableaprès L’arête de l’horloge arrive. Si les données changent immédiatement après l’arête de l’horloge, le circuit pourrait ne pas capturer la bonne valeur.

- Règle : Les données doivent rester inchangées pendant une durée spécifique après le déclenchement de l’horloge.

- Visuel : Sur un schéma, il s’agit de l’écart entre l’arête de l’horloge et la prochaine transition des données.

⚠️ La fenêtre de temporisation

La combinaison du temps de préparation et du temps de maintien crée une fenêtre valide pour la capture des données. Si votre diagramme de temporisation montre les données qui changent dans cette fenêtre, le système est en danger de défaillance.

⚡ Systèmes synchrones vs. asynchrones

Les diagrammes de temporisation diffèrent considérablement selon l’architecture du système.

Systèmes synchrones

Dans la conception synchrone, toutes les opérations sont coordonnées par un signal d’horloge global. Chaque changement d’état a lieu sur l’arête de cette horloge. Les diagrammes de temporisation de ces systèmes ont un aspect très régulier.

- Caractéristiques :Prévisible, plus facile à concevoir, limité par la vitesse de l’horloge.

- Apparence du schéma :Les lignes verticales de la grille s’alignent parfaitement avec tous les changements de signal.

Systèmes asynchrones

Dans la conception asynchrone, il n’y a pas d’horloge globale. Les signaux changent dès que les entrées changent. Cela offre un potentiel de vitesse plus élevé, mais rend l’analyse de temporisation beaucoup plus difficile.

- Caractéristiques :Réponse plus rapide aux entrées, analyse de danger complexe.

- Apparence du schéma : Les transitions de signal se produisent à des intervalles irréguliers. Vous devez mesurer les écarts de temps exacts entre les événements.

📝 Comment dessiner un diagramme de temporisation

La création d’un diagramme de temporisation est un processus systématique. Suivez ces étapes pour documenter un circuit ou vérifier une conception.

- Identifier les signaux : Liste toutes les entrées, sorties et lignes de contrôle internes. Les étiquetez clairement.

- Établir l’échelle de temps : Déterminez l’échelle de temps. Pour les circuits logiques, les cycles d’horloge sont généralement l’unité de référence.

- Tracer l’horloge : Dessinez toujours le signal d’horloge en premier. Il sert de référence à tous les autres événements.

- Cartographier les entrées Dessinez les signaux d’entrée en fonction de l’opération logique ou de la séquence de test.

- Calculez les délais : Déplacez les signaux de sortie vers la droite en fonction du délai de propagation des portes impliquées.

- Vérifiez les contraintes : Vérifiez que les temps de setup et de hold sont respectés pour chaque bascule.

- Revoyez les transitions : Assurez-vous qu’il n’y ait pas de glitch. Un glitch est une impulsion brève et involontaire qui peut déclencher la logique de manière incorrecte.

🔄 Exemple du monde réel : un compteur simple

Pour visualiser comment ces concepts fonctionnent ensemble, envisagez un simple compteur binaire à 3 bits. Ce circuit augmente sa valeur chaque fois que le signal d’horloge pulse.

Imaginez trois lignes de sortie : Q0, Q1 et Q2. Q0 bascule à chaque cycle d’horloge. Q1 bascule chaque fois que Q0 effectue un cycle complet. Q2 bascule chaque fois que Q1 effectue un cycle complet.

Analyse étape par étape

- Horloge (CLK) : Une onde carrée avec un rapport cyclique de 50 %.

- Q0 (bit de poids faible) : Change d’état à chaque front montant de l’horloge. La fréquence est la moitié de celle de l’horloge.

- Q1 : Change d’état à chaque front montant de Q0. La fréquence est la moitié de celle de Q0.

- Q2 (bit de poids fort) : Change d’état à chaque front montant de Q1. La fréquence est la moitié de celle de Q1.

En dessinant cela, vous remarquerez un effet d’ondulation. Q0 change en premier. Q1 attend que Q0 se stabilise avant de changer. Q2 attend que Q1 se stabilise. Cette accumulation de délais est l’essence d’un compteur à propagation.

| Cycle d’horloge | Q2 | Q1 | Q0 | Valeur décimale |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ Erreurs courantes à éviter

Même les ingénieurs expérimentés peuvent commettre des erreurs en lisant les diagrammes de temporisation. Soyez attentif à ces erreurs courantes.

- Ignorer les parasites :Une impulsion brève peut ne pas être visible si l’échelle de temps est trop grande, mais elle peut déclencher une bascule. Vérifiez toujours la présence d’impulsions étroites.

- Mauvaise interprétation du rapport cyclique :Supposer qu’une horloge est à 50 % alors qu’elle est en réalité décalée. Cela affecte la fenêtre de temporisation.

- Ne pas tenir compte des états haute impédance :Dans les systèmes de bus, les lignes sont flottantes. Un diagramme de temporisation doit indiquer quand une ligne est activée et quand elle est en état flottant.

- Confondre setup et hold :Le setup est avant l’arête ; le hold est après. Confondre ces deux notions conduit à des conceptions de circuits incorrectes.

- Omettre la référence de masse :Tous les niveaux de tension doivent être mesurés par rapport au même point de masse. Si les masses diffèrent, les niveaux logiques sont invalides.

🛠 Meilleures pratiques pour la documentation

Lors de la création de diagrammes de timing pour la documentation ou le débogage, suivez ces recommandations pour assurer une clarté optimale.

- Utiliser un échelonnage cohérent :Assurez-vous que l’axe des temps est linéaire. Ne compressez pas une section et étirez une autre sauf si cela est explicitement indiqué.

- Aligner les bords critiques :Assurez-vous que le bord de l’horloge est parfaitement aligné avec le point d’échantillonnage des données.

- Marquer les intervalles : Si une attente existe, marquez-la avec la valeur de temps spécifique (par exemple, tpd = 5 ns).

- Codage par couleur : Utilisez des couleurs distinctes pour les différents types de signaux (par exemple, bleu pour l’horloge, rouge pour les données, vert pour le contrôle).

- Indiquer les états actifs : Indiquez clairement si un signal est actif à haut ou actif à bas (par exemple, en utilisant une barre au-dessus du nom comme /CS).

🧩 Métastabilité et risques de timing

Les diagrammes de timing avancés révèlent souvent un phénomène appelé métastabilité. Cela se produit lorsque le signal change exactement dans la fenêtre de setup/hold d’une bascule. La sortie ne se stabilise pas immédiatement à 0 ou à 1 ; elle reste à un niveau de tension intermédiaire.

Bien que rare, la métastabilité peut provoquer des plantages du système. Les diagrammes de timing aident à la prédire en montrant la relation entre les entrées asynchrones et l’horloge synchrone. Si un signal externe change trop près de l’arête de l’horloge, le diagramme montrera les données franchissant la seuil au mauvais moment.

🔍 Analyse des données réelles

Lorsque vous examinez un diagramme de timing généré par un analyseur logique, les lignes sont rarement des carrés parfaits. Les signaux du monde réel présentent :

- Temps de montée : Le temps nécessaire pour passer de bas à haut. Il est rarement instantané.

- Temps de descente : Le temps nécessaire pour passer de haut à bas.

- Surtension / Sous-tension : Pic de tension dépassant les rails d’alimentation.

- Jitter : Variations dans le timing des fronts du signal.

Comprendre ces imperfections est essentiel pour la conception à haute vitesse. Une onde carrée parfaite est un idéal théorique ; les signaux réels sont des formes d’onde analogiques qui représentent la logique numérique.

📚 Résumé des points clés

Les diagrammes de temporisation sont le langage du temporisation numérique. Ils traduisent la logique abstraite en réalité physique. En maîtrisant ces diagrammes, vous acquérez la capacité de :

- Visualiser le flux de données à travers un système.

- Identifier où les signaux pourraient entrer en conflit.

- Assurer que les données sont capturées de manière fiable.

- Calculer la vitesse maximale de fonctionnement d’un circuit.

Commencez par pratiquer avec des portes logiques simples. Dessinez l’entrée, calculez le délai et tracez la sortie. Au fur et à mesure que vous progressez, passez aux bus complexes et aux domaines d’horloge. Avec de la patience et de la pratique, la lecture de ces diagrammes deviendra naturelle.

🚀 En avant

Poursuivez l’exploration des subtilités de l’intégrité du signal et des réseaux de distribution d’horloge. À mesure que les systèmes deviennent plus rapides, les marges de temporisation se réduisent. La capacité à lire un diagramme de temporisation avec précision restera une compétence fondamentale pour tout ingénieur travaillant sur des matériels numériques.