Comprendre le comportement des circuits numériques exige plus que la simple connaissance des portes logiques. Cela demande une maîtrise de la manière dont les signaux évoluent dans le temps. Les diagrammes de temporisation fournissent le langage visuel pour cette analyse temporelle. Ils représentent l’état de divers signaux par rapport à une horloge ou à un événement spécifique. Pour les étudiants en informatique, maîtriser ce concept est essentiel pour concevoir des systèmes fiables.

Ce guide explore les mécanismes, les techniques de lecture et les paramètres critiques impliqués dans les diagrammes de temporisation. Nous aborderons tout, des transitions de signal de base aux violations complexes de temps de préparation et de maintien. À la fin de cet aperçu, vous aurez une solide base pour analyser les interactions numériques.

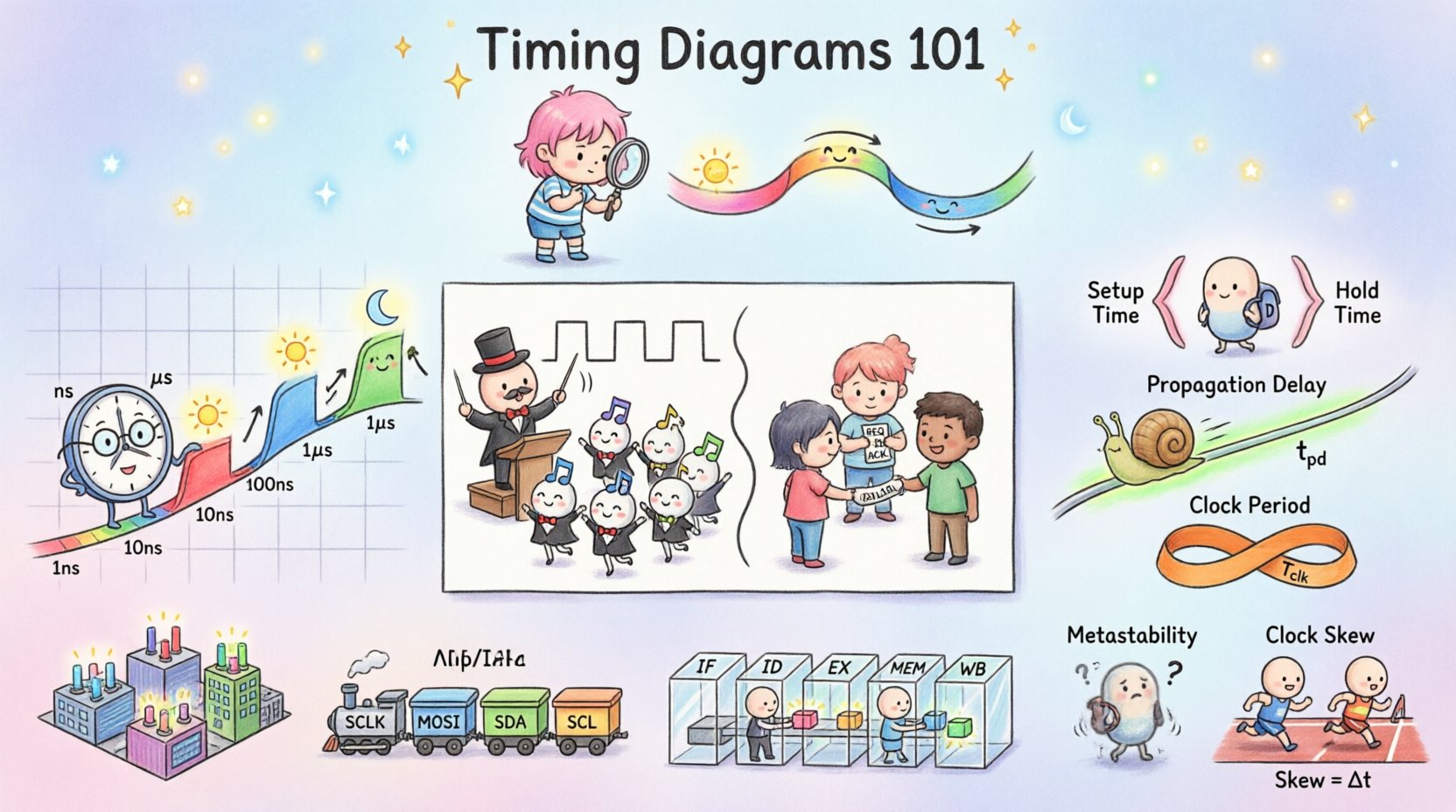

Qu’est-ce qu’un diagramme de temporisation ? ⏱️

Un diagramme de temporisation est une représentation graphique de la relation entre deux ou plusieurs signaux au fil du temps. Il agit comme une chronologie pour les événements numériques. Chaque signal est tracé sous forme de ligne horizontale. La position verticale indique le niveau logique ou l’état. L’axe horizontal représente l’écoulement du temps.

Ces diagrammes sont essentiels pour vérifier qu’un système numérique fonctionne correctement. Ils aident les ingénieurs à prédire la manière dont les données circulent à travers les registres, les bus et la mémoire. Sans eux, le débogage des problèmes matériels devient presque impossible. Ils combler le fossé entre la logique abstraite et la réalité physique.

Composants fondamentaux des signaux numériques 📡

Avant de plonger dans les diagrammes, il faut comprendre les signaux eux-mêmes. Les systèmes numériques reposent sur des niveaux de tension pour représenter des données binaires. Ces niveaux ne sont pas toujours statiques ; ils passent d’un état à un autre.

- Niveau logique haut (1) : Représente généralement une tension proche du rail d’alimentation.

- Niveau logique bas (0) : Représente généralement une tension proche de la masse.

- Bords : Les points de transition entre haut et bas. Les fronts montants passent du bas au haut. Les fronts descendants passent du haut au bas.

- État stable : La période pendant laquelle un signal reste constant.

- Marges de bruit : La tolérance qu’un signal possède avant d’être mal interprété.

Les diagrammes de temporisation visualisent ces transitions. Ils montrent exactement quand un signal change et combien de temps il reste dans cet état. Cette précision est cruciale pour assurer l’intégrité des données.

Comprendre l’axe du temps ⏳

L’axe horizontal est la charpente de tout diagramme de temporisation. Il représente l’évolution du temps. En conception numérique, cet axe est souvent synchronisé avec un signal d’horloge. L’horloge agit comme le battement du cœur du système.

Les unités sur l’axe du temps varient en fonction de la vitesse du circuit. Les unités courantes incluent :

- Secondes (s) : Utilisées pour les systèmes très lents.

- Millisecondes (ms) : 10^-3 secondes.

- Microsecondes (µs) : 10^-6 secondes.

- Nanosecondes (ns) : 10^-9 secondes. Standard pour les processeurs modernes.

- Picosecondes (ps) : 10^-12 secondes. Nécessaire pour les interfaces à haute vitesse.

Lors de la lecture d’un schéma, recherchez les repères d’échelle. Ils indiquent la durée de chaque cycle. Cela aide à calculer les délais de propagation et à garantir que les signaux arrivent dans la fenêtre requise.

Systèmes synchrones vs asynchrones 🔄

Les systèmes numériques se divisent généralement en deux catégories selon la manière dont ils gèrent le temps. Comprendre cette distinction est essentiel pour tracer des schémas précis.

1. Systèmes synchrones

Dans les conceptions synchrones, tous les changements d’état se produisent par rapport à un signal d’horloge global. Le diagramme de temporisation affichera une onde d’horloge périodique. Chaque bascule se met à jour sur le front actif de cette horloge.

- Avantages : Comportement prévisible. Plus facile à vérifier.

- Défis : Le décalage d’horloge peut poser des problèmes si les signaux arrivent à des moments différents.

- Caractéristique du schéma : Des lignes verticales s’alignent souvent avec les fronts d’horloge pour indiquer les moments de capture.

2. Systèmes asynchrones

Les conceptions asynchrones ne reposent pas sur une horloge globale. Elles utilisent plutôt des protocoles d’échange de signaux ou des signaux locaux pour déclencher des actions. Les diagrammes de temporisation sont ici plus irréguliers.

- Avantages : Consommation d’énergie plus faible dans certains cas. Temps de réponse moyen plus rapide.

- Défis : Complex à vérifier. Suceptible aux conditions de course.

- Caractéristique du schéma : Les signaux se déclenchent mutuellement sans rythme fixe.

Paramètres critiques de temporisation 📏

Des mesures spécifiques définissent la fiabilité d’un diagramme de temporisation. Ces paramètres déterminent si un circuit fonctionnera correctement dans toutes les conditions.

| Paramètre | Description | Signification |

|---|---|---|

| Délai de propagation | Temps nécessaire pour qu’un signal se propage de l’entrée à la sortie. | Limite la fréquence d’opération maximale. |

| Temps de préparation | Les données doivent être stables avant l’edge de l’horloge. | Assure que la bascule capte la bonne valeur. |

| Temps de maintien | Les données doivent rester stables après l’edge de l’horloge. | Empêche la bascule de lire une valeur en changement. |

| Période de l’horloge | Durée d’un cycle complet du signal d’horloge. | Définit la vitesse du système. |

| Cycle de fonctionnement | Pourcentage de la période pendant lequel le signal est à l’état haut. | Affecte la consommation d’énergie et les marges de temps. |

Approfondissement : Temps de préparation et temps de maintien

Les temps de préparation et de maintien sont les contraintes les plus critiques pour la logique séquentielle. En cas de violation, le système peut entrer dans un état métastable où la sortie est indéfinie.

Violation du temps de préparation : Cela se produit lorsque les données changent trop près de l’edge de l’horloge. Le circuit n’a pas assez de temps pour se préparer à la capture. Le résultat est souvent une erreur logique.

Violation du temps de maintien : Cela se produit lorsque les données changent trop tôt après l’edge de l’horloge. Le circuit essaie encore de capturer la valeur précédente. Cela est souvent plus difficile à corriger car cela dépend de la disposition physique.

Lecture et analyse des diagrammes 🔍

Analyser un diagramme temporel nécessite une approche systématique. Suivez ces étapes pour interpréter les données visuelles avec précision.

- Identifiez l’horloge : Trouvez le signal périodique. C’est votre point de référence.

- Localisez les bords actifs : Déterminez si le système est déclenché par des bords montants ou descendants.

- Suivez les dépendances des signaux : Voyez comment les changements dans un signal affectent les autres.

- Vérifiez les parasites : Recherchez des impulsions courtes qui pourraient être du bruit ou des transitions non désirées.

- Vérifiez les contraintes : Assurez-vous que les temps de préparation et de maintien sont respectés pour tous les registres.

Considérez un scénario simple de transfert de données. Un processeur envoie des données à la mémoire. Le diagramme temporel montrera d’abord la stabilisation des lignes d’adresse, puis celle des lignes de données, et enfin le signal d’écriture. Chaque étape doit se produire dans une fenêtre spécifique.

Violations courants et leur impact ⚠️

Même les ingénieurs expérimentés rencontrent des problèmes de temporisation. Comprendre les violations courantes aide au dépannage.

1. Métastabilité

Lorsqu’un signal viole le temps de setup ou de hold, la sortie du bascule peut osciller avant de se stabiliser. Cet état est appelé métastabilité. Elle peut se propager dans le système, provoquant un comportement imprévisible. Des circuits de synchronisation sont souvent utilisés pour atténuer ce risque.

2. Désynchronisation (skew)

La désynchronisation d’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents. Cela peut réduire la marge de temporisation effective. Un désynchronisation positive accorde plus de temps de setup mais moins de temps de hold. Une désynchronisation négative fait l’inverse.

3. Conditions de course

Les conditions de course se produisent lorsque la sortie dépend de la séquence des événements. Si deux signaux changent simultanément, l’ordre de leur traitement détermine l’état final. Les diagrammes de temporisation aident à visualiser ces séquences afin d’éviter les courses.

Application en architecture informatique 🖥️

Les diagrammes de temporisation ne sont pas seulement des outils théoriques. Ils sont largement utilisés dans l’architecture du monde réel.

Interfaces mémoire

La DRAM et la SRAM ont des exigences de temporisation strictes. Le contrôleur mémoire doit attendre des délais spécifiques avant de lire ou d’écrire. Les diagrammes de temporisation définissent les séquences des bus d’ordres. Ils assurent que la banque mémoire est prête avant l’accès aux données.

Protocoles de bus

Les protocoles comme I2C, SPI et UART reposent sur la temporisation pour la communication. La ligne d’horloge dans SPI synchronise le transfert de données. En UART, la temporisation est basée sur les débits (bauds). Le récepteur doit échantillonner la ligne de données au centre exact de la période du bit. Un diagramme de temporisation montre l’alignement du bit de départ, des bits de données et du bit d’arrêt.

Étapes de pipeline

Les processeurs modernes utilisent le pipeline pour exécuter plusieurs instructions en même temps. Chaque étape doit être terminée dans un cycle d’horloge. Les diagrammes de temporisation représentent le flux des données à travers les étapes de récupération, décodage, exécution et écriture. Ils aident à identifier les blocages où une étape attend une autre.

Meilleures pratiques pour la documentation 📝

La création de diagrammes de temporisation clairs garantit que d’autres ingénieurs peuvent comprendre votre conception. Suivez ces recommandations pour une documentation efficace.

- Utilisez des échelles cohérentes : Assurez-vous que l’axe du temps est uniforme dans tout le document.

- Libellez clairement : Nommez chaque signal. Évitez les libellés génériques comme « Signal 1 ».

- Mettez en évidence les contraintes : Utilisez des crochets ou des zones ombrées pour indiquer les fenêtres de setup et de hold.

- Regroupez les signaux connexes : Gardez les signaux de contrôle ensemble et les signaux de données ensemble.

- Incluez des annotations : Ajoutez des notes expliquant les transitions complexes ou les comportements spéciaux.

Considérations avancées 🔬

À mesure que les systèmes deviennent plus rapides, l’analyse de temporisation devient plus complexe. Plusieurs facteurs ajoutent des couches de difficulté.

1. Bruit d’alimentation

Les fluctuations de tension peuvent déplacer les niveaux de seuil des portes logiques. Cela modifie effectivement le délai de propagation. Les diagrammes de temporisation doivent tenir compte des scénarios de tension les plus défavorables.

2. Variations de température

Les composants électroniques se comportent différemment selon la température. Les hautes températures augmentent la résistance et le retard. Les basses températures peuvent affecter la capacité. Les concepteurs doivent vérifier le temporisation sur toute la plage de température de fonctionnement.

3. Intégrité du signal

Les pistes longues sur une carte électronique agissent comme des lignes de transmission. Les réflexions et les interférences peuvent déformer les signaux. Les diagrammes de temporisation doivent inclure des diagrammes d’œil ou des métriques de qualité du signal pour les liaisons à haute vitesse.

Conclusion sur l’analyse de temporisation 🎯

Les diagrammes de temporisation sont la carte pour naviguer dans la logique numérique. Ils traduisent les états binaires abstraits en événements temporels physiques. Pour un étudiant en informatique, la maîtrise de la lecture et de la création de ces diagrammes est une compétence fondamentale.

En comprenant les cycles d’horloge, les délais de propagation et les contraintes de configuration, vous pouvez concevoir des systèmes robustes et efficaces. La capacité à visualiser le flux des signaux évite des erreurs coûteuses dans la conception matérielle. Alors que la technologie évolue, les principes restent les mêmes. Le temps est la variable constante.

Concentrez-vous sur les fondamentaux. Pratiquez la lecture des diagrammes existants. Dessinez les vôtres pour chaque nouveau circuit que vous concevez. Cette discipline vous sera très utile dans votre carrière technique.