Dans la conception numérique moderne, comprendre le flux des signaux au fil du temps est essentiel pour garantir la fiabilité du système. Les systèmes asynchrones, dont les opérations ne sont pas régies par une horloge globale unique, posent des défis particuliers par rapport à leurs homologues synchrones. L’outil principal utilisé pour visualiser et déboguer ces interactions complexes est le diagramme temporel. Ce guide offre une analyse approfondie de la manière de construire, lire et analyser les diagrammes temporels dans des environnements asynchrones.

La nature de la conception asynchrone 🌐

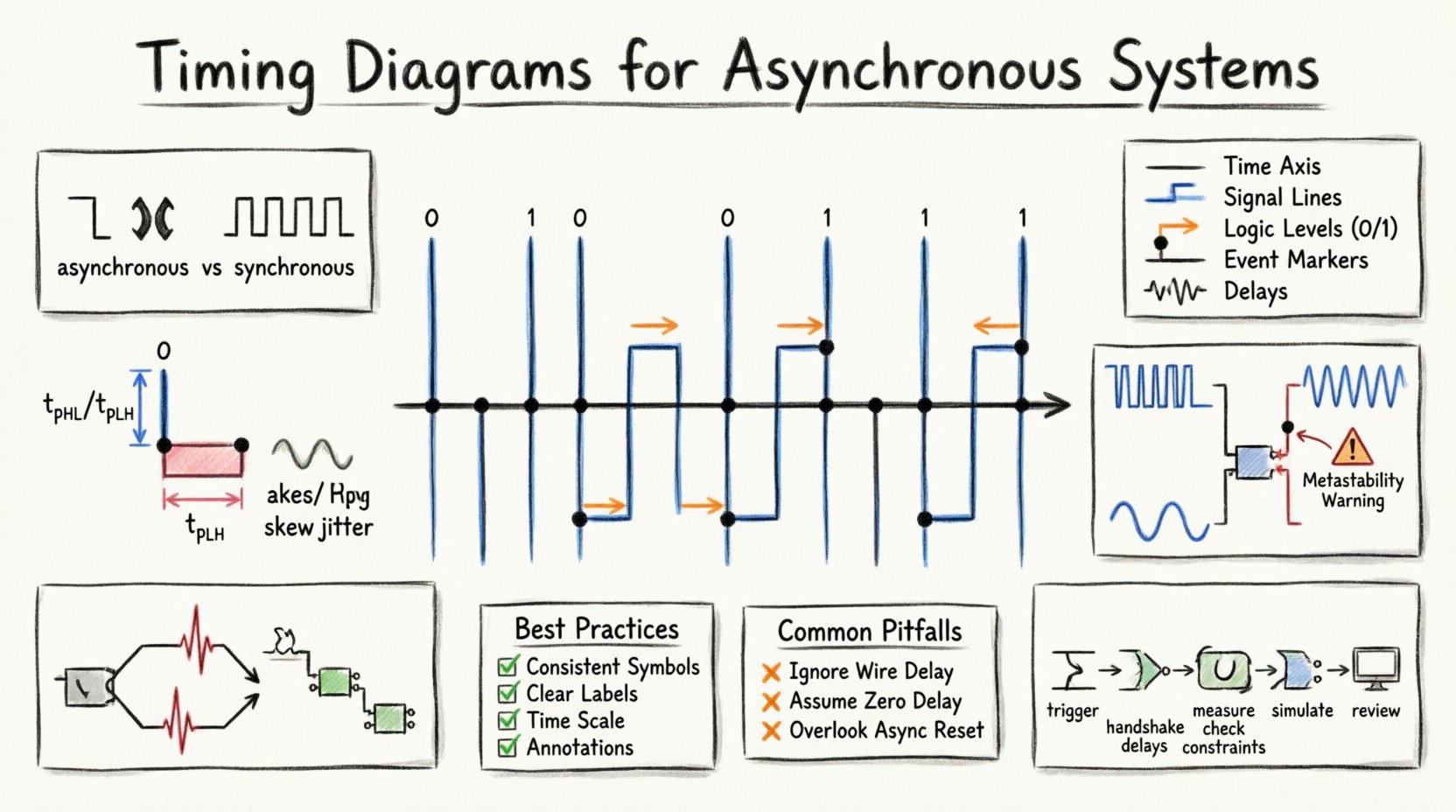

Les systèmes asynchrones fonctionnent sans signal d’horloge centralisé qui commande chaque changement d’état. À la place, les événements sont déclenchés par la fin des opérations précédentes ou par l’arrivée des données. Cette approche présente des avantages tels qu’une consommation d’énergie réduite et une performance potentielle plus élevée dans certains contextes. Toutefois, elle introduit une complexité concernant la synchronisation des signaux et la vérification du temps.

Lorsqu’elles analysent ces systèmes, les équipes doivent tenir compte des délais variables, des temps de propagation et de l’absence de point de référence universel. Les diagrammes temporels servent de langage visuel pour cartographier ces événements. Ils permettent aux équipes de voir la relation exacte entre les transitions de signaux au fil du temps.

Anatomie d’un diagramme temporel 📐

Un diagramme temporel est une représentation graphique du comportement des signaux. Il représente le temps sur l’axe horizontal et les états des signaux sur l’axe vertical. Pour analyser efficacement un système asynchrone, il est nécessaire de comprendre les composants fondamentaux qui constituent ces diagrammes.

- Axe du temps : Représente l’évolution du temps. Dans l’analyse asynchrone, cela est souvent relatif à un déclencheur d’événement spécifique plutôt qu’à un cycle d’horloge.

- Lignes de signal :Lignes horizontales représentant des fils ou des réseaux individuels. Chaque ligne suit le niveau logique (Haut, Bas ou Inconnu) d’un signal spécifique.

- Niveaux logiques : Notés généralement comme

0(Bas/Terre) et1(Haut/VCC). Les transitions entre ces états constituent le cœur de l’analyse. - Marqueurs d’événements :Lignes verticales ou annotations indiquant des occurrences spécifiques, telles qu’un signal d’échange de mains changeant d’état.

- Délais :Espaces visuels entre un changement d’entrée et le changement de sortie correspondant, représentant le délai de propagation.

Contrairement aux diagrammes synchrones qui s’appuient sur des lignes de grille représentant les fronts d’horloge, les diagrammes asynchrones s’appuient sur les frontières d’événements. Cela exige une interprétation plus soigneuse de l’écart entre les transitions.

Paramètres temporels critiques ⚙️

Pour analyser l’intégrité d’un système asynchrone, des paramètres temporels spécifiques doivent être mesurés et comparés aux spécifications du design. Ces paramètres définissent la fenêtre dans laquelle un signal doit être stable pour être correctement interprété par un récepteur.

Délai de propagation

Le délai de propagation est le temps nécessaire à un signal pour passer de l’entrée d’un composant à sa sortie. Dans la logique asynchrone, ce délai est une source principale d’incertitude. Les variations de fabrication, de température et de tension peuvent modifier ce délai.

- tpHL :Temps nécessaire à un signal pour passer de Haut à Bas.

- tpLH :Temps nécessaire à un signal pour passer de Bas à Haut.

- tpd : Retard de propagation général, souvent calculé comme la moyenne de tpHL et tpLH.

Lors de l’analyse d’un diagramme de temporisation, recherchez la distance horizontale entre le front d’entrée et le front de sortie correspondant. Cette distance est le retard de propagation.

Temps de préparation et temps de maintien

Même dans les systèmes asynchrones, les bascules et les verrous nécessitent souvent des fenêtres spécifiques de stabilité. Le temps de préparation est la durée avant un événement déclencheur pendant laquelle les données doivent être stables. Le temps de maintien est la durée après l’événement déclencheur pendant laquelle les données doivent rester stables.

Si ces fenêtres sont violées, le système peut entrer dans un état de métastabilité, où la sortie n’est ni Haute ni Basse, mais un niveau de tension indéfini. Les diagrammes de temporisation aident à visualiser ces violations en montrant si les données changent trop près d’un front de contrôle.

Désynchronisation et jitter

- S désynchronisation : La différence de temps d’arrivée du même signal à deux points différents du circuit.

- Jitter : Des variations à court terme dans le timing du signal. Dans les systèmes asynchrones, le jitter peut être causé par du bruit d’alimentation ou des interférences.

Gestion des traversées de domaines d’horloge 🔄

L’une des sources les plus courantes d’erreurs dans les systèmes mixtes concerne les traversées entre différents domaines d’horloge. Même si un système est principalement asynchrone, il contient souvent des sous-blocs synchrones fonctionnant à des fréquences différentes. Les diagrammes de temporisation sont essentiels pour vérifier ces traversées.

Lorsqu’un signal passe d’un domaine d’horloge à un autre, le récepteur peut échantillonner le signal à un moment où celui-ci change. Cela entraîne une métastabilité. La méthode standard pour atténuer ce phénomène consiste à utiliser un synchroniseur, généralement une chaîne de bascules.

| Paramètre | Description | Impact sur le diagramme de temporisation |

|---|---|---|

| Temps de résolution de la métastabilité | Temps nécessaire au synchroniseur pour atteindre un niveau logique valide | Montre une période étendue d’état indéfini avant que le signal ne se stabilise |

| Latence de traversée de domaine | Retard supplémentaire introduit par le synchroniseur | Augmente l’écart temporel entre l’événement source et l’événement de destination |

| Latence d’échange de signaux | Temps nécessaire pour les signaux d’acquittement dans les protocoles asynchrones | Crée un motif aller-retour dans le chronogramme du signal |

Les analystes doivent s’assurer que le diagramme de temporisation tient compte du temps de résolution. Si un bloc aval tente de lire le signal avant que le synchroniseur ne se soit stabilisé, une corruption des données se produit.

Identification et résolution des conditions de course ⚠️

Une condition de course se produit lorsque le comportement du système dépend du timing relatif d’événements qui ne devraient pas s’influencer mutuellement. En logique asynchrone, c’est un problème fréquent. Les diagrammes de temporisation sont la méthode principale pour détecter ces conditions.

Aléas statiques

Une erreur statique se produit lorsque un signal devrait rester à un niveau constant mais bascule brièvement en raison de délais de parcours. Par exemple, si un signal doit logiquement rester à l’état haut, mais qu’un changement d’entrée provoque une brève baisse vers le bas, il s’agit d’une erreur statique-1.

- Indicateur visuel : Un pic étroit ou une impulsion sur une ligne de signal qui devrait être plate.

- Cause racine : Des délais de propagation inégaux à travers différentes portes logiques.

Erreurs dynamiques

Les erreurs dynamiques impliquent plusieurs transitions alors qu’une seule est attendue. Cela se produit souvent dans des chemins logiques complexes où les signaux passent par un nombre différent de portes.

Étapes d’analyse des conditions de course

- Suivre les chemins : Identifier tous les chemins empruntés par un signal depuis sa source jusqu’à sa destination.

- Mesurer les délais : Calculer le délai de chaque chemin à l’aide du diagramme de temporisation.

- Comparer les fronts : Vérifier si les temps d’arrivée des signaux concurrents se chevauchent d’une manière qui crée une ambiguïté.

- Vérifier la stabilité : S’assurer que les signaux de contrôle restent stables pendant la fenêtre critique d’arrivée des données.

Si une condition de course est détectée, la conception pourrait nécessiter une restructuration. Les solutions courantes incluent l’ajout de tampons pour égaliser les délais, l’insertion de protocoles d’échange de mains, ou l’utilisation de structures FIFO asynchrones.

Intégrité du signal et considérations sur le bruit 🔌

Les diagrammes de temporisation n’existent pas en vase clos. La couche physique introduit des bruits qui affectent la qualité du signal. Lors de l’analyse des systèmes asynchrones, les ingénieurs doivent distinguer les erreurs logiques de temporisation des dégradations physiques du signal.

Glitches de signal

Les glitches sont des impulsions de courte durée qui peuvent se propager dans un circuit. Dans les systèmes asynchrones, un glitch peut déclencher erronément une bascule ou une mémoire. Les diagrammes de temporisation les montrent souvent sous forme de pics fins.

- Filtrage : S’assurer que la logique en aval dispose d’un délai suffisant pour filtrer ces impulsions.

- Vitesse de montée/descente : Des fronts plus raides (temps de montée/descente plus rapides) sont plus sensibles au couplage de bruit.

Couplage crosstalk

Le crosstalk se produit lorsque le signal sur un fil induit une tension sur un fil voisin. Cela peut décaler le timing d’un signal, le faisant arriver plus tôt ou plus tard que prévu.

Dans un diagramme de temporisation, le crosstalk peut se manifester par un décalage de la position du front ou par un pic supplémentaire de bruit. Pour atténuer ce phénomène, l’écartement entre les signaux doit être pris en compte lors de la phase de conception physique.

Meilleures pratiques pour la documentation 📝

Une documentation claire garantit que l’analyse de temporisation peut être reproduite et comprise par d’autres ingénieurs. Un diagramme de temporisation bien structuré inclut des métadonnées spécifiques et des annotations.

Normalisation

- Utilisez des symboles cohérents pour les niveaux logiques.

- Marquez tous les signaux clairement avec leur fonction.

- Indiquez l’échelle de temps de manière explicite (par exemple, nanosecondes par division).

Annotations

Les annotations textuelles sont essentielles pour expliquer des comportements spécifiques. Utilisez des flèches pour indiquer les transitions critiques ou les zones potentielles de problème. Indiquez les valeurs de délai de propagation directement sur le schéma.

Contrôle de version

Les diagrammes de temporisation évoluent avec les modifications du design. Maintenez des numéros de version pour tous les diagrammes afin de garantir que l’analyse correspond à l’état actuel du matériel. Ne comptez pas sur la mémoire pour les détails de temporisation.

Processus d’analyse étape par étape 🛠️

Pour analyser efficacement un système asynchrone, suivez une approche structurée. Cela garantit que aucun paramètre de temporisation critique n’est négligé.

- Définissez le déclencheur :Identifiez l’événement qui déclenche la séquence. C’est généralement le point de départ de l’axe du temps.

- Cartographiez la mainmise :Suivez les signaux de demande et d’acquittement. Assurez-vous qu’ils suivent le protocole correct (par exemple, mainmise à quatre phases ou à deux phases).

- Mesurez les délais :Calculez la latence totale depuis le déclencheur jusqu’à la sortie finale. Décomposez-la en délais des composants.

- Vérifiez les contraintes :Vérifiez que les temps de setup et de hold sont respectés pour tous les éléments de stockage impliqués.

- Simulez les variations :Analysez le schéma dans des conditions extrêmes, telles que la température maximale ou la tension minimale.

- Revoyez la métastabilité :Assurez-vous que la probabilité de métastabilité est réduite à un niveau acceptable grâce aux synchronisateurs.

Péchés courants dans l’analyse de temporisation ⚡

Même les ingénieurs expérimentés peuvent manquer des problèmes subtils. Être conscient des pièges courants aide à éviter des reconfigurations coûteuses.

- Ignorer le délai de filage :Se fier uniquement au délai de porte tout en négligeant la résistance et la capacité des interconnexions.

- Supposer un délai nul :Traiter les boucles de rétroaction comme instantanées, ce qui est physiquement impossible.

- Ne pas tenir compte du réinitialisation asynchrone :Échouer à tenir compte du timing des signaux de réinitialisation par rapport aux signaux de données.

- Confusion entre front et niveau : Confondre les comportements déclenchés par front et par niveau lors de l’interprétation du schéma.

Conclusion sur la vérification ✅

Les diagrammes temporels sont indispensables pour la vérification des systèmes asynchrones. Ils offrent une représentation visuelle concrète des relations temporelles abstraites. En analysant rigoureusement ces diagrammes, les ingénieurs peuvent identifier les conditions de course, vérifier les protocoles d’échange de main, et garantir l’intégrité du signal.

La complexité de la conception asynchrone exige une précision absolue. Chaque nanoseconde compte. Une compréhension approfondie des délais de propagation, des temps de setup et des temps de maintien permet de concevoir des systèmes robustes. Bien que l’absence d’une horloge globale ajoute de la difficulté, les insights tirés d’une analyse temporelle détaillée conduisent à des conceptions plus efficaces et fiables.

Continuer à affiner ces compétences d’analyse garantit que les systèmes fonctionnent correctement dans des conditions environnementales variables. L’objectif est la stabilité et la prévisibilité, obtenues grâce à une documentation et une mesure méticuleuses.

Considérations avancées 🔬

Pour les applications à haute performance, des facteurs supplémentaires entrent en jeu. Cela inclut les gradients de température à travers le circuit intégré et les baisses de tension lors des événements de commutation.

- Gradients de température :Les signaux qui voyagent du centre chaud d’un circuit intégré vers le bord plus froid subiront des vitesses différentes. Cette variation doit être prise en compte dans l’analyse temporelle.

- Bruit du réseau d’alimentation :Le bruit de commutation simultanée peut décaler les seuils logiques. Les diagrammes temporels devraient idéalement inclure une représentation de la stabilité des rails d’alimentation.

- Latence variable :Certains protocoles asynchrones autorisent une latence variable. Le diagramme temporel doit indiquer la plage de latences acceptables, et non pas une seule valeur.

En intégrant ces considérations avancées, l’analyse temporelle devient un outil complet de validation du système. Elle va au-delà de la simple vérification vers une véritable optimisation des performances.

Souvenez-vous que le temps ne concerne pas seulement la vitesse ; il concerne la correction. Un système rapide qui échoue à cause d’erreurs temporelles est moins utile qu’un système plus lent qui fonctionne de manière fiable. Le diagramme temporel est la carte qui vous guide vers cette fiabilité.