Dans le monde complexe de l’ingénierie embarquée, le timing est tout. Un microcontrôleur peut fonctionner parfaitement en simulation mais échouer catastrophiquement sur le matériel en raison de quelques nanosecondes de retard. C’est là que le diagramme de timing devient un outil indispensable. Ces représentations visuelles décrivent le comportement des signaux au fil du temps, offrant un aperçu clair de la manière dont les composants interagissent au sein d’un système numérique. Que vous soyez en train de déboguer une panne de communication ou de concevoir une nouvelle interface périphérique, comprendre comment lire et créer des diagrammes de timing est fondamental.

Ce guide couvre les mécanismes essentiels du timing des signaux, des définitions de base aux interactions complexes des protocoles. Nous explorerons comment interpréter les formes d’onde, construire des diagrammes précis à partir de données de mesure, et identifier les pièges courants qui entraînent une instabilité du système. En maîtrisant ces outils visuels, vous acquérez la capacité de prédire le comportement du système et de valider les conceptions avant même qu’elles ne quittent le banc de test.

🔍 Comprendre les bases du timing des signaux

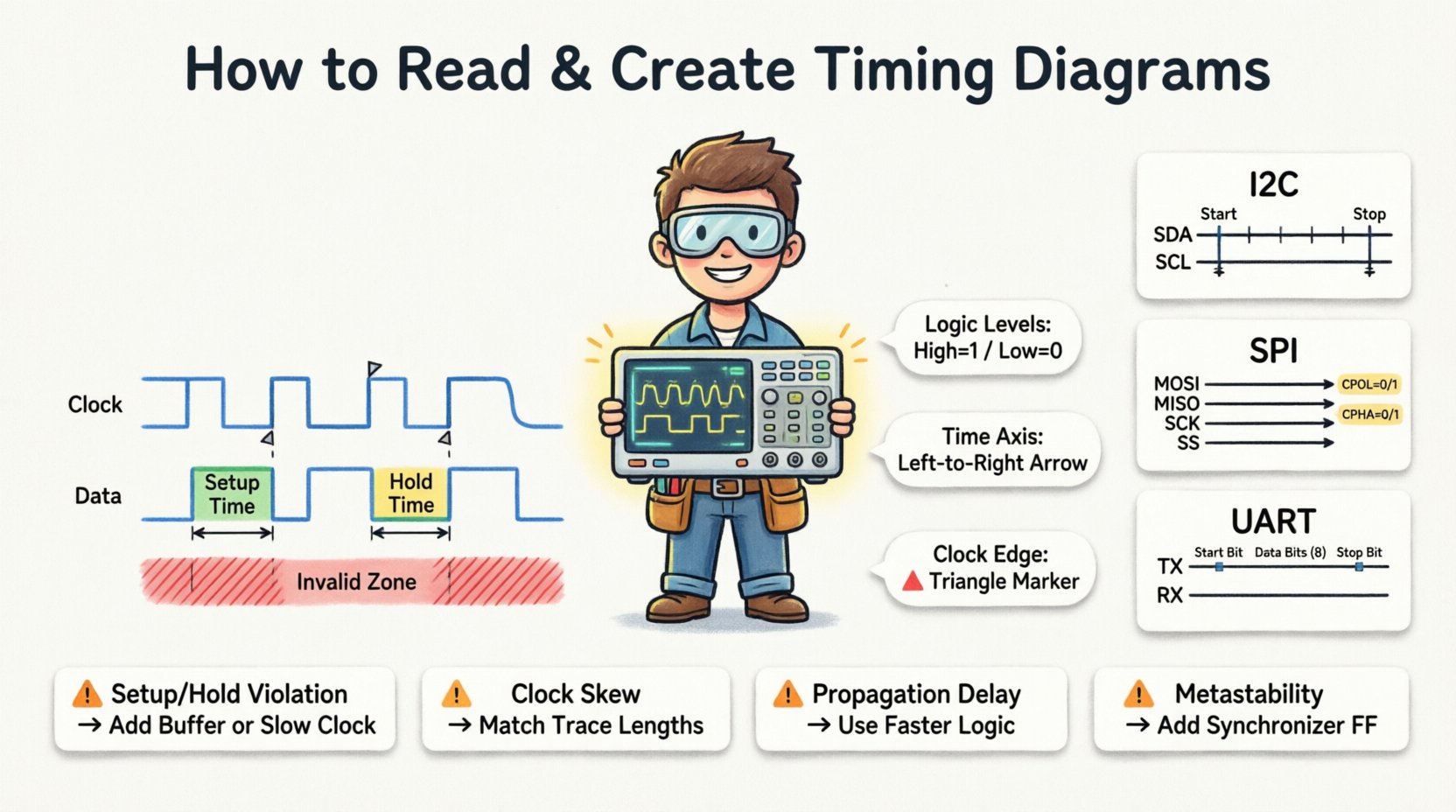

Un diagramme de timing n’est pas simplement un dessin ; c’est une représentation mathématique des états logiques par rapport à un axe temporel. Dans les systèmes embarqués, nous traitons principalement des niveaux logiques numériques, qui sont binaires : Haut (1) et Bas (0). Toutefois, c’est au niveau des transitions entre ces niveaux que réside la complexité.

- Niveaux logiques :La plupart des systèmes embarqués fonctionnent selon des seuils de tension spécifiques. Par exemple, un système 3,3 V définit le Haut comme toute tension supérieure à 2,0 V et le Bas comme toute tension inférieure à 0,8 V.

- Axe temporel :Le temps s’écoule de gauche à droite. L’écart horizontal représente la durée d’états spécifiques ou le délai entre les événements.

- Traçages de signal : Chaque ligne horizontale représente un fil ou un réseau spécifique. Plusieurs lignes empilées verticalement permettent de comparer les relations entre les signaux.

Lors de l’analyse d’un système, vous recherchez la causalité. Le signal d’horloge déclenche-t-il le changement de données ? Le signal d’activation doit-il être actif avant que les données ne soient valides ? Les diagrammes de timing répondent à ces questions de manière visuelle.

🛠️ Composants clés d’un diagramme de timing

Pour interpréter correctement un diagramme, vous devez reconnaître les éléments standards utilisés pour indiquer le comportement du signal. Ces composants définissent les règles d’engagement pour le matériel.

| Composant | Description | Indicateur visuel |

|---|---|---|

| Nom du signal | Identifie le fil ou le réseau spécifique | Étiquette de texte à gauche |

| Niveau logique | État Haut (1) ou Bas (0) | Ligne horizontale plate en haut ou en bas |

| Front de transition | Changement du Haut au Bas ou inversement | Ligne verticale reliant les niveaux |

| Front d’horloge | Point de déclenchement pour la logique synchrone | Ligne pointillée ou marqueur triangulaire |

| Zone invalide | Zone où les données ne peuvent pas être lues | Zone ombrée ou hachurée |

Comprendre ces composants vous permet de déconstruire des interactions complexes. Par exemple, une zone ombrée indique souvent une exigence de temps de préparation ou de maintien, où l’appareil récepteur ne peut pas capturer les données de manière fiable.

👁️ Comment lire un diagramme de temporisation étape par étape

La lecture d’un diagramme de temporisation nécessite une approche systématique. Vous traduisez essentiellement un motif visuel en une séquence d’événements. Suivez ce processus pour garantir une précision maximale.

1. Identifier la source d’horloge

La plupart des systèmes embarqués sont synchrones, ce qui signifie qu’un signal d’horloge détermine le rythme des opérations. Localisez la piste d’horloge. Elle présente généralement une onde carrée régulière et périodique.

- Vérifiez la fréquence. Est-elle de 1 MHz ou de 100 MHz ? Cela détermine la vitesse de l’ensemble du système.

- Identifiez le type de transition. L’appareil se déclenche-t-il sur la montée (passage de bas à haut) ou sur la descente (passage de haut à bas) ?

2. Cartographier les fenêtres de validité des données

Les données ne sont valables que durant des fenêtres spécifiques par rapport à l’horloge. Recherchez la relation entre l’arête de l’horloge et la ligne de données.

- Temps de préparation : Les données doivent rester stables pendant une certaine période avant l’arête de l’horloge.

- Temps de maintien : Les données doivent rester stables pendant une certaine période après l’arête de l’horloge.

Si les données changent durant ces fenêtres, une violation de temporisation se produit, entraînant une métastabilité ou une capture incorrecte des données.

3. Analyser les signaux de contrôle

Les signaux de contrôle tels que Chip Select (CS), Enable (EN) ou Reset (RST) déterminent quand la communication peut avoir lieu.

- Le Chip Select est-il actif bas ou actif haut ?

- Le signal Enable doit-il être activé avant que l’horloge ne commence à alterner ?

- Y a-t-il des événements asynchrones qui remplacent la logique de l’horloge ?

4. Vérifier les mécanismes d’échange de signaux

Beaucoup de protocoles utilisent l’échange de signaux pour gérer le contrôle de flux. Recherchez les signaux Acknowledge (ACK) ou Ready (RDY).

- L’émetteur attend-il un signal avant d’envoyer le prochain octet ?

- Des conditions de défaillance après délai sont-elles représentées sur le diagramme ?

📐 Comment créer des diagrammes de temporisation précis

Créer un diagramme de timing est aussi important que de le lire. Il sert de spécification aux ingénieurs en matériel et de guide de vérification aux développeurs logiciels. Vous pouvez les générer à partir de spécifications, d’outils de mesure ou de données de simulation.

Étape 1 : Définir les exigences du protocole

Avant de dessiner, rassemblez les spécifications. Elles proviennent généralement de la fiche technique du composant avec lequel vous interagissez.

- Extraire les fréquences minimales et maximales de l’horloge.

- Notez les niveaux de tension pour les états logiques Haut et Bas.

- Enregistrez les contraintes de temps de préparation (setup) et de maintien (hold).

Étape 2 : Capturer les données des signaux

Utilisez des outils matériels pour capturer le comportement du monde réel. Cela garantit que votre diagramme reflète la réalité plutôt que des idéaux théoriques.

- Oscilloscopes : Idéal pour l’intégrité des signaux analogiques et les niveaux de tension.

- Analyseurs logiques : Idéal pour les transitions d’état numériques et le timing multi-canaux.

- Modèles de simulation : Convient pour vérifier la logique avant la disponibilité du matériel.

Étape 3 : Tracer les formes d’onde

Tracez les signaux dans l’ordre chronologique. Assurez-vous que l’échelle de temps est cohérente sur toutes les voies.

- Utilisez des lignes droites pour les niveaux logiques.

- Utilisez des lignes diagonales pour les transitions afin d’indiquer les temps de montée et de descente.

- Marquez les points critiques tels que le front de l’horloge et le changement de données.

Étape 4 : Annoter les contraintes critiques

Les annotations fournissent un contexte que les visuels seuls ne peuvent pas transmettre.

- Marquez explicitement les fenêtres de temps de préparation (setup) et de maintien (hold).

- Indiquez la durée d’états spécifiques du protocole (par exemple, bit de départ, bit d’arrêt).

- Mettez en évidence toute latence ou délai connu dans le chemin du signal.

🌐 Diagrammes de timing dans les protocoles embarqués courants

Les différents protocoles de communication ont des caractéristiques de timing distinctes. Comprendre ces nuances est essentiel pour l’intégration.

1. Circuit intégré interconnecté (I2C)

I2C est un bus série synchrone à deux fils. Il utilise SDA (Données) et SCL (Horloge).

- Condition de démarrage : SDA passe de Haut à Bas tandis que SCL est à Haut.

- Condition d’arrêt : SDA passe de bas à haut pendant que SCL est à haut.

- Transfert de données : Les données sont valides lorsque SCL est à haut ; les changements ont lieu lorsque SCL est à bas.

- ACK/NACK : Le récepteur tire SDA à bas pendant la neuvième impulsion d’horloge pour confirmer la réception.

2. Interface périphérique série (SPI)

SPI est un bus synchrone à quatre fils offrant des vitesses plus élevées que I2C.

- Lignes : MOSI (Sortie maître), MISO (Entrée maître), SCK (Horloge), SS (Sélection esclave).

- CPOL : La polarité de l’horloge détermine l’état inactif (haut ou bas).

- CPHA : La phase de l’horloge détermine quand les données sont échantillonnées (première ou deuxième transition).

- Sélection de puce : Doit être activé (asserté) avant que l’horloge ne commence à basculer.

3. Récepteur-émetteur asynchrone universel (UART)

UART est asynchrone, ce qui signifie qu’il n’y a pas de signal d’horloge partagé. Le timing repose sur les débits.

- Bit de départ : Tire la ligne à bas pour signaler le début d’une trame.

- Bits de données : Transmis en commençant par le bit de poids faible, généralement 8 bits.

- Bit d’arrêt : Tire la ligne à haut pour signaler la fin d’une trame.

- Parité : Bit facultatif pour la vérification d’erreurs.

| Fonctionnalité | I2C | SPI | UART |

|---|---|---|---|

| Horloge | Synchronisé (partagé) | Synchronisé (partagé) | Asynchronisé (pas d’horloge) |

| Fils | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Adressage | Oui (adresse par octet) | Non (basé sur les câblages) | Non |

| Vitesse maximale | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Violations de temporisation courantes et débogage

Même avec une conception soigneuse, des violations de temporisation peuvent survenir. Elles sont souvent à l’origine de bogues intermittents difficiles à reproduire.

1. Violations de temps de préparation et de maintien

Cela se produit lorsque les données arrivent trop tôt ou trop tard par rapport au front de l’horloge.

- Symptôme : Corruption des données ou erreurs aléatoires dans la capture de l’analyseur logique.

- Solution : Réduire la vitesse de l’horloge ou optimiser les longueurs des pistes du circuit imprimé.

2. Désynchronisation de l’horloge

La désynchronisation de l’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents.

- Symptôme : Conditions de course où une bascule capte les données avant qu’une autre ne soit prête.

- Solution : Égaliser les longueurs des pistes ou utiliser un réseau dédié de distribution de l’horloge.

3. Délai de propagation

Les signaux mettent du temps à voyager à travers les fils et les portes. Les traces longues ajoutent un délai important.

- Symptôme : Problèmes d’intégrité du signal ou réflexions sur les lignes à haute vitesse.

- Solution : Utilisez des résistances de terminaison et maintenez les traces aussi courtes que possible.

4. Métastabilité

Lorsque des signaux asynchrones traversent des domaines d’horloge, le bascule réceptrice peut entrer dans un état métastable.

- Symptôme : Blocages du système ou réinitialisations aléatoires.

- Solution : Utilisez des chaînes de synchronisation (deux ou plusieurs bascules en série) pour résoudre le signal.

📝 Meilleures pratiques pour la documentation

La création de diagrammes de temporisation pour la documentation garantit que les développeurs futurs peuvent comprendre le système sans avoir à reverse-ingénier le matériel.

- Conformité : Utilisez des symboles et des styles de ligne standard dans tous les diagrammes du projet.

- Échelle : Assurez-vous que l’axe du temps est linéaire et clairement étiqueté avec des unités (ns, µs, ms).

- Référence : Liez toujours le diagramme à la section spécifique du datasheet ou à la norme du protocole.

- Clarté : Évitez le bazar. Si un signal est statique, affichez-le comme une ligne droite plutôt que comme un bruit de basculement.

- Gestion de version : Mettez à jour les diagrammes chaque fois que le matériel ou le firmware change de manière significative.

🔗 Réflexions finales sur l’intégrité du signal

Les diagrammes de temporisation combler le fossé entre la logique abstraite et la réalité physique. Ils permettent aux ingénieurs de visualiser les contraintes invisibles de l’électronique numérique. En apprenant à les lire, vous pouvez dépanner des problèmes matériels complexes. En apprenant à les créer, vous pouvez concevoir des systèmes robustes qui fonctionnent de manière fiable dans toutes les conditions.

Le processus exige de la patience et une attention aux détails. Chaque front, chaque délai et chaque niveau de tension compte. À mesure que les systèmes embarqués deviennent plus rapides et plus complexes, la dépendance aux diagrammes de temporisation précis ne fera que croître. Traitez-les comme des spécifications critiques plutôt que comme une documentation optionnelle.

Commencez par analyser les fiches techniques des composants que vous utilisez. Recherchez les spécifications de temporisation. Ensuite, essayez de dessiner les diagrammes à partir de ces chiffres. Comparez vos dessins avec les mesures réelles obtenues à l’aide de vos outils. Ce cycle de prédiction et de vérification développe l’intuition nécessaire pour la conception de haut niveau des systèmes embarqués.

Souvenez-vous qu’un diagramme est un outil de communication. Il doit transmettre les informations nécessaires à un autre ingénieur avec un minimum d’ambiguïté. Des diagrammes de temporisation clairs et précis réduisent le temps de développement et évitent les révisions matérielles coûteuses. Investissez le temps pour maîtriser cette compétence, et elle vous rapportera des bénéfices tout au long de votre carrière d’ingénieur.