Les diagrammes de timing sont la colonne vertébrale de la vérification des systèmes numériques. Ils transforment la logique abstraite en lignes de temps visuelles sur lesquelles s’appuient les ingénieurs, les concepteurs et les testeurs pour valider le comportement des signaux. Lorsqu’un diagramme de timing contient des erreurs, les conséquences vont bien au-delà du simple croquis. Des hypothèses erronées sur le timing peuvent entraîner des défaillances matérielles, une corruption des données ou une instabilité du système dans les environnements de production. Ce guide explore les pièges les plus fréquents rencontrés dans l’analyse du timing et propose des stratégies concrètes pour garantir une précision optimale.

La création d’un diagramme de timing précis exige bien plus que le simple tracé de lignes. Elle exige une compréhension approfondie des domaines d’horloge, de la propagation des signaux et des contraintes physiques. Les ingénieurs ont souvent tendance à précipiter la phase de visualisation, négligeant des détails subtils qui deviennent critiques lors de l’implémentation. En reconnaissant ces erreurs courantes dès le départ, les équipes peuvent économiser un temps considérable lors des phases de débogage et d’intégration. Examinons maintenant les domaines spécifiques où les erreurs surviennent le plus fréquemment.

1. Interprétation erronée des violations de temps de setup et de hold ⚠️

Les temps de setup et de hold sont des contraintes fondamentales dans la conception numérique synchrone. Une violation de setup survient lorsque les données arrivent trop tardivement avant le front actif de l’horloge. Une violation de hold se produit lorsque les données changent trop tôt après le front de l’horloge. Ce ne sont pas seulement des concepts théoriques ; ils représentent des limites physiques des bascules et des portes logiques.

Beaucoup de diagrammes ne marquent pas clairement la fenêtre de validité des signaux de données. Lors du tracé de ces signaux, les ingénieurs omettent parfois les fenêtres critiques de setup et de hold, ce qui crée une ambiguïté lors de la revue. Un diagramme solide doit indiquer explicitement ces fenêtres par rapport au front de l’horloge.

- Erreur courante : Tracer les transitions de données alignées exactement sur le front de l’horloge sans tenir compte du jitter ou du décalage.

- Erreur courante : Ignorer la direction du front (montant ou descendant) pour les fenêtres de setup/hold.

- Erreur courante : Supposer des fronts d’horloge idéaux avec une durée de transition nulle.

Pour éviter ces problèmes, annotez toujours les marges de setup et de hold. Utilisez un hachurage distinct ou des repères pour indiquer les zones interdites où les transitions de données sont invalides. Ce repère visuel oblige les relecteurs à vérifier que le chemin du signal respecte les exigences de timing de la logique réceptrice.

2. Négliger le décalage d’horloge et le jitter 🌪️

Le décalage d’horloge (clock skew) désigne la différence entre les temps d’arrivée du signal d’horloge sur différents composants. Le jitter représente les variations à court terme du timing du signal d’horloge. Ces deux facteurs peuvent modifier considérablement les fenêtres de timing effectives pour les signaux de données.

Une erreur courante dans les diagrammes consiste à traiter l’horloge comme une ligne verticale parfaitement droite sur tous les composants. En réalité, les réseaux de distribution introduisent des délais. Si un diagramme montre une seule ligne d’horloge qui se ramifie vers trois registres différents sans tenir compte des différences de parcours, il donne une vision irréaliste du comportement du système.

- Impact : Le décalage peut réduire le temps disponible pour la propagation des données, entraînant des violations de setup erronées.

- Impact : Le jitter peut réduire la marge de temps de hold, augmentant ainsi le risque de métastabilité.

Lors de la création de diagrammes, représentez les chemins d’horloge par des lignes distinctes avec des décalages relatifs si le décalage est significatif. Si le décalage est négligeable, indiquez clairement cette hypothèse dans les notes du diagramme. Ne cachez pas la complexité de la distribution d’horloge si elle affecte le budget de timing.

3. Échelles et unités de temps incohérentes 📏

L’une des erreurs les plus simples mais les plus dommageables consiste à mélanger les échelles de temps dans un même diagramme. Une section peut montrer des nanosecondes tandis qu’une autre affiche des microsecondes. Cette incohérence oblige le lecteur à recalculer constamment les rapports, augmentant ainsi le risque d’interprétation erronée.

Un autre problème est l’absence d’un axe du temps clair. Sans barre d’échelle ou des graduations étiquetées, la durée des impulsions devient subjective. Une impulsion courte pourrait être de 10 nanosecondes ou de 100 nanosecondes selon la manière dont le lecteur interprète l’écartement.

Suivez ces normes pour maintenir une cohérence :

- Définir l’échelle : Placez une règle de temps en bas ou en haut du diagramme.

- Utilisez la notation scientifique : Indiquez clairement les unités (ns, μs, ps) dans l’en-tête.

- Maintenez les rapports proportionnels : Assurez-vous que la distance horizontale entre les événements correspond à la différence de temps.

La cohérence construit la confiance. Chaque ingénieur qui regarde le schéma doit pouvoir déduire les mêmes valeurs de temporisation sans avoir à faire d’hypothèses sur l’échelle du dessin.

4. Ambiguïté dans les déclenchements sur front 🔄

La logique numérique repose souvent sur des déclenchements spécifiques sur front, tels que le front montant ou le front descendant. Un diagramme de temporisation doit indiquer explicitement quel front déclenche l’action. Une ambiguïté ici peut entraîner un comportement complètement opposé dans le matériel.

Une erreur courante consiste à dessiner un signal d’horloge sans indiquer le front actif. Par exemple, si un bascule se déclenche sur le front descendant, mais que le schéma ressemble à celui d’un déclenchement sur front montant, le concepteur logique pourrait implémenter un comportement incorrect.

- Meilleure pratique :Utilisez des flèches sur la ligne d’horloge pour indiquer le front actif.

- Meilleure pratique :Indiquez le type de déclenchement dans la légende (par exemple, « Posedge », « Nedge »).

- Meilleure pratique :Évitez d’utiliser des flèches doubles sauf si les deux fronts sont actifs.

La clarté est primordiale. Si un signal est asynchrone, assurez-vous qu’il soit clairement séparé du domaine d’horloge afin d’éviter toute confusion quant au front qui le contrôle.

5. Oublier les délais de propagation ⏳

Le délai de propagation est le temps nécessaire à un signal pour passer de l’entrée à la sortie à travers une porte logique ou un fil. Dans les schémas idéaux, les signaux semblent changer instantanément. Dans les systèmes physiques, il y a toujours un délai.

Lorsque les concepteurs omettent les délais de propagation, le diagramme de temporisation suggère que la sortie change immédiatement après le changement d’entrée. Cela peut masquer des violations de temporisation qui se produiront dans le silicium. Par exemple, un chemin combinatoire pourrait sembler respecter la période d’horloge sur le schéma, mais le délai réel fait dépasser les données le prochain front d’horloge.

| Fonctionnalité | Schéma idéal | Implémentation en situation réelle |

|---|---|---|

| Transition du signal | Ligne verticale | Ligne inclinée avec délai |

| Propagation | Instantanée | Délai de porte + délai de fil |

| Marge de setup | Souvent non vérifié | Doit tenir compte du pire cas |

Pour atténuer ce problème, indiquez le délai attendu sur les chemins critiques. Si le délai est significatif par rapport à la période d’horloge, dessinez la transition avec une pente ou indiquez explicitement la valeur du délai. Cette représentation visuelle aide les validateurs à repérer les goulets d’étranglement potentiels avant la fabrication.

6. Ignorer les risques de métastabilité 🌌

La métastabilité se produit lorsque la bascule reçoit des données près du front d’horloge, ce qui la fait entrer dans un état indéfini pendant une durée imprévisible. Les diagrammes de temporisation captent rarement cet état de manière explicite, car il s’agit d’un mode de défaillance, et non d’un fonctionnement normal.

Toutefois, ignorer la possibilité de métastabilité dans les interfaces asynchrones constitue une erreur critique. Si un schéma montre un signal asynchrone qui se synchronise sur une horloge sans chaîne de synchronisation, cela implique un risque de perte ou de corruption des données.

- Identification : Recherchez les signaux qui traversent des domaines d’horloge sans synchronisation appropriée.

- Documentation : Indiquez où la métastabilité représente un risque connu et comment elle est atténuée.

- Visualisation : Utilisez des lignes pointillées pour indiquer les frontières asynchrones.

Même si le système est conçu pour gérer la métastabilité, le schéma doit refléter les étapes de synchronisation. Cela garantit que l’équipe de vérification sait tester ces conditions spécifiques.

7. Glissements de signal et aléas ⚡

Les glissements sont des impulsions transitoires qui surviennent en raison de délais de propagation inégaux dans des chemins parallèles. Ils peuvent provoquer un déclenchement erroné de la logique si leur existence n’est pas prise en compte dans l’analyse du temps.

Une erreur courante consiste à dessiner des signaux propres et stables là où des glissements sont physiquement inévitables. Par exemple, dans un multiplexeur qui bascule entre des entrées, la sortie pourrait brièvement clignoter avant de se stabiliser. Si le schéma montre une transition lisse, la logique en aval pourrait ne pas être conçue pour filtrer ces glissements.

Mettez en évidence les zones potentielles de danger dans le schéma. Utilisez des annotations pour avertir qu’un signal spécifique peut présenter un comportement transitoire pendant les changements d’état. Cela informe la stratégie de test afin d’inclure des scénarios de détection de glissements.

8. Manque de contexte pour les signaux de contrôle 🔌

Les signaux de données sont inutiles sans le contexte fourni par les signaux de contrôle tels que l’activation, la réinitialisation ou la sélection de puce. Un schéma qui se concentre uniquement sur les lignes de données omet souvent les conditions nécessaires pour que ces données soient valides.

Par exemple, un bus de données pourrait afficher des valeurs valides, mais si le signal « Écriture active » n’est pas indiqué comme actif pendant cette fenêtre, les données sont effectivement ignorées. À l’inverse, si le signal « Écriture active » est actif mais que les données sont invalides, le système écrit des données inutiles.

- Inclure le contrôle : Affichez toujours les signaux de contrôle aux côtés des signaux de données.

- Définir la validité : Utilisez un indicateur « Valide » ou une notation similaire pour indiquer quand les données sont fiables.

- Conditions d’état : Indiquez clairement l’état des signaux de contrôle (actif haut vs. actif bas).

La complétude est essentielle. Un diagramme temporel qui manque du contexte des signaux de contrôle est souvent à l’origine de confusion pendant le débogage. Assurez-vous que la relation entre les signaux de contrôle et les données soit visuellement explicite.

9. Mauvaise utilisation des annotations et de la légende 📝

Même un schéma parfaitement exact peut être mal compris s’il manque d’annotations appropriées. Les symboles, abréviations et légendes doivent être cohérents et expliqués.

Les erreurs courantes d’annotation incluent :

- Utiliser des étiquettes génériques comme « Signal A » au lieu de noms descriptifs.

- Omettre d’expliquer le sens de styles de ligne spécifiques (plein vs. pointillé).

- Omettre la définition du niveau actif (actif haut vs. actif bas).

Une section de légende dédiée doit faire partie de chaque diagramme temporel. Elle définit chaque symbole, style de ligne et abréviation utilisé. Cela réduit la charge cognitive du lecteur et garantit que tout le monde interprète le schéma de la même manière.

10. Liste de vérification et de revue ✅

Avant de finaliser un diagramme de timing, une revue systématique est nécessaire. Utilisez la liste de contrôle suivante pour valider l’exactitude et la clarté de votre travail.

| Élément à vérifier | Critères de réussite |

|---|---|

| Échelle de temps | Unités cohérentes et règle claire fournie |

| Front d’horloge | Front actif clairement indiqué pour toutes les horloges |

| Préparation/Conservation | Fenêtres définies pour les signaux synchrones |

| Propagation | Délais pris en compte dans les chemins critiques |

| Signaux de contrôle | Signaux d’activation/réinitialisation affichés avec les données |

| Légendes | Tous les symboles et abréviations expliqués |

| Traversée de domaine | Points de CDC identifiés et marqués |

Mettre régulièrement à jour cette liste de contrôle garantit qu’aucune erreur courante ne passe inaperçue. Elle agit comme une barrière de qualité pour la documentation avant qu’elle n’atteigne l’équipe d’ingénierie.

11. Clarté visuelle et conception de mise en page 🎨

La mise en page d’un diagramme de timing influence la facilité avec laquelle les erreurs sont détectées. Les diagrammes surchargés avec des signaux superposés sont sujets à des malentendus. L’alignement vertical des signaux liés aide l’œil à suivre les relations entre les événements.

Suivez ces principes de mise en page :

- Regrouper les signaux :Garder les signaux liés (comme l’adresse et les données) proches les uns des autres.

- Aligner les bords :Assurez-vous que les fronts d’horloge sont alignés verticalement sur toutes les voies.

- Espacer :Laissez suffisamment d’espace blanc pour éviter la superposition des signaux.

- Codage par couleur :Utilisez des couleurs différentes pour les différents domaines d’horloge si disponible (bien que le noir et blanc soit la norme pour l’impression).

Une mise en page propre réduit l’effort cognitif nécessaire pour interpréter le diagramme. Cela facilite la détection rapide des anomalies et des violations de timing.

12. Contraintes du monde réel vs. Simulation 🖥️

Les diagrammes de temporisation dérivés uniquement de la simulation ne reflètent pas nécessairement les réalités physiques. Les outils de simulation supposent souvent des conditions idéales, telles qu’une capacité parasite nulle et un routage parfait.

Lors de la traduction des résultats de simulation en documentation, les ingénieurs doivent tenir compte des variations de fabrication. Les coins Process, Voltage et Temperature (PVT) peuvent modifier les marges de temporisation. Un diagramme ne montrant que des valeurs nominales pourrait être insuffisant pour une conception robuste.

- Pire cas :Prenez en compte le coin de processus le plus lent pour l’analyse de temporisation.

- Meilleur cas :Prenez en compte le coin de processus le plus rapide pour l’analyse du temps de maintien.

- Marge :Ajoutez des marges de sécurité au diagramme pour tenir compte des variations PVT.

La documentation doit refléter la robustesse de la conception, et non seulement les résultats de simulation dans le meilleur des cas. Cela prépare l’équipe aux scénarios de déploiement réels.

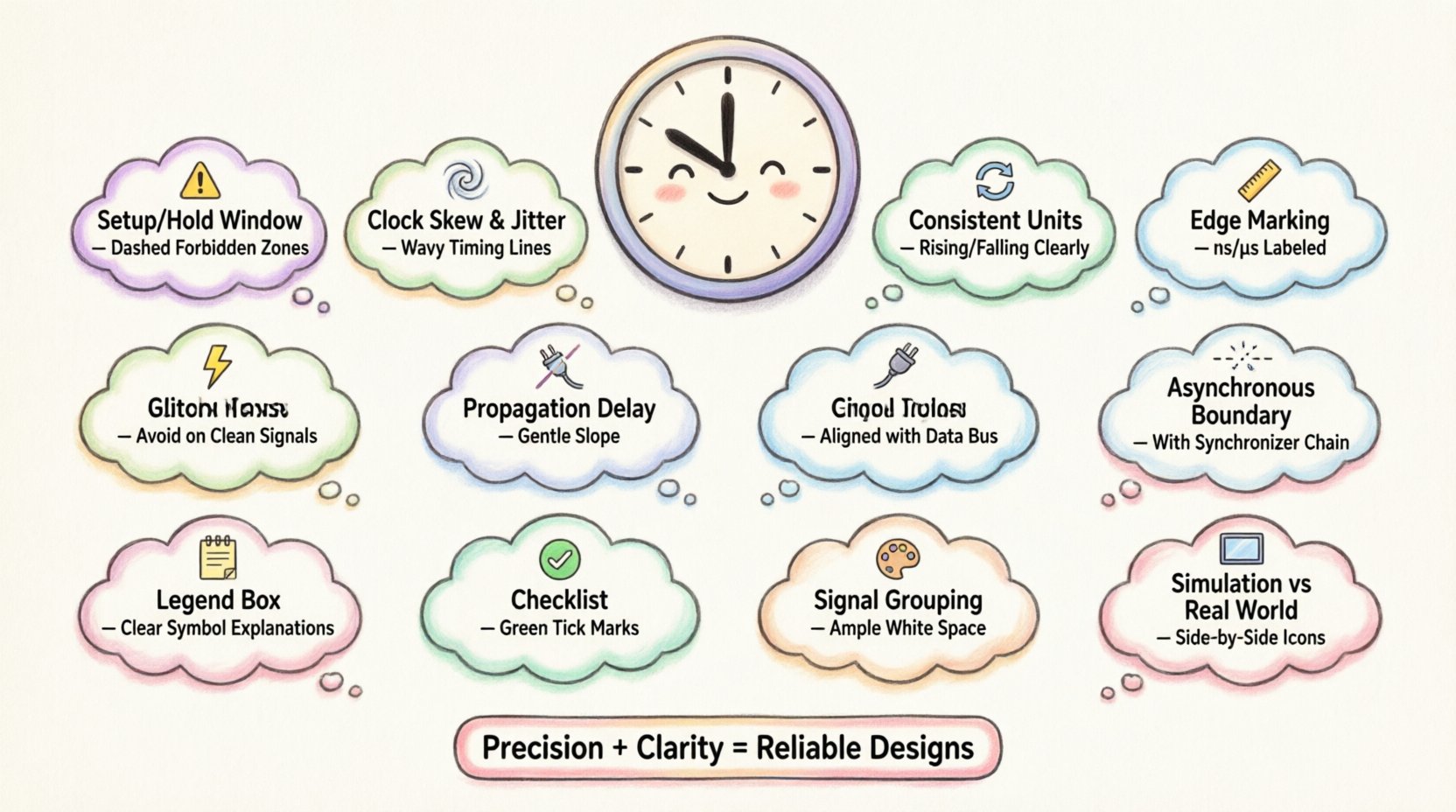

Réflexions finales sur la précision du temporisation 🛡️

Les diagrammes de temporisation sont autant des outils de communication que des spécifications techniques. Leur objectif principal est de transmettre clairement l’intention et les contraintes à tous les intervenants. En évitant des erreurs courantes telles que négliger le décalage, ignorer les déclenchements sur front ou omettre les signaux de contrôle, les ingénieurs assurent que l’intention de conception est préservée de la documentation au matériel.

La précision de ces diagrammes évite les re-spins coûteux et les cycles de débogage. Un diagramme bien structuré sert de source unique de vérité tout au long du cycle de vie du projet. Investissez le temps nécessaire pour effectuer correctement l’analyse de temporisation, et l’implémentation en aval se déroulera sans heurt.

Souvenez-vous qu’un diagramme de temporisation est un document vivant. Il doit être mis à jour chaque fois que la conception change. Maintenir l’intégrité des informations de temporisation garantit que le système reste fiable tout au long de sa durée de vie opérationnelle. Concentrez-vous sur la précision, la clarté et la complétude pour livrer des conceptions numériques robustes.