Les diagrammes de temporisation sont la colonne vertébrale de la conception des systèmes numériques. Ils servent de contrat visuel entre la logique, le matériel et le logiciel, définissant précisément à quel moment les signaux doivent changer d’état. Toutefois, malgré leur omniprésence dans le domaine du génie, un brouillard persistant d’erreurs de compréhension entoure la manière dont ces diagrammes sont créés, interprétés et utilisés. De nombreux professionnels les considèrent comme des illustrations statiques plutôt que comme des représentations dynamiques du comportement du système.

Ce guide vise à dissiper le flou. Nous analyserons les idées reçues courantes, explorerons les réalités techniques de la propagation des signaux et établirons un cadre pour créer une documentation de temporisation précise. En distinguant le vrai du faux, les ingénieurs pourront réduire le temps de débogage et améliorer la fiabilité du système.

Qu’est-ce qu’un diagramme de temporisation ? 🤔

Un diagramme de temporisation est une représentation graphique du comportement des signaux dans un circuit numérique au fil du temps. Contrairement à un schéma, qui montre les connexions, un diagramme de temporisation illustre les relations de causalité et temporelles. Il représente les niveaux de signal (haut, bas ou flottant) en fonction d’une chronologie, permettant aux concepteurs de vérifier que les données sont stables au moment prévu.

Les caractéristiques principales incluent :

- Axe du temps :Il court généralement horizontalement, représentant l’évolution des événements.

- Lignes de signal :Des lignes verticales représentant des fils spécifiques, des bus ou des états logiques.

- Bords :Des transitions du bas vers le haut (montante) ou du haut vers le bas (descendante).

- Étiquettes :Des annotations indiquant les temps de préparation, les temps de maintien ou les délais.

Sans une compréhension claire de ces composants, le diagramme devient une source de confusion plutôt qu’une source de clarté.

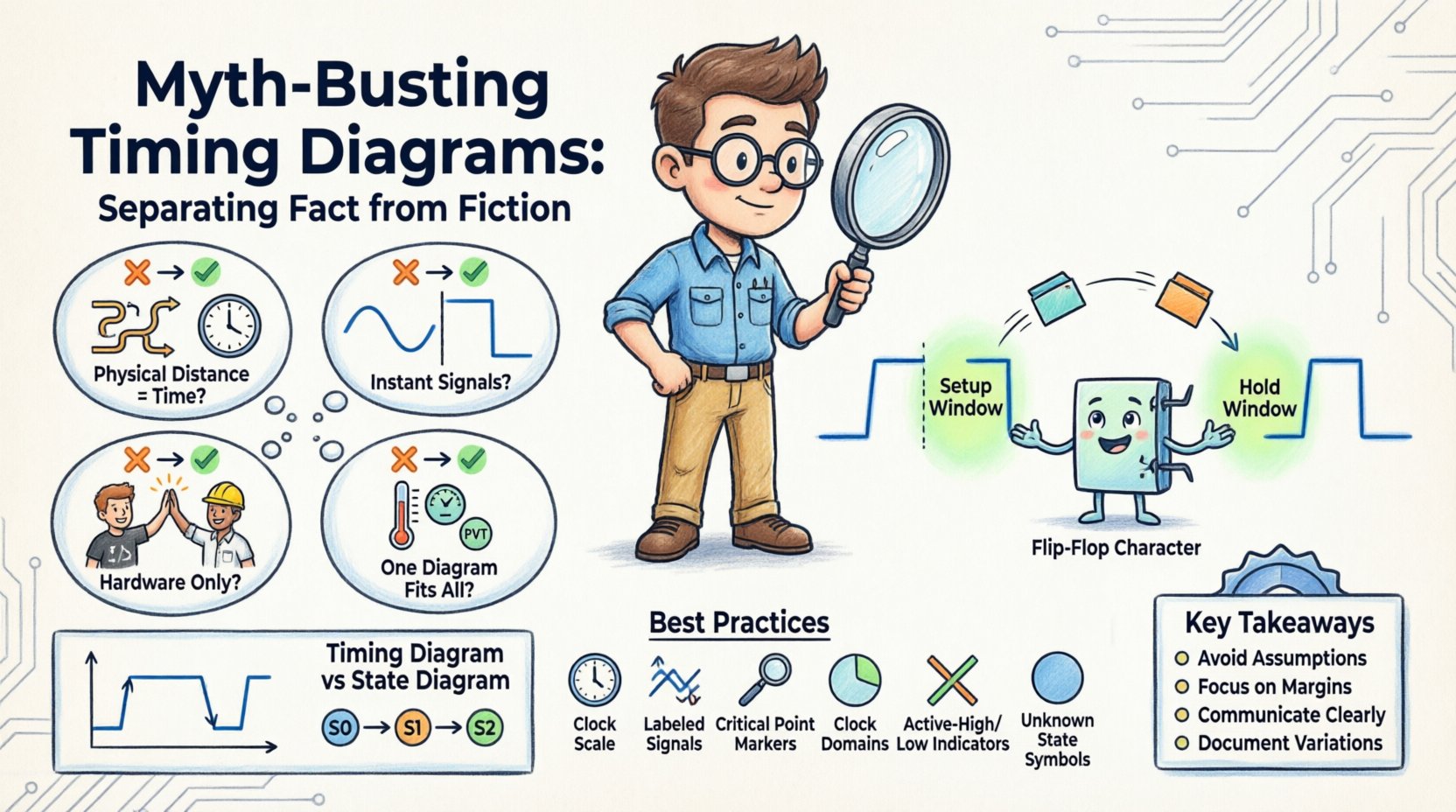

Mythes courants sur les diagrammes de temporisation 🚫

Pour améliorer la qualité de la conception, nous devons d’abord identifier les croyances erronées qui entraînent des erreurs. Voici les mythes les plus répandus dans les cercles techniques.

Mythe 1 : Les diagrammes de temporisation montrent une distance physique exacte 📏

Le mythe :Les ingénieurs supposent souvent que la distance horizontale entre deux bords sur un diagramme correspond directement à la longueur physique de la piste sur une carte PCB.

Le fait :Les diagrammes de temporisation représentent le temps logique ou électrique, et non l’espace physique. Bien que la longueur de la piste affecte le délai de propagation, le diagramme se concentre sur le résultatde ce délai, et non sur la géométrie elle-même. Un délai de 1 nanoseconde peut représenter une piste de 15 cm sur une carte FR4 ou une piste de 10 cm sur une piste en cuivre avec des constantes diélectriques différentes. Le diagramme abstrait le support physique afin de se concentrer sur la fenêtre de temporisation.

- La longueur physique détermine le délai, mais le diagramme montre la valeur du délai.

- La complexité du routage est masquée ; seul le résultat final compte.

- Supposer une échelle 1:1 entre le temps et la distance entraîne des erreurs de disposition.

Mythe 2 : Les transitions de signal sont instantanées ⚡

Le mythe :Dans de nombreux diagrammes, des lignes verticales indiquent qu’un signal change d’état immédiatement.

Le fait :Aucun signal physique ne change d’état instantanément. Il y a toujours une durée de montée et une durée de descente. Lorsqu’un schéma montre une arête verticale, cela représente une transition rapide par rapport à la période d’horloge, mais pas nulle. Ignorer les durées de transition peut entraîner des problèmes d’intégrité du signal, tels que des oscillations ou des interférences, qui ne sont pas visibles sur les schémas idéalisés.

- La durée de montée est la durée nécessaire pour passer de 10 % à 90 % de la tension.

- Les schémas simplifient souvent cela pour plus de lisibilité, mais la simulation doit en tenir compte.

- Les conceptions à haute vitesse exigent une modélisation explicite des pentes de transition.

Mythe 3 : Les diagrammes de temporisation ne concernent que les ingénieurs matériel.

La fiction :Les développeurs logiciels et les architectes système ignorent souvent les diagrammes de temporisation, en supposant qu’ils sont sans rapport avec la logique du code.

Le fait :Le logiciel doit respecter les contraintes de temporisation matérielles. Les interruptions, les transferts DMA et l’entrée/sortie mappée en mémoire dépendent toutes du timing établi par le matériel. Si un pilote tente de lire des données avant que le matériel ne signale le signal « Prêt », une erreur de bus se produit. Les diagrammes de temporisation sont essentiels pour la communication entre disciplines.

- Les interruptions logicielles doivent être synchronisées avec les cycles d’horloge matériel.

- Les fenêtres d’accès à la mémoire sont définies par les spécifications de temporisation.

- Les équipes matérielles et logicielles ont besoin d’une compréhension commune du calendrier.

Mythe 4 : Un seul schéma convient à tous les contextes

La fiction :Un seul diagramme de temporisation peut décrire un système entier, indépendamment des conditions d’exploitation.

Le fait :Le temporisation varie selon la température, la tension et les variations de processus (PVT). Un schéma établi pour des conditions nominales peut échouer aux extrêmes. Les concepteurs doivent tenir compte des scénarios les plus défavorables. Un schéma montrant un comportement optimal est souvent moins utile qu’un schéma mettant en évidence les limites d’exploitation.

- Le délai maximal détermine la période d’horloge minimale.

- La température affecte la résistance et la capacité.

- Les variations de processus modifient les vitesses de commutation des transistors.

Approfondissement : Temps de préparation et temps de maintien ⏱️

Comprendre les violations de temporisation est crucial. Deux concepts précis dominent l’analyse de l’intégrité des données : le temps de préparation et le temps de maintien. Ce sont souvent la source des bogues les plus insidieux dans les systèmes numériques.

Temps de préparation (Tsu)

Le temps de préparation est la durée minimale avantun front d’horloge pendant laquelle les données doivent être stables. Si les données changent trop près du front d’horloge, le bascule réceptrice peut ne pas capturer la bonne valeur.

- Il garantit que les données sont stabilisées avant que la fenêtre de capture ne se ferme.

- Les violations provoquent une métastabilité ou des états logiques incorrects.

- Le délai du chemin doit être inférieur à la période d’horloge moins le temps de préparation.

Temps de maintien (Th)

Le temps de maintien est la durée minimale aprèsun bord d’horloge pendant laquelle les données doivent rester stables. Si les données changent trop tôt après le bord d’horloge, le bascule peut perdre la valeur précédemment capturée.

- Il garantit que les données restent stables suffisamment longtemps pour être verrouillées.

- Les violations sont souvent plus difficiles à corriger que les violations de préparation.

- Le délai du chemin doit être supérieur à la durée exigée pour le temps de maintien.

Scénarios de violations de temporisation

Lors de l’analyse d’un diagramme de temporisation, recherchez les motifs suivants :

- Violation de préparation : Le signal de données est encore en cours de changement lorsque le bord d’horloge arrive.

- Violation de maintien : Le signal de données change immédiatement après le bord d’horloge.

- Glitch : Une impulsion brève qui se situe dans la fenêtre de préparation/maintien mais qui n’est pas une transition valide.

Diagramme de temporisation vs. Diagramme d’état 🔄

La confusion survient souvent entre les diagrammes de temporisation et les diagrammes d’état. Bien qu’ils décrivent tous deux le comportement du système, ils répondent à des questions différentes. Un diagramme d’état montre ce quele système fait (flux logique), tandis qu’un diagramme de temporisation montre quandcela se produit (flux temporel).

| Fonctionnalité | Diagramme de temporisation | Diagramme d’état |

|---|---|---|

| Focus principal | Temps et niveaux de signal | Logique et flux de contrôle |

| Représentation des axes | Horizontal = Temps | Horizontal = États logiques |

| Meilleur pour | Intégrité du signal, synchronisation | Conception d’algorithmes, logique d’automate à états finis |

| Complexité | Haute précision temporelle | Haute branche logique |

| Détail du signal | Affiche les niveaux de tension (Haut/Bas) | Affiche des états abstraits (Inactif/Exécution) |

Utiliser le bon diagramme pour la tâche évite les malentendus. Un automate à états peut être conçu sans diagramme temporel, mais une interface de bus à haute vitesse ne peut pas.

Meilleures pratiques pour créer des diagrammes précis ✅

Pour garantir que votre documentation soit efficace, suivez ces directives. La précision dans la documentation réduit l’ambiguïté lors de l’implémentation.

- Définissez l’échelle du temps : Précisez toujours les unités (ns, µs, cycles). Si vous utilisez des cycles, définissez la fréquence d’horloge.

- Nommez chaque signal : N’utilisez pas de noms génériques comme « Signal 1 ». Utilisez des noms descriptifs comme « CLK_IN » ou « DATA_VALID ».

- Marquez les points critiques : Mettez en évidence les fenêtres de setup et de hold de manière explicite avec un hachurage ou des annotations.

- Incluez les domaines d’horloge : Si plusieurs horloges existent, distinguez-les clairement. Montrez la relation entre les horloges asynchrones si cela s’applique.

- Indiquez le niveau actif haut/bas : Précisez si un état actif est haut (1) ou bas (0) pour éviter les erreurs de polarité.

- Indiquez les états inconnus : Utilisez X ou Z pour représenter des états non définis ou en état de haute impédance plutôt que de les laisser vides.

Gestion des signaux asynchrones 🔄

L’un des aspects les plus complexes des diagrammes temporels est la gestion des signaux asynchrones. Ce sont des signaux non synchronisés avec l’horloge principale du système. Ils introduisent une incertitude qui doit être gérée.

- Métastabilité : Lorsqu’un signal asynchrone arrive près d’une transition d’horloge, la bascule peut entrer dans un état métastable. Elle se stabilisera finalement sur 0 ou 1, mais le temps nécessaire est imprévisible.

- Synchronisateurs : Utilisez des chaînes de bascules pour résoudre la métastabilité. Les diagrammes temporels doivent montrer que la région métastable se stabilise avant la prochaine transition d’horloge.

- Échanges de signaux (handshaking) : Des protocoles comme I2C ou SPI utilisent des échanges de signaux asynchrones. Le diagramme temporel doit montrer les états d’attente où le maître attend le esclave.

Application réelle : Débogage d’une condition de course 🐞

Imaginez un scénario où un bus de données n’est pas correctement lu. Le système bloque occasionnellement. Une analyse du diagramme temporel révèle le problème.

- Observation : Le signal « Ready » est activé légèrement après l’impulsion de lecture.

- Vérification du diagramme : Le diagramme temporel montre que le front du signal « Ready » tombe dans la fenêtre de préparation de l’impulsion de lecture.

- Conclusion : Les données sont lues avant qu’elles ne soient valides.

- Solution : Ajustez la logique pour retarder l’impulsion de lecture ou allonger l’impulsion « Ready ».

Cet exemple met en évidence l’importance de visualiser le déroulement temporel. Sans le diagramme, la condition de course reste cachée dans la logique du code.

Outils et méthodes d’analyse 🔍

Bien que les noms spécifiques de logiciels ne soient pas au centre de l’attention, les méthodologies d’analyse restent constantes. L’ingénierie moderne repose sur la simulation et les visualisateurs d’ondes pour valider les diagrammes temporels.

- Simulation : Exécutez des bancs de test pour générer des signaux correspondant à l’intention du design.

- Analyse statique des temps (STA) : Calculez les délais sans simulation pour vérifier les violations sur toutes les voies.

- Débogage matériel : Utilisez des oscilloscopes pour capturer des signaux du monde réel et les comparer au diagramme théorique.

- Contrôle de version : Gardez les diagrammes temporels sous contrôle de version. Les modifications matérielles exigent souvent des mises à jour des spécifications temporelles.

L’impact du jitter et du décalage (skew) 📉

Les diagrammes temporels sont souvent tracés avec des lignes parfaites et droites. La réalité est plus chaotique. Le jitter et le décalage sont des sources de bruit qui affectent la précision temporelle.

- Jitter :Variations dans le timing des fronts d’un signal. Le jitter d’horloge fait bouger la fenêtre d’échantillonnage.

- S skew :La différence de temps d’arrivée du même signal d’horloge à différents points du circuit.

- Impact :Les deux réduisent la marge de timing. Un diagramme de timing devrait idéalement montrer la marge, et non seulement le front idéal.

Résumé des points clés 📝

Les diagrammes de timing sont bien plus que des dessins ; ce sont des spécifications de comportement. En comprenant les mythes et les faits qui les entourent, les ingénieurs peuvent concevoir des systèmes plus robustes.

- Évitez les hypothèses :Ne supposez pas de transitions instantanées ni de synchronisation parfaite.

- Concentrez-vous sur les marges :Les temps de setup et de hold sont les buffers de sécurité qui préviennent les échecs.

- Communiquez clairement :Utilisez des diagrammes pour combler le fossé entre les équipes matérielles et logicielles.

- Documentez les variations :Reconnaissez que le timing évolue selon l’environnement et le processus.

Quand vous regardez un diagramme de timing, voyez le temps. Voyez les contraintes. Voyez la fiabilité. Cette perspective transforme une image statique en un outil puissant pour l’excellence en ingénierie.