Dans le monde de l’électronique numérique et de l’ingénierie matérielle, la communication entre les composants repose sur une coordination précise. Sans une compréhension claire du moment où les signaux changent d’état, les systèmes échouent. Le diagramme de timing sert de plan directeur pour cette coordination. Il visualise la relation entre les signaux au fil du temps, révélant si les données sont valides, stables et prêtes à être traitées. Ce guide aborde les questions fondamentales auxquelles les ingénieurs et les étudiants sont confrontés lors de l’analyse de ces outils visuels essentiels.

Que vous conceviez une interface de microcontrôleur, débogiez un protocole de communication ou étudiez la logique numérique, comprendre les aspects temporels de votre conception est impératif. Cet article explore l’anatomie des diagrammes de timing, explique les paramètres clés et répond aux questions fréquentes concernant l’intégrité du signal et la synchronisation.

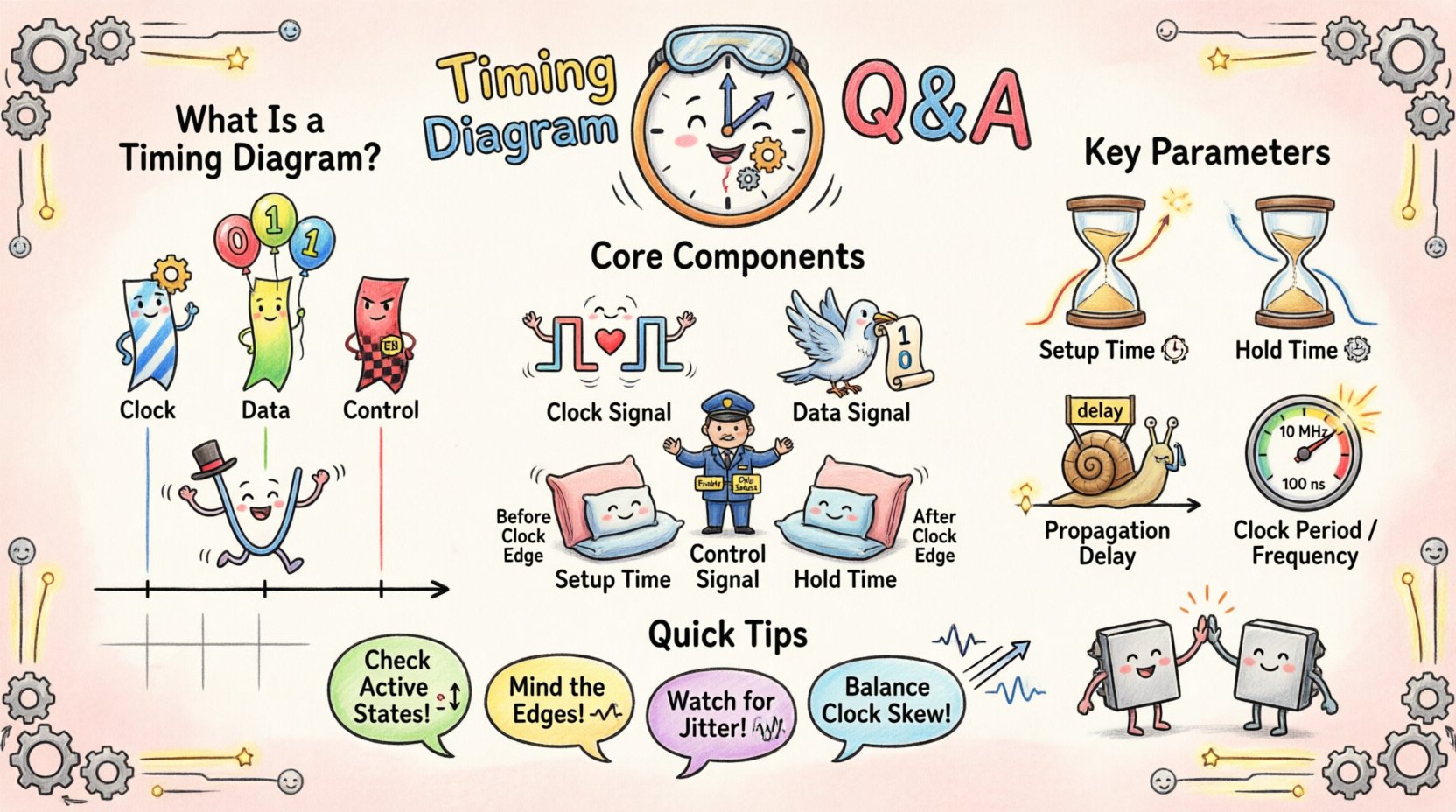

Qu’est-ce qu’un diagramme de timing ? 📊

Un diagramme de timing est une représentation graphique de la séquence des événements dans un système. Il représente les niveaux des signaux en fonction d’un axe horizontal du temps. Contrairement à un schéma logique, qui montre les connexions, un diagramme de timing montre le comportement. Il vous permet de voir si un signal passe à haut ou à bas avant ou après un autre signal. Ce contexte visuel est essentiel pour vérifier qu’un récepteur dispose de suffisamment de temps pour lire les données avant l’arrivée de l’impulsion suivante de l’horloge.

Les caractéristiques clés incluent :

- Axe du temps : Généralement orienté horizontalement de gauche à droite.

- Lignes de signal :Lignes horizontales représentant des fils individuels ou des bus de données.

- Niveaux logiques :Les états haut (1) et bas (0) sont représentés par des plateaux de tension distincts.

- Bords :Lignes verticales indiquant la transition d’un état à un autre.

Composants essentiels d’un diagramme de timing 🧩

Pour lire efficacement ces diagrammes, vous devez identifier les éléments standards qui composent le signal. Chaque élément joue un rôle spécifique dans la synchronisation du système.

| Composant | Description | Indicateur visuel |

|---|---|---|

| Signal d’horloge | Fournit le rythme cardiaque du système. Les autres signaux sont souvent échantillonnés par rapport à celui-ci. | Motif régulier de onde carrée |

| Signal de données | Transporte les informations réelles qui sont transférées. | Transitions irrégulières basées sur l’entrée |

| Signal de contrôle | Gère le flux de données (par exemple, Activer, Sélection de puce, Écrire). | Pulsations actives haut ou actives bas |

| Temps de préparation | La durée pendant laquelle les données doivent être stables avant une impulsion d’horloge. | Distance horizontale avant le bord |

| Temps de maintien | La durée pendant laquelle les données doivent rester stables après un front d’horloge. | Distance horizontale après le bord |

Comprendre les paramètres clés de temporisation ⚙️

Les paramètres de temporisation définissent les contraintes dans lesquelles un circuit numérique fonctionne correctement. Leur violation entraîne souvent un comportement imprévisible. Ci-dessous figurent les définitions et les implications des métriques les plus critiques.

1. Temps de préparation ⏳

Le temps de préparation est la durée minimale pendant laquelle le signal de données doit rester stable avant le front déclencheur du signal d’horloge. Si les données changent trop près du front d’horloge, le bascule peut ne pas capturer correctement la valeur. Ce paramètre est souvent la contrainte la plus critique dans les conceptions à haute vitesse, car il détermine la fréquence maximale de fonctionnement.

2. Temps de maintien ⏳

Le temps de maintien est la durée minimale pendant laquelle le signal de données doit rester stable après le front déclencheur du signal d’horloge. Contrairement au temps de préparation, le temps de maintien est généralement indépendant de la fréquence d’horloge. Il dépend du délai interne de la bascule et du délai de propagation externe du chemin de données.

3. Délai de propagation ⏳

Il s’agit du temps nécessaire à un signal pour voyager depuis l’entrée d’un composant jusqu’à sa sortie. Ce délai varie en fonction de la température, de la tension et des tolérances de fabrication. Dans un diagramme de temporisation, cela apparaît comme un retard entre un changement dans un signal et le changement correspondant dans un autre.

4. Période et fréquence d’horloge ⏳

La période d’horloge est la durée d’un cycle complet du signal d’horloge. La fréquence est l’inverse de la période. Une période plus courte signifie une fréquence plus élevée, ce qui permet un traitement plus rapide, mais réduit la fenêtre de stabilité du signal.

Questions fréquemment posées ❓

Les ingénieurs rencontrent souvent des scénarios spécifiques qui provoquent de la confusion. Voici des réponses détaillées aux questions les plus pressantes concernant l’analyse de temporisation.

Q : Que se passe-t-il si le temps de préparation est violé ? 🛑

Lorsque la condition de temps de préparation n’est pas respectée, la bascule entre dans un état connu sous le nom de métastabilité. Dans cet état, la sortie ne se stabilise pas immédiatement sur un niveau logique haut ou bas valide. Au contraire, elle peut osciller ou rester à un niveau de tension intermédiaire pendant une durée imprévisible. Cela peut entraîner une lecture incorrecte par la logique en aval, provoquant des erreurs système ou des plantages. Dans les cas graves, la métastabilité peut se propager à travers tout le circuit, entraînant une panne fonctionnelle difficile à diagnostiquer.

Q : Comment gérer le décalage d’horloge ? 🔄

Le décalage d’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents. Cela peut survenir en raison de longueurs de parcours variables ou de différences de charge. Pour gérer le décalage :

- Équilibrage du routage : Assurez-vous que les pistes d’horloge sont routées avec des longueurs et des largeurs similaires.

- Utilisation de tampons : Utilisez des tampons d’horloge pour alimenter plusieurs charges de manière équilibrée.

- Marges de temporisation : Concevez le système avec une marge suffisante dans les temps de préparation et de maintien pour absorber les petites variations de décalage.

Q : Quelle est la différence entre la temporisation synchrone et la temporisation asynchrone ? ⚖️

Dans synchrone systèmes, toutes les opérations sont synchronisées par un seul signal d’horloge. Les diagrammes temporels de ces systèmes montrent des fronts d’horloge réguliers et répétés. Dans asynchrone systèmes, les signaux déclenchent des actions sans horloge globale. Les diagrammes temporels de ces systèmes montrent des transitions déclenchées par des événements, souvent avec une plus grande variation des intervalles entre les signaux. Les conceptions asynchrones sont plus difficiles à analyser, mais peuvent être plus efficaces en énergie dans certains applications à faible consommation.

Q : Comment le jitter affecte-t-il un diagramme temporel ? 📉

Le jitter est la variation à court terme d’un signal par rapport à sa position idéale dans le temps. Dans un diagramme temporel, cela se manifeste par des fronts du signal d’horloge qui apparaissent légèrement plus tôt ou plus tard qu’ils ne devraient. Un jitter excessif réduit la fenêtre effective de capture des données. Il réduit effectivement les marges de setup et de hold, augmentant ainsi le risque de violations temporelles. Les interfaces à haute vitesse nécessitent un contrôle strict du jitter pour préserver l’intégrité des données.

Q : Puis-je lire des diagrammes temporels sans horloge ? 🕵️

Oui, mais cela nécessite une approche différente. Les protocoles asynchrones comme I2C ou UART n’utilisent pas toujours une ligne d’horloge partagée. À la place, ils reposent sur des débits prédéfinis ou des signaux d’échange. Dans ces diagrammes, vous devez examiner les largeurs d’impulsion et le temps entre les transitions pour déduire le débit de données. Par exemple, dans UART, la durée du bit de départ définit le timing des bits de données suivants.

Lecture et interprétation des formes d’onde 🔍

Interpréter un diagramme temporel nécessite une approche systématique. Examiner les lignes au hasard conduit souvent à manquer des détails. Suivez ce processus pour une analyse précise.

- Identifiez la référence : Trouvez le signal d’horloge ou le signal de contrôle principal. Tous les autres délais sont relatifs à celui-ci.

- Vérifiez les états actifs : Déterminez si les signaux sont actifs haut ou actifs bas. Une impulsion basse peut signifier « activé », tandis qu’une impulsion haute signifie « désactivé ». Cela est souvent indiqué par un symbole de bulle sur le nom de la broche dans les schémas.

- Analysez l’alignement des fronts : Examinez attentivement où les fronts des données s’alignent avec les fronts de l’horloge. Les données devraient idéalement changer lorsque l’horloge est stable (par exemple, en phase basse) et rester stables pendant l’edge actif.

- Suivez les dépendances : Suivez la relation de cause à effet. Si le signal A déclenche le signal B, il doit y avoir un délai clair entre eux correspondant au délai de propagation.

- Vérifiez les largeurs d’impulsion : Assurez-vous que les impulsions actives sont assez larges pour que le composant récepteur puisse les détecter. Une impulsion trop étroite peut être filtrée comme du bruit.

Erreurs courantes dans l’interprétation des diagrammes ❌

Même les ingénieurs expérimentés peuvent mal interpréter les diagrammes s’ils négligent des détails précis. Évitez ces pièges courants.

- Ignorer les niveaux logiques : Supposer que tous les signaux sont actifs haut sans vérification. Vérifiez toujours la fiche technique ou le schéma.

- Ne pas tenir compte des délais de propagation : Supposer que les signaux changent instantanément. Les composants du monde réel ont des temps de réponse finis.

- Lire incorrectement les échelles de temps : Oublier de noter l’unité de temps (nanosecondes contre microsecondes). Un signal qui semble stable à un zoom lent peut montrer des anomalies à un zoom rapide.

- Ne pas tenir compte des états d’alimentation : Les diagrammes temporels changent souvent lorsque un dispositif passe en mode veille. Assurez-vous que vous regardez la séquence temporelle active.

Stratégies pour une analyse précise 🛠️

Pour garantir que votre analyse de temporisation soit robuste, adoptez ces stratégies. Ces méthodes aident à maintenir la cohérence et à réduire les risques d’erreur.

- Utilisez les lignes de grille :Alignez vos curseurs ou repères avec les lignes de grille du diagramme pour mesurer avec précision les intervalles de temps.

- Documentez vos hypothèses :Notez la fréquence d’horloge supposée et les niveaux logiques avant de commencer l’analyse. Cela évite toute confusion ultérieure.

- Croisez les informations :Comparez le diagramme de temporisation avec la logique de la machine à états. Chaque transition d’état doit correspondre à un événement de temporisation.

- Simulez des variations :Considérez les scénarios les plus défavorables. Que se passe-t-il si la température augmente et que les délais s’allongent ? Et si la tension baisse et que la puissance de conduite diminue ?

- Concentrez-vous sur les chemins critiques :Identifiez le chemin le plus long dans votre logique. Ce chemin détermine la vitesse d’horloge maximale du système. Priorisez l’analyse de temporisation pour ces trajets spécifiques.

L’impact des violations de temporisation ⚠️

Comprendre pourquoi la temporisation est importante est crucial. Lorsqu’une violation de temporisation se produit, le comportement physique du circuit change. La conséquence la plus courante est la corruption des données. Un registre pourrait capturer un « 1 » alors qu’il aurait dû capturer un « 0 ». Dans les protocoles de communication, cela entraîne des erreurs de cadencement ou des paquets perdus. Dans les systèmes de contrôle, cela peut entraîner des commandes incorrectes pour les actionneurs, pouvant entraîner des dommages physiques ou des risques de sécurité.

En outre, les violations de temporisation peuvent entraîner des défaillances intermittentes. Un système pourrait fonctionner parfaitement à température ambiante mais échouer lorsqu’il chauffe. Cela se produit parce que les délais de propagation augmentent avec la température. Concevoir avec des marges de temporisation suffisantes prend en compte ces variations environnementales.

Meilleures pratiques pour les diagrammes de temporisation 📝

Créer des diagrammes de temporisation clairs et précis est une compétence qui s’améliore avec la pratique. Suivez ces directives pour produire des diagrammes faciles à comprendre pour les autres.

- Tout étiqueter :Chaque ligne de signal doit avoir un nom clair. Évitez les étiquettes génériques comme « Signal 1 ».

- Utilisez une échelle constante :Maintenez une échelle de temps uniforme sur l’ensemble du diagramme, sauf si vous devez zoomer sur un événement spécifique.

- Mettez en évidence les événements critiques :Utilisez des couleurs différentes ou des lignes plus épaisses pour marquer les fenêtres de setup et de hold.

- Incluez des annotations :Ajoutez des notes textuelles pour expliquer des interactions complexes ou des contraintes spécifiques.

- Vérifiez avec les fiches techniques :Vérifiez toujours les paramètres de votre diagramme par rapport aux spécifications officielles des composants.

Considérations avancées : domaines d’horloge multiples 🌐

Les systèmes modernes utilisent souvent plusieurs domaines d’horloge. Par exemple, un processeur peut fonctionner à 2 GHz tandis qu’un contrôleur de mémoire fonctionne à 400 MHz. Les diagrammes de temporisation pour ces systèmes deviennent considérablement plus complexes. Vous devez tenir compte de :

- Échantillonnage entre horloges : Comment les données passent d’une fréquence à une autre.

- Tampons FIFO : Comment synchroniser le flux de données entre des horloges asynchrones.

- Synchronisation de la réinitialisation :Assurer que tous les domaines se réinitialisent de manière coordonnée afin d’éviter les incohérences d’état.

Lors de l’analyse de ces diagrammes, recherchez la logique de synchronisation, telles que les signaux d’échange ou les chaînes de synchronisation. Ces composants sont spécifiquement conçus pour combler en toute sécurité l’écart entre différents domaines de temporisation.

Conclusion : La précision est essentielle 🔑

Les diagrammes de temporisation sont bien plus que des images ; ce sont la preuve mathématique d’un système fonctionnel. Ils définissent les limites de fiabilité et de performance. En comprenant les composants fondamentaux, les paramètres et les pièges potentiels, vous pouvez concevoir des systèmes qui fonctionnent correctement dans des conditions réelles. Une attention portée aux temps de préparation, aux temps de maintien et aux délais de propagation distingue un prototype fonctionnel d’un produit prêt à la production. Une pratique continue de la lecture et de la création de ces diagrammes affinera votre intuition technique et améliorera vos résultats ingénierie.

Souvenez-vous qu’une transition représente toujours une histoire sur le flux d’information. Respectez le temps nécessaire à ce que l’information voyage, et vos conceptions résisteront à l’épreuve du temps.