Dans l’architecture complexe des systèmes numériques, comprendre précisément le moment où un signal change d’état est crucial. Les diagrammes temporels fournissent une représentation visuelle de l’évolution des signaux au fil du temps. Ce sont des outils essentiels pour les ingénieurs, développeurs et concepteurs qui doivent vérifier que les composants interagissent correctement. Sans ces aides visuelles, le débogage des communications asynchrones ou la vérification des domaines d’horloge devient un jeu de devinettes. Ce guide explore les mécanismes, les avantages et les applications des diagrammes temporels dans la conception de systèmes.

Qu’est-ce qu’un diagramme temporel ? ⚙️

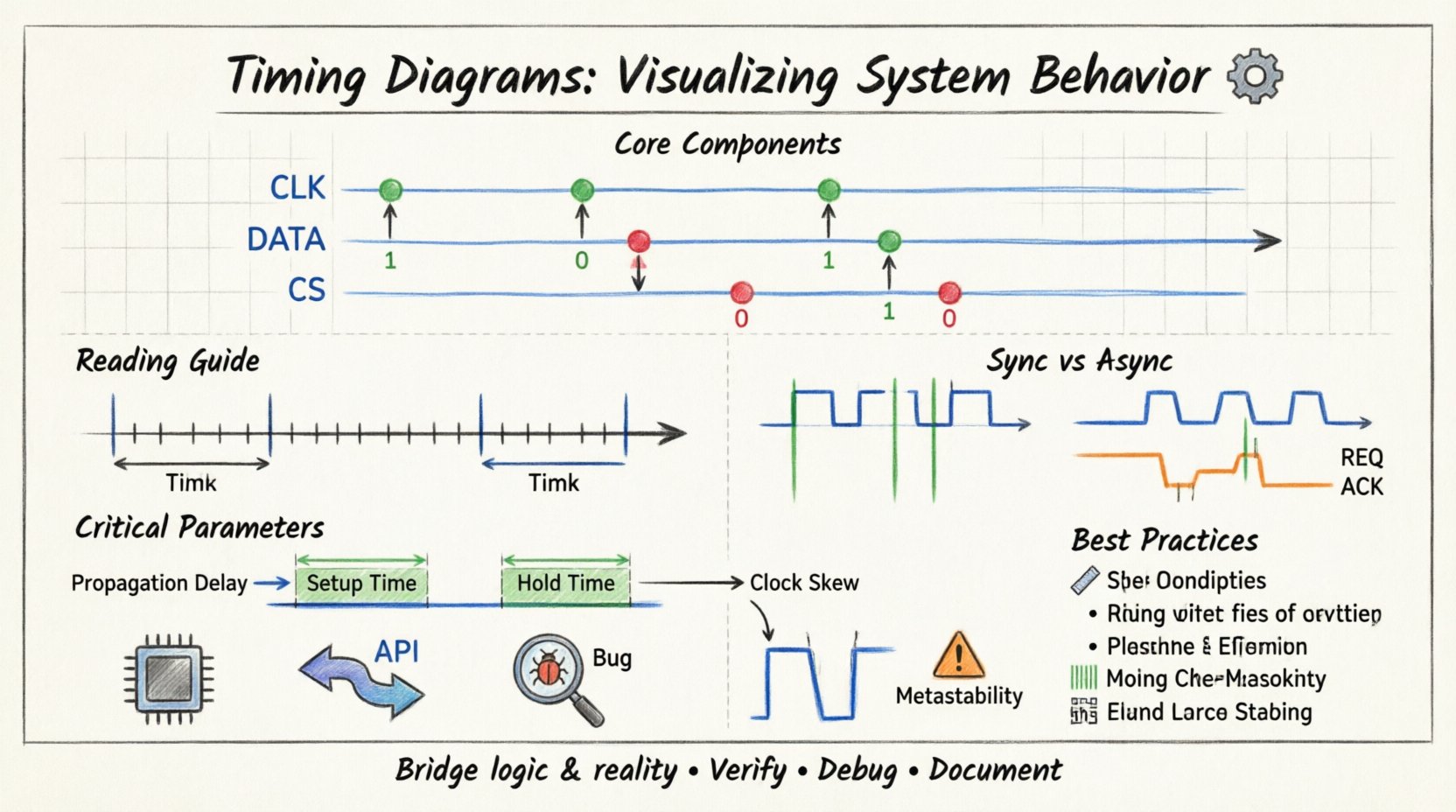

Un diagramme temporel est un graphique qui affiche le comportement des signaux sur une période donnée. Il représente l’état logique des signaux en fonction d’une chronologie. Contrairement aux schémas de circuits, qui montrent les connexions physiques, les diagrammes temporels se concentrent sur la relation temporelle entre les événements. Ils répondent à des questions telles que : le signal A change-t-il avant le signal B ? L’impulsion d’horloge est-elle suffisamment large ? Combien de temps faut-il à la donnée pour se stabiliser ?

Ces diagrammes sont fondamentaux dans :

- Vérification des protocoles matériels

- Documentation des interactions logiques logicielles

- Débogage des conditions de course

- Validation de l’alignement entre l’horloge et les données

Composants fondamentaux d’un diagramme temporel 🧩

Pour interpréter correctement un diagramme temporel, il faut comprendre ses éléments de base. Chaque diagramme se compose d’éléments spécifiques qui transmettent des informations sur le fonctionnement du système.

1. L’axe du temps 📏

L’axe horizontal représente le temps. Il s’écoule généralement de gauche à droite. L’échelle peut être absolue (nanosecondes, microsecondes) ou relative (cycles d’horloge). Dans les systèmes synchrones, le temps est souvent divisé en étapes discrètes correspondant aux fronts d’horloge.

2. Les lignes de signal 📡

Chaque ligne représente un signal, un fil ou un bus de données spécifique. Ces lignes sont étiquetées avec des noms tels queCLK, DATA, CS (Sélection de puce), ouRST (Réinitialisation). La position verticale de la ligne sépare les différents signaux afin d’éviter toute confusion.

3. Niveaux logiques 🟢🔴

Les signaux existent généralement dans des états discrets. En logique numérique, ces états sont haut (logique 1) et bas (logique 0). Les diagrammes temporels montrent les transitions entre ces états. Une transition du bas au haut est un front montant. Une transition du haut au bas est un front descendant.

4. Événements et transitions 🔄

Les événements sont des moments précis où un signal change d’état. Ils sont souvent marqués par des lignes verticales ou des flèches. Les événements importants incluent les fronts d’horloge, les verrous de données et les signaux d’acquittement. L’écart entre ces événements indique la durée.

Lecture efficace des diagrammes temporels 👁️

La lecture de ces diagrammes nécessite une approche systématique. Une mauvaise interprétation de la séquence des événements peut entraîner des erreurs de conception. Suivez ces principes pour garantir une précision absolue.

- De gauche à droite : Lisez toujours le chronogramme du début (à gauche) à la fin (à droite). Cela représente le déroulement chronologique des opérations.

- Alignement vertical : Les événements alignés verticalement se produisent simultanément. Si deux signaux changent exactement à la même ligne verticale, ils sont concurrents.

- Durée : La longueur horizontale d’un état de signal indique combien de temps il reste dans cet état. Une impulsion large signifie une durée plus longue.

- Dépendances : Recherchez les relations de cause à effet. Le changement d’un signal déclenche souvent un autre. Le diagramme montre le délai entre ces déclenchements.

Systèmes synchrones vs. asynchrones 🔄

Les chronogrammes diffèrent considérablement selon que le système est synchrone ou asynchrone. Comprendre cette distinction est essentiel pour une analyse précise.

Systèmes synchrones ⏰

Ces systèmes reposent sur un signal d’horloge global. Tous les changements d’état se produisent aux fronts spécifiques de l’horloge (montant ou descendant). Le diagramme affichera un motif régulier d’horloge. Les données ne sont échantillonnées que lorsque l’horloge le permet. Cela rend le timing prévisible, mais introduit des contraintes telles que les temps de préparation (setup) et de maintien (hold).

Systèmes asynchrones 🕰️

Ces systèmes ne reposent pas sur une horloge globale. Les changements d’état se produisent lorsque les signaux d’entrée changent. Les chronogrammes ici ont un aspect moins régulier. Ils mettent l’accent sur les protocoles d’échange de signaux. Un signal doit passer à haut, puis l’autre, puis revenir à bas. Cela exige une analyse soigneuse des délais pour éviter les conditions de course.

Paramètres critiques dans l’analyse du timing ⚙️

Au-delà du simple tracé de lignes, les ingénieurs analysent des paramètres spécifiques pour garantir la fiabilité. Ces paramètres définissent la fenêtre dans laquelle un système fonctionne correctement.

- Retard de propagation : Le temps nécessaire à un signal pour voyager depuis l’entrée jusqu’à la sortie à travers un composant. Ce délai s’accumule à travers les portes logiques.

- Temps de préparation (setup) : Le temps minimal avant un front d’horloge pendant lequel les données doivent être stables. Si les données changent trop tard, le bascule ne peut pas les capturer correctement.

- Temps de maintien (hold) : Le temps minimal après un front d’horloge pendant lequel les données doivent rester stables. Si les données changent trop tôt, la valeur actuelle est perdue.

- Désynchronisation d’horloge (clock skew) : La différence de temps d’arrivée du signal d’horloge entre différents composants. Un déséquilibre élevé peut entraîner des violations de temps de préparation ou de maintien.

- Métastabilité : Un état où la sortie d’une bascule n’est ni haute ni basse. Cela se produit lorsque les temps de préparation ou de maintien sont violés. Les chronogrammes aident à visualiser le risque de métastabilité.

Application en matériel et logiciel 🔌

Les chronogrammes ne sont pas limités au matériel. Ils sont également largement utilisés dans l’architecture logicielle et la conception de protocoles.

Conception matérielle

En matériel, ces diagrammes valident les protocoles de bus. Par exemple, vérifier que le bus d’adresse est stable avant que l’impulsion de lecture ne s’active. Ils garantissent que les temps d’accès à la mémoire correspondent à la vitesse de l’horloge du processeur. Ils sont également utilisés pour analyser les pics de consommation d’énergie lors des transitions de signal.

Logiciel et protocoles

Dans le logiciel, les diagrammes de timing représentent les appels d’API ou les échanges de messages. Ils montrent la séquence des requêtes et des réponses entre les services. Cela aide à identifier les problèmes de latence dans les systèmes distribués. Ils clarifient l’ordre des opérations dans les environnements multithreadés.

Péchés courants et erreurs 🛑

La création ou la lecture des diagrammes de timing peut entraîner des erreurs si elle n’est pas faite avec soin. Être conscient des erreurs courantes aide à améliorer la précision.

- Ignorer les signaux actifs bas : De nombreux signaux utilisent la logique active-bas (inversée). Une ligne passant à bas peut signifier que le signal est actif. Vérifiez toujours la légende ou l’étiquette.

- Supposer des transitions instantanées : Les signaux réels ont des temps de montée et de descente. Les diagrammes idéaux montrent des lignes verticales, mais les signaux physiques ont une pente. Cette pente affecte l’intégrité du signal.

- Passer à côté des parasites : Les courtes impulsions qui ne respectent pas les largeurs minimales peuvent provoquer des déclenchements erronés. On les appelle souvent des parasites.

- Mal interpréter l’état haute impédance : Les états d’impédance élevée signifient qu’un signal est déconnecté. Dans les diagrammes, cela apparaît comme une ligne pointillée ou un symbole spécifique. Ignorer cela peut entraîner des erreurs de contention de bus.

- Alignement incorrect des horloges : Supposer que toutes les horloges sont alignées en phase alors qu’elles ne le sont pas. Le décalage peut entraîner un échantillonnage incorrect des données.

Comparaison des types de diagrammes 📊

Différents contextes exigent des méthodes de visualisation différentes. Bien que les diagrammes de timing soient puissants, ce ne sont pas les seuls outils disponibles.

| Type de diagramme | Objectif principal | Meilleure utilisation |

|---|---|---|

| Diagramme de timing | Temps et états du signal | Vérification des relations entre horloge et données |

| Diagramme d’état | États du système | Définition du flux logique et des conditions |

| Diagramme de séquence | Ordre des messages | Interactions logicielles et appels d’API |

| Schéma de circuit | Connexions physiques | Câblage et disposition des composants |

| Visualiseur de forme d’onde | Signaux en temps réel | Débogage du comportement réel du matériel |

Meilleures pratiques pour la documentation 📝

Pour rendre les diagrammes de temporisation utiles pour les équipes et une référence future, suivez ces meilleures pratiques. Une documentation claire réduit l’ambiguïté et accélère le débogage.

- Tout étiqueter : Chaque ligne de signal doit avoir un nom clair. Évitez les étiquettes génériques comme Sig1.

- Inclure les unités : Précisez les unités de temps sur l’axe. S’agit-il de millisecondes ou de cycles d’horloge ?

- Marquer les points critiques : Mettez en évidence explicitement les fenêtres de setup et de hold. Utilisez le hachurage ou des couleurs distinctes pour marquer les fenêtres critiques de temporisation.

- Garder tout organisé : Regroupez les signaux connexes ensemble. Par exemple, tous les signaux de contrôle en haut, les signaux de données en bas.

- Documenter les hypothèses : Notez toutes les hypothèses formulées lors de la création. Par exemple, supposez un délai de propagation nul ou des conditions de charge spécifiques.

- Utiliser une notation cohérente : Utilisez des symboles standards pour les fronts montants, les fronts descendants et les états de haute impédance.

Guide étape par étape pour créer un diagramme 🛠️

Créer un diagramme de temporisation depuis zéro nécessite une approche structurée. Suivez ces étapes pour garantir une complétude.

- Identifier les signaux : Liste tous les entrées et sorties impliquées dans l’interaction.

- Déterminer la séquence : Définissez l’ordre des événements. Qu’est-ce qui déclenche le processus ?

- Définir l’échelle temporelle : Décidez de la granularité de l’axe temporel.

- Dessiner l’horloge : Si le système est synchrone, dessinez d’abord le signal d’horloge. Il sert de référence pour le reste du diagramme.

- Ajouter les données : Tracez les signaux de données par rapport aux fronts d’horloge.

- Vérifiez les contraintes :Vérifiez les temps de setup et de hold par rapport aux signaux tracés.

- Revue :Parcourez le chronogramme pour vous assurer qu’aucun vide logique n’existe.

Le rôle du timing dans le débogage 🐞

Lorsqu’un système échoue, les diagrammes de timing sont souvent la première chose que les ingénieurs scrutent. Ils aident à déterminer si le problème est logique ou temporel. Si la logique est correcte mais que le timing est décalé, le système échoue de manière intermittente. Cela est souvent plus difficile à reproduire qu’une erreur logique grave.

Les scénarios de débogage incluent :

- Corruption des données :Signaux qui changent pendant qu’ils sont lus.

- Interruptions manquées :Un signal d’interruption trop court pour être détecté.

- Conflit sur le bus :Deux dispositifs qui pilotent le bus en même temps.

- Passage entre domaines d’horloge :Signaux qui passent entre des fréquences d’horloge différentes sans synchronisation appropriée.

Comprendre la largeur des données et l’alignement 📐

Les diagrammes de timing visualisent également la largeur des données. Les bus parallèles nécessitent plusieurs lignes. Chaque ligne doit changer de manière synchronisée. Un mauvais alignement peut entraîner des erreurs de données. Le diagramme montre comment les bits sont alignés au sein d’un cycle d’horloge. Pour la communication série, le diagramme de timing montre le flux de bits. Il met en évidence la période du bit et le point d’échantillonnage.

Sujets avancés : Jitter et bruit 📉

Les signaux du monde réel ne sont pas parfaits. Le jitter est l’écart du front d’horloge par rapport à sa position idéale. Le bruit est une fluctuation aléatoire du niveau du signal. Les diagrammes de timing peuvent représenter le jitter en affichant une bande épaisse autour du front au lieu d’une ligne nette. Cela indique une incertitude. Les concepteurs doivent s’assurer que le système tolère cette incertitude. La marge entre la bande de jitter et la fenêtre de setup/hold constitue la marge de sécurité.

Intégration avec les suites de tests 🧪

Les diagrammes de timing ne servent pas uniquement à la conception. Ils sont utilisés pour générer des cas de test. Les suites de tests automatisées peuvent vérifier si le comportement réel du système correspond au diagramme. Si le timing mesuré dépasse la tolérance, le test échoue. Cela garantit que le matériel ou le logiciel respecte les spécifications tout au long de son cycle de vie.

Conclusion sur la visualisation du système 🎯

Les diagrammes de timing restent une pierre angulaire de l’ingénierie système. Ils combler le fossé entre la logique abstraite et la réalité physique. En visualisant l’écoulement du temps et des signaux, les ingénieurs peuvent prédire les défaillances avant qu’elles n’arrivent. Ils facilitent la communication entre les équipes matérielles et logicielles. Un diagramme bien dessiné transmet plus d’informations que des pages de texte. À mesure que les systèmes deviennent plus rapides et plus complexes, la nécessité d’une analyse de timing précise augmente. La maîtrise de ces diagrammes garantit des conceptions robustes et fiables.

N’oubliez pas de privilégier la clarté et l’exactitude. Évitez les hypothèses. Vérifiez chaque transition. Avec de la pratique, la lecture et la création de ces diagrammes deviennent une partie intuitive du processus de conception. Ils sont la carte qui guide le voyageur à travers le paysage de la logique numérique.