डिजिटल इलेक्ट्रॉनिक्स और कंप्यूटर इंजीनियरिंग की दुनिया में, सिग्नल एक निर्जीव रूप से नहीं मौजूद होते हैं। वे ट्रेस के माध्यम से, गेट्स के माध्यम से और प्रोसेसर में विशिष्ट समय सीमाओं के साथ यात्रा करते हैं। एक प्रणाली कैसे काम करती है, इसे समझने के लिए इंजीनियरों को इन सिग्नलों के समय के साथ बदलाव को देखना होता है। इस दृश्य को समय आरेख के माध्यम से प्राप्त किया जाता है। शुरुआत करने वाले के लिए, ये चार्ट जटिल हिरोग्लिफ्स की तरह लग सकते हैं, लेकिन वास्तव में ये डिजिटल लॉजिक के डिबगिंग और डिजाइन के लिए सबसे मूलभूत उपकरण हैं।

यह मार्गदर्शिका समय आरेखों के विस्तृत विश्लेषण के लिए है। हम सिग्नल के शरीर का अध्ययन करेंगे, विश्वसनीयता को परिभाषित करने वाले महत्वपूर्ण पैरामीटर्स का अध्ययन करेंगे, और ऐसे सामान्य त्रुटियों का अध्ययन करेंगे जो प्रणाली विफलता के कारण बनती हैं। चाहे आप परीक्षा की तैयारी कर रहे हों या अपना पहला माइक्रोकंट्रोलर सर्किट डिजाइन कर रहे हों, इन आरेखों को समझना आवश्यक है।

🧠 समय आरेख क्या है?

एक समय आरेख समय के साथ डिजिटल सिग्नलों की स्थिति का एक आलेखी प्रतिनिधित्व है। सर्किट स्कीमेटिक के विपरीत, जो दिखाता हैक्याकिससे जुड़ा हैक्याएक समय आरेख दिखाता हैजबचीजें होती हैं। यह वोल्टेज स्तरों को समय अक्ष के साथ आलेखित करता है, जिससे इंजीनियरों को घटनाओं के क्रम को देखने में मदद मिलती है।

इन आरेखों की कई कारणों से अत्यंत आवश्यकता होती है:

- डिबगिंग: वे रेस कंडीशन्स को उजागर करते हैं जहां सिग्नल गलत क्रम में पहुंचते हैं।

- सत्यापन: वे यह सत्यापित करते हैं कि एक सर्किट आवश्यक गति विशेषताओं को पूरा करता है।

- दस्तावेज़ीकरण: वे अलग-अलग चिप्स के बीच संचार के तरीके के लिए एक संदर्भ के रूप में कार्य करते हैं।

- डिजाइन: वे यह निर्धारित करने में मदद करते हैं कि एक प्रणाली कितनी अधिकतम क्लॉक आवृत्ति को समर्थन कर सकती है।

जब आप एक समय आरेख को देखते हैं, तो आप एक प्रणाली के माध्यम से गतिमान इलेक्ट्रॉनों के भौतिक व्यवहार का एक स्नैपशॉट देख रहे होते हैं। यह लेटेंसी, प्रसारण और समन्वय की वास्तविकता को पकड़ता है।

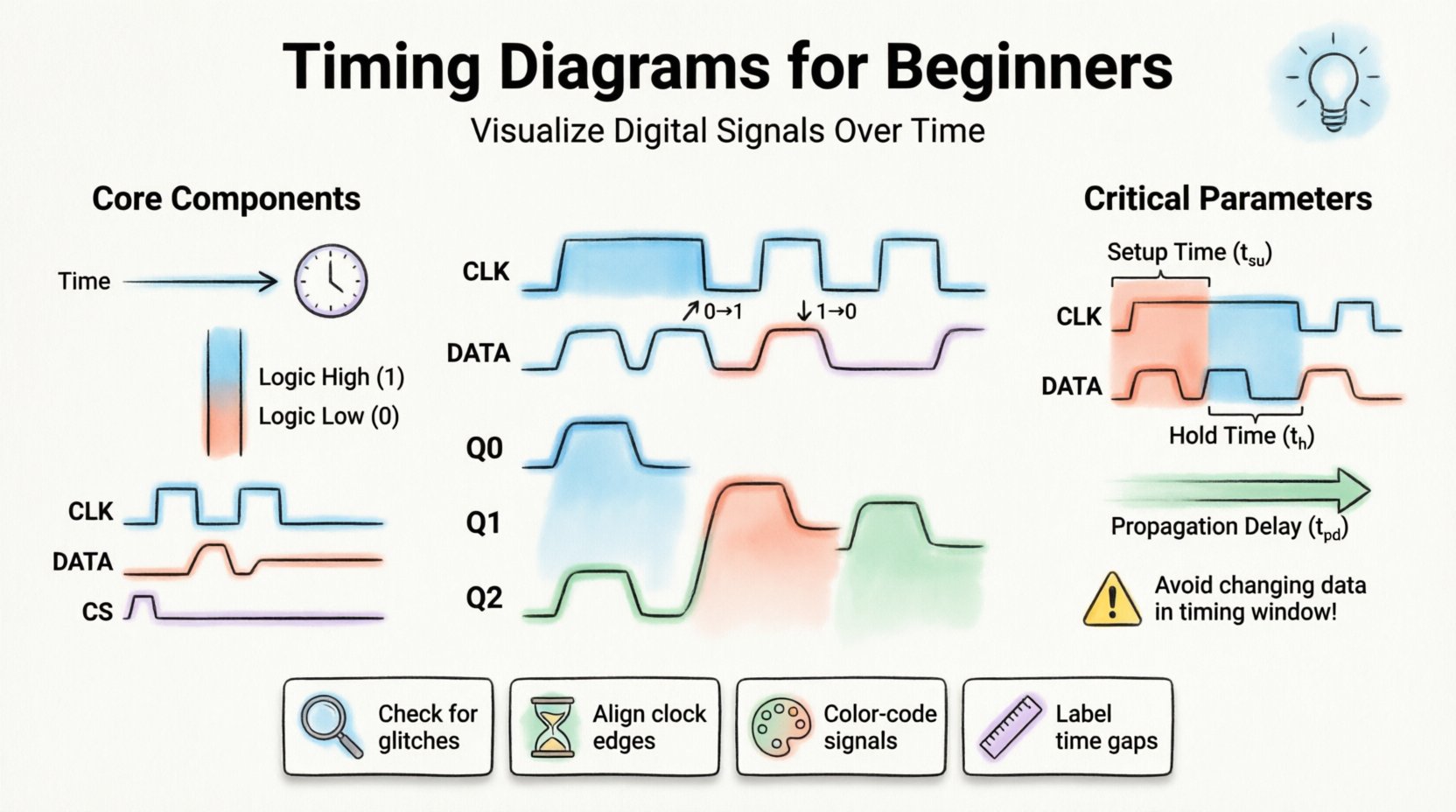

📊 समय आरेख के मुख्य घटक

जटिल तरंगरूपों के विश्लेषण से पहले, आपको निर्माण ब्लॉक्स को समझना होगा। प्रत्येक समय आरेख में कुछ मूल तत्व होते हैं।

1. समय अक्ष

क्षैतिज अक्ष समय का प्रतिनिधित्व करता है। यह बाएं से दाएं की ओर बहता है। डिजिटल डिजाइन में, इस अक्ष को अक्सर क्लॉक साइकिल में विभाजित किया जाता है, जिसे ऊर्ध्वाधर ग्रिड रेखाओं द्वारा चिह्नित किया जाता है। पैमाना उच्च गति वाले प्रोसेसर के लिए नैनोसेकंड (ns) से लेकर धीमे नियंत्रण तर्क के लिए मिलीसेकंड (ms) तक बदल सकता है।

2. वोल्टेज स्तर अक्ष

ऊर्ध्वाधर अक्ष सिग्नल की तार्किक स्थिति का प्रतिनिधित्व करता है। मानक लॉजिक परिवारों में, यह आमतौर पर द्विआधारी होता है:

- लॉजिक हाई (1):आमतौर पर VCC या 5V के रूप में दर्शाया जाता है।

- लॉजिक लो (0): अक्सर ग्राउंड या 0V के रूप में दर्शाया जाता है।

- हाई-ज़ (उच्च प्रतिरोध): एक ऐसी स्थिति जहां पिन प्रभावी रूप से अलग हो जाता है, जो बस सिस्टम में सामान्य है।

3. सिग्नल लाइनें

प्रत्येक क्षैतिज रेखा एक विशिष्ट तार या सिग्नल नाम का प्रतिनिधित्व करती है। इन रेखाओं को स्पष्ट रूप से लेबल किया गया है (उदाहरण के लिए, CLK, DATA_IN, CS), ताकि यह पहचाना जा सके कि सर्किट का कौन सा हिस्सा निगरानी में है।

🔄 सिग्नल संक्रमण पढ़ना

सिग्नल लाइन के ऊपर और नीचे जाने की गति वहां है जहां डेटा रहता है। इन गतियों की दिशा को समझना महत्वपूर्ण है।

⬆️ राइजिंग एज

एक राइजिंग एज तब होता है जब कोई सिग्नल लो से हाई में संक्रमण करता है। बाइनरी तर्क में, इसे अक्सर कई संचालनों के ट्रिगर बिंदु के रूप में देखा जाता है। इसका अर्थ 0 से 1 में परिवर्तन होता है।

⬇️ फॉलिंग एज

एक फॉलिंग एज तब होता है जब कोई सिग्नल हाई से लो में संक्रमण करता है। इसका अर्थ 1 से 0 में परिवर्तन होता है।

⚡ एज ट्रिगरिंग

बहुत से डिजिटल घटक, जैसे फ्लिप-फ्लॉप, केवल इन एजेस के प्रति प्रतिक्रिया करते हैं, स्थिर अवस्था के बजाय। एक फ्लिप-फ्लॉप केवल क्लॉक सिग्नल के राइजिंग एजपर डेटा कैप्चर कर सकता है। यदि आप एज को मिस करते हैं, तो डेटा खो जाता है।

| संक्रमण | दिशा | बाइनरी परिवर्तन | सामान्य ट्रिगर प्रकार |

|---|---|---|---|

| राइजिंग एज | लो ➔ हाई | 0 ➔ 1 | पॉजिटिव एज ट्रिगर्ड |

| फॉलिंग एज | हाई ➔ लो | 1 ➔ 0 | नेगेटिव एज ट्रिगर्ड |

| लेवल हाई | स्थिर हाई | स्थिर 1 | स्तर संवेदनशील |

| स्तर कम | स्थिर कम | स्थिर 0 | स्तर संवेदनशील |

⏳ महत्वपूर्ण समय संरचना पैरामीटर

समय आरेख केवल चित्र नहीं होते; इनमें मापदंड होते हैं। संकेत परिवर्तनों के बीच का स्थान विश्वसनीयता निर्धारित करता है। डिजिटल समय विश्लेषण में तीन विशिष्ट पैरामीटर प्रमुख हैं।

1. प्रसारण देरी (tpd)

संकेत तुरंत यात्रा नहीं करते। जब इनपुट बदलता है, तो आउटपुट में उस परिवर्तन को दर्शाने में एक सीमित समय लगता है। इसे प्रसारण देरी कहते हैं। यह सामग्री के भौतिक प्रतिरोध और धारिता के कारण होती है।

- परिभाषा: इनपुट परिवर्तन और आउटपुट परिवर्तन के बीच समय अंतर।

- प्रभाव: तर्क गेट की श्रृंखला में, देरी जमा होती है। यदि देरी बहुत अधिक है, तो संकेत अगले क्लॉक चक्र शुरू होने के बाद आ सकता है, जिससे त्रुटियाँ हो सकती हैं।

2. सेटअप समय (tsu)

सेटअप समय एक डेटा संकेत के स्थिर रहने की आवश्यकता हैपहले क्लॉक किनारे आने से पहले। यदि डेटा क्लॉक किनारे के बहुत निकट बदलता है, तो प्राप्त करने वाला सर्किट इसे सही तरीके से कैप्चर नहीं कर सकता।

- नियम: डेटा को क्लॉक ट्रिगर होने से पहले एक विशिष्ट अवधि के लिए मान्य होना चाहिए।

- दृश्य: एक आरेख पर, यह डेटा लाइन स्थिर होने और क्लॉक किनारे के बीच का अंतर है।

3. होल्ड समय (th)

होल्ड समय डेटा संकेत के स्थिर रहने की आवश्यकता हैके बाद घड़ी का किनारा आता है। यदि डेटा घड़ी के किनारे के तुरंत बाद बदल जाता है, तो सर्किट सही मान को लैच नहीं कर सकता है।

- नियम: डेटा को घड़ी के ट्रिगर के बाद एक निश्चित अवधि तक अपरिवर्तित रहना चाहिए।

- दृश्य: एक आरेख में, यह घड़ी के किनारे और अगले डेटा संक्रमण के बीच का अंतर है।

⚠️ समय खंड

सेटअप और होल्ड समय का संयोजन डेटा को कैप्चर करने के लिए एक मान्य खंड बनाता है। यदि आपका समय आरेख डेटा के इस खंड के भीतर बदलने का दर्शाता है, तो प्रणाली असफल होने के जोखिम में है।

⚡ समकालिक बनाम असमकालिक प्रणालियाँ

समय आरेख प्रणाली की संरचना के आधार पर बहुत अलग होते हैं।

समकालिक प्रणालियाँ

समकालिक डिजाइन में, सभी संचालन एक सामान्य घड़ी सिग्नल द्वारा नियंत्रित होते हैं। प्रत्येक अवस्था परिवर्तन इस घड़ी के किनारे पर होता है। इन प्रणालियों के लिए समय आरेख बहुत नियमित दिखाई देते हैं।

- विशेषताएँ: पूर्वानुमानित, डिजाइन करना आसान, घड़ी की गति द्वारा सीमित।

- आरेख का दृश्य: ऊर्ध्वाधर ग्रिड रेखाएँ सभी सिग्नल परिवर्तनों के साथ पूरी तरह से मेल खाती हैं।

असमकालिक प्रणालियाँ

असमकालिक डिजाइन में, कोई सामान्य घड़ी नहीं होती है। सिग्नल तब बदलते हैं जब भी इनपुट बदलते हैं। इससे अधिक गति की संभावना होती है, लेकिन समय विश्लेषण को बहुत कठिन बना देता है।

- विशेषताएँ: इनपुट के प्रति तेज अनुक्रिया, जटिल खतरा विश्लेषण।

- आरेख का दृश्य: सिग्नल संक्रमण अनियमित अंतरालों पर होते हैं। आपको घटनाओं के बीच के ठीक समय अंतराल को मापना होगा।

📝 समय आरेख कैसे बनाएँ

समय आरेख बनाना एक व्यवस्थित प्रक्रिया है। एक सर्किट का दस्तावेजीकरण करने या डिजाइन की पुष्टि करने के लिए इन चरणों का पालन करें।

- सिग्नल पहचानें: सभी इनपुट, आउटपुट और आंतरिक नियंत्रण लाइनों की सूची बनाएँ। उन्हें स्पष्ट रूप से लेबल करें।

- समय आधार स्थापित करें: समय पैमाने का निर्णय लें। लॉजिक सर्किट्स के लिए, घड़ी चक्कर आमतौर पर मानक इकाई होते हैं।

- घड़ी को आरेखित करें: हमेशा घड़ी सिग्नल को पहले बनाएँ। यह सभी अन्य घटनाओं के लिए संदर्भ है।

- इनपुट को मैप करें तार्किक संचालन या परीक्षण क्रम के आधार पर इनपुट तरंगरूप खींचें।

- देरी की गणना करें: शामिल गेट्स के प्रसार देरी के आधार पर आउटपुट सिग्नलों को दाईं ओर स्थानांतरित करें।

- सीमाओं की जांच करें: सुनिश्चित करें कि प्रत्येक फ्लिप-फ्लॉप के लिए सेटअप और होल्ड समय पूरे हों।

- संक्रमणों की समीक्षा करें: सुनिश्चित करें कि कोई ग्लिच न हो। एक ग्लिच एक अनचाहा, अल्पकालिक पल्स है जो तर्क को गलत तरीके से सक्रिय कर सकता है।

🔄 वास्तविक दुनिया का उदाहरण: एक सरल गणनाकर्ता

इन अवधारणाओं के एक साथ काम करने के तरीके को समझने के लिए एक सरल 3-बिट बाइनरी काउंटर को ध्यान में रखें। यह परिपथ प्रत्येक बार क्लॉक सिग्नल के पल्स के साथ अपने मान को बढ़ाता है।

तीन आउटपुट लाइनों के बारे में सोचें: Q0, Q1, और Q2। Q0 प्रत्येक क्लॉक चक्र पर टॉगल होता है। Q1 प्रत्येक बार जब Q0 एक पूर्ण चक्र पूरा करता है, तो टॉगल होता है। Q2 प्रत्येक बार जब Q1 एक पूर्ण चक्र पूरा करता है, तो टॉगल होता है।

चरण-दर-चरण विश्लेषण

- क्लॉक (CLK): 50% ड्यूटी साइकिल वाली एक वर्ग तरंग।

- Q0 (LSB): क्लॉक के प्रत्येक उत्थान किनारे पर अवस्था बदलता है। आवृत्ति क्लॉक की आधी है।

- Q1: Q0 के प्रत्येक उत्थान किनारे पर अवस्था बदलता है। आवृत्ति Q0 की आधी है।

- Q2 (MSB): Q1 के प्रत्येक उत्थान किनारे पर अवस्था बदलता है। आवृत्ति Q1 की आधी है।

इसे खींचते समय आप एक रिपल प्रभाव देखेंगे। Q0 पहले बदलता है। Q1 Q0 के स्थिर होने का इंतजार करता है फिर बदलता है। Q2 Q1 का इंतजार करता है। इस देरी के संचय के कारण ही रिपल काउंटर की विशेषता है।

| क्लॉक चक्र | Q2 | Q1 | Q0 | दशमलव मान |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ बचने के लिए सामान्य गलतियाँ

समय आरेख पढ़ते समय अनुभवी � ingineers भी गलतियाँ कर सकते हैं। इन सामान्य त्रुटियों के बारे में जागरूक रहें।

- ग्लिचेस को नजरअंदाज करना: यदि समय पैमाना बहुत बड़ा है, तो एक संक्षिप्त पल्स दिखाई नहीं दे सकता है, लेकिन यह एक लैच को ट्रिगर कर सकता है। हमेशा संकीर्ण पल्स के लिए जांच करें।

- ड्यूटी साइकिल का गलत अर्थ निकालना: एक घड़ी के 50% होने का मान लेना, जबकि वास्तव में यह विकृत है। इससे समय खंड प्रभावित होता है।

- हाई-जी अवस्थाओं को नजरअंदाज करना: बस प्रणालियों में, रेखाएँ तैरती हैं। एक समय आरेख में यह दिखाना आवश्यक है कि एक रेखा कब ड्राइव की जाती है और कब तैरती है।

- सेटअप और होल्ड में भ्रम: सेटअप किनारे से पहले होता है; होल्ड बाद में होता है। इन्हें गलत करने से गलत सर्किट डिजाइन होते हैं।

- ग्राउंड रेफरेंस की उपेक्षा: सभी वोल्टेज स्तरों को एक ही ग्राउंड के संदर्भ में मापना चाहिए। यदि ग्राउंड भिन्न हैं, तो लॉजिक स्तर अमान्य हैं।

🛠 दस्तावेज़ीकरण के लिए सर्वोत्तम प्रथाएँ

दस्तावेज़ीकरण या डीबगिंग के लिए समय आरेख बनाते समय, स्पष्टता सुनिश्चित करने के लिए इन दिशानिर्देशों का पालन करें।

- समान पैमाने का उपयोग करें: सुनिश्चित करें कि समय अक्ष रेखीय हो। यदि स्पष्ट रूप से चिह्नित नहीं है, तो एक खंड को संकुचित और दूसरे को फैलाएं।

- महत्वपूर्ण किनारों को संरेखित करें: सुनिश्चित करें कि क्लॉक किनारा डेटा सैंपलिंग बिंदु के साथ पूरी तरह से संरेखित हो।

- अंतरालों को लेबल करें: यदि कोई देरी है, तो इसे विशिष्ट समय मान के साथ लेबल करें (उदाहरण के लिए, tpd = 5ns).

- रंग कोडिंग: विभिन्न सिग्नल प्रकारों के लिए अलग-अलग रंगों का उपयोग करें (उदाहरण के लिए, क्लॉक के लिए नीला, डेटा के लिए लाल, नियंत्रण के लिए हरा)।

- सक्रिय अवस्थाओं को चिह्नित करें: स्पष्ट रूप से इंगित करें कि कोई सिग्नल सक्रिय उच्च या सक्रिय निम्न है (उदाहरण के लिए, /CS जैसे नाम के ऊपर बार का उपयोग करके)।

🧩 मेटास्टेबिलिटी और समय संबंधी खतरे

उन्नत समय आरेख अक्सर एक घटना जैसे मेटास्टेबिलिटी को उजागर करते हैं। यह तब होता है जब कोई सिग्नल फ्लिप-फ्लॉप के सेटअप/होल्ड विंडो के ठीक समय पर बदलता है। आउटपुट तुरंत 0 या 1 पर स्थिर नहीं होता; यह एक मध्यवर्ती वोल्टेज स्तर पर लटकता रहता है।

हालांकि दुर्लभ, मेटास्टेबिलिटी सिस्टम क्रैश का कारण बन सकती है। समय आरेख असिंक्रोनस इनपुट और सिंक्रोनस क्लॉक के बीच संबंध दिखाकर इसकी भविष्यवाणी में मदद करते हैं। यदि बाहरी सिग्नल क्लॉक किनारे के बहुत करीब बदलता है, तो आरेख डेटा को गलत समय पर थ्रेशोल्ड को पार करते हुए दिखाएगा।

🔍 वास्तविक डेटा का विश्लेषण

जब आप लॉजिक एनालाइज़र द्वारा उत्पन्न समय आरेख को देखते हैं, तो रेखाएँ दुर्लभ रूप से पूर्ण वर्ग होती हैं। वास्तविक दुनिया के सिग्नल में होते हैं:

- राइज़ टाइम: निम्न से उच्च तक जाने में लगने वाला समय। यह दुर्लभ रूप से तुरंत नहीं होता।

- फॉल टाइम: उच्च से निम्न तक जाने में लगने वाला समय।

- ओवरशूट/अंडरशूट: वोल्टेज शिखर जो आपूर्ति रेल्स को पार करते हैं।

- जिटर: सिग्नल किनारों के समय में भिन्नता।

इन अपूर्णताओं को समझना उच्च गति डिज़ाइन के लिए आवश्यक है। एक संपूर्ण वर्ग तरंग एक सैद्धांतिक आदर्श है; वास्तविक सिग्नल एनालॉग तरंगरूप हैं जो डिजिटल तर्क का प्रतिनिधित्व करते हैं।

📚 मुख्य बातों का सारांश

टाइमिंग आरेख डिजिटल टाइमिंग की भाषा हैं। वे संकीर्ण तर्क को भौतिक वास्तविकता में बदलते हैं। उन्हें समझने से आपको निम्न क्षमता प्राप्त होती है:

- एक प्रणाली के माध्यम से डेटा के प्रवाह को दृश्य रूप से देखने की क्षमता प्राप्त करें।

- वह स्थान पहचानें जहां सिग्नलों में संघर्ष हो सकता है।

- यह सुनिश्चित करें कि डेटा विश्वसनीय रूप से कैप्चर किया जाए।

- परिपथ की अधिकतम संचालन गति की गणना करें।

सरल लॉजिक गेट्स के साथ अभ्यास से शुरुआत करें। इनपुट बनाएं, देरी की गणना करें और आउटपुट को आरेखित करें। आगे बढ़ते हुए, जटिल बसेस और क्लॉक डोमेन्स पर जाएं। धैर्य और अभ्यास के साथ, इन आरेखों को पढ़ना आपके लिए दूसरी प्रकृति की बात हो जाएगी।

🚀 आगे बढ़ना

सिग्नल अखंडता और क्लॉक वितरण नेटवर्क के बारीकियों को जारी रखें। जैसे-जैसे प्रणालियां तेज होती हैं, टाइमिंग मार्जिन संकीर्ण होते जाते हैं। किसी भी डिजिटल हार्डवेयर के साथ काम करने वाले � ingineer के लिए टाइमिंग आरेख को सही तरीके से पढ़ने की क्षमता एक मूल क्षमता बनी रहेगी।