डिजिटल सर्किट्स के व्यवहार को समझने के लिए केवल लॉजिक गेट्स के बारे में जानने से अधिक चाहिए। यह सिग्नलों के समय के साथ बदलाव को समझने की आवश्यकता होती है। समय आरेख इस समय संबंधी विश्लेषण के लिए दृश्य भाषा प्रदान करते हैं। वे एक घड़ी या एक विशिष्ट घटना के संबंध में विभिन्न सिग्नलों की स्थिति को नक्शा बनाते हैं। कंप्यूटर विज्ञान के छात्रों के लिए इस अवधारणा को समझना विश्वसनीय प्रणालियों के डिज़ाइन के लिए आवश्यक है।

यह मार्गदर्शिका समय आरेखों में शामिल यांत्रिकी, पढ़ने की तकनीकों और महत्वपूर्ण पैरामीटर्स का अध्ययन करती है। हम बुनियादी सिग्नल संक्रमण से लेकर जटिल सेटअप और होल्ड समय उल्लंघन तक सब कुछ को कवर करेंगे। इस अवलोकन के अंत तक, आप डिजिटल अंतरक्रियाओं के विश्लेषण के लिए एक मजबूत आधार प्राप्त कर लेंगे।

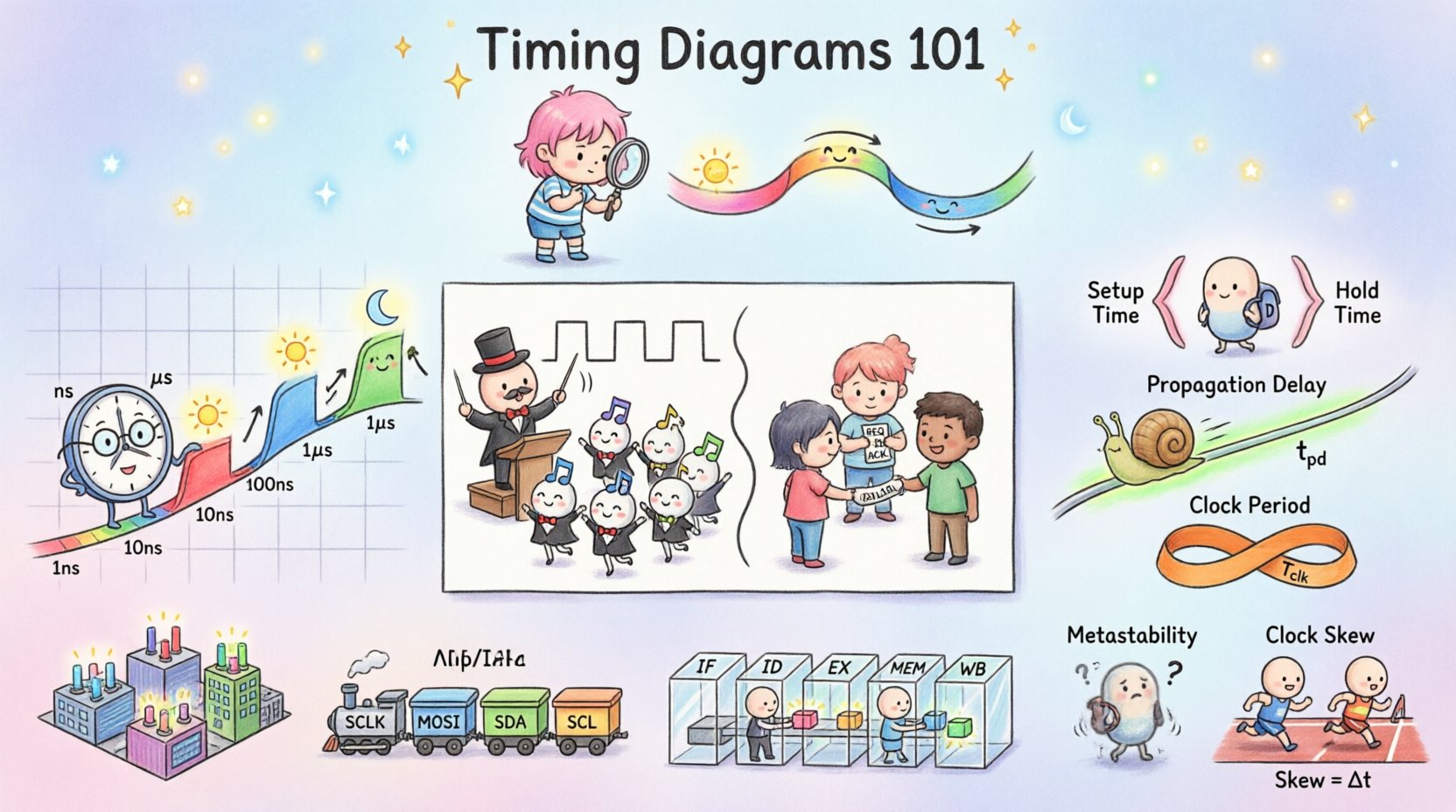

समय आरेख क्या है? ⏱️

एक समय आरेख समय के साथ दो या अधिक सिग्नलों के बीच संबंध का एक आलेखीय प्रतिनिधित्व है। यह डिजिटल घटनाओं के लिए एक समय रेखा के रूप में कार्य करता है। प्रत्येक सिग्नल को एक क्षैतिज रेखा के रूप में आलेखित किया जाता है। ऊर्ध्वाधर स्थिति लॉजिक स्तर या स्थिति को दर्शाती है। क्षैतिज अक्ष समय के प्रवाह का प्रतिनिधित्व करता है।

इन आरेखों का डिजिटल प्रणाली के सही संचालन की पुष्टि करने के लिए बहुत महत्व है। ये � ingineers को डेटा के रजिस्टर, बस और मेमोरी के माध्यम से गति के बारे में भविष्यवाणी करने में मदद करते हैं। इनके बिना, हार्डवेयर समस्याओं का निराकरण लगभग असंभव हो जाता है। ये अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं।

डिजिटल सिग्नलों के मूल घटक 📡

आरेखों में डुबकी लेने से पहले, सिग्नलों को समझना आवश्यक है। डिजिटल प्रणालियाँ बाइनरी डेटा के प्रतिनिधित्व के लिए वोल्टेज स्तरों पर निर्भर करती हैं। इन स्तरों को हमेशा स्थिर नहीं रहता है; वे अवस्थाओं के बीच संक्रमण करते हैं।

- लॉजिक हाई (1):आमतौर पर आपूर्ति रेल के पास के वोल्टेज का प्रतिनिधित्व करता है।

- लॉजिक लो (0):आमतौर पर ग्राउंड के पास के वोल्टेज का प्रतिनिधित्व करता है।

- किनारे:उच्च और निम्न के बीच संक्रमण बिंदु। राइजिंग किनारे निम्न से उच्च की ओर जाते हैं। फॉलिंग किनारे उच्च से निम्न की ओर जाते हैं।

- स्थिर अवस्था:वह अवधि जब एक सिग्नल स्थिर रहता है।

- शोर मार्जिन:वह सहिष्णुता जो एक सिग्नल को गलत व्याख्या के पहले होती है।

समय आरेख इन संक्रमणों को दृश्य रूप देते हैं। वे ठीक समय बताते हैं जब एक सिग्नल बदलता है और वह कितनी देर उस अवस्था में रहता है। यह निर्दिष्टता डेटा अखंडता सुनिश्चित करने के लिए महत्वपूर्ण है।

समय अक्ष को समझना ⏳

क्षैतिज अक्ष किसी भी समय आरेख की रीढ़ है। यह समय के प्रगति का प्रतिनिधित्व करता है। डिजिटल डिज़ाइन में, इस अक्ष को अक्सर एक घड़ी सिग्नल के साथ समकालीन किया जाता है। घड़ी प्रणाली के दिल के रूप में कार्य करती है।

समय अक्ष पर इकाइयाँ सर्किट की गति के आधार पर बदलती हैं। सामान्य इकाइयाँ इस प्रकार हैं:

- सेकंड (s):बहुत धीमी प्रणालियों के लिए उपयोग किया जाता है।

- मिलीसेकंड (ms):10^-3 सेकंड।

- माइक्रोसेकंड (µs):10^-6 सेकंड।

- नैनोसेकंड (ns):10^-9 सेकंड। आधुनिक प्रोसेसर्स के लिए मानक।

- पिकोसेकंड (पीएस): 10^-12 सेकंड। उच्च गति इंटरफेस के लिए आवश्यक।

एक आरेख को पढ़ते समय, स्केल मार्कर्स को देखें। वे प्रत्येक चक्र की अवधि को दर्शाते हैं। इससे प्रसार देरी की गणना करने और सुनिश्चित करने में मदद मिलती है कि सिग्नल आवश्यक खंड में आएं।

सिंक्रोनस बनाम एसिंक्रोनस प्रणाली 🔄

डिजिटल प्रणालियाँ आम तौर पर समय के प्रबंधन के आधार पर दो श्रेणियों में आती हैं। सही आरेख बनाने के लिए इस अंतर को समझना महत्वपूर्ण है।

1. सिंक्रोनस प्रणाली

सिंक्रोनस डिजाइन में, सभी स्थिति परिवर्तन एक सामान्य घड़ी सिग्नल के संदर्भ में होते हैं। समय आरेख में एक आवर्ती घड़ी तरंगरूप दिखाई देगा। प्रत्येक फ्लिप-फ्लॉप इस घड़ी के सक्रिय किनारे पर अपडेट होता है।

- लाभ: पूर्वानुमानित व्यवहार। जांच करना आसान।

- चुनौतियाँ: घड़ी विचलन के कारण समस्याएँ हो सकती हैं यदि सिग्नल अलग-अलग समय पर पहुँचते हैं।

- आरेख विशेषता: लंबवत रेखाएँ अक्सर घड़ी के किनारों के साथ संरेखित होती हैं ताकि कैप्चर के क्षण दिखाए जा सकें।

2. एसिंक्रोनस प्रणाली

एसिंक्रोनस डिजाइन में एक सामान्य घड़ी पर निर्भर नहीं होते। इसके बजाय, वे कार्यों को तब शुरू करने के लिए हैंडशेक प्रोटोकॉल या स्थानीय सिग्नल का उपयोग करते हैं। यहाँ समय आरेख अधिक अनियमित होते हैं।

- लाभ: कुछ मामलों में कम बिजली की खपत। तेज औसत प्रतिक्रिया समय।

- चुनौतियाँ: जांच करना कठिन। रेस की स्थिति में झुकाव।

- आरेख विशेषता: सिग्नल एक दूसरे को एक निश्चित � ritm के बिना ट्रिगर करते हैं।

महत्वपूर्ण समय संबंधी पैरामीटर 📏

विशिष्ट मापदंड एक समय आरेख की विश्वसनीयता को परिभाषित करते हैं। इन पैरामीटर्स निर्धारित करते हैं कि क्या परिपथ सभी स्थितियों में सही तरीके से काम करेगा।

| पैरामीटर | विवरण | महत्व |

|---|---|---|

| प्रसार देरी | सिग्नल के इनपुट से आउटपुट तक यात्रा करने में लगा समय। | अधिकतम संचालन आवृत्ति को सीमित करता है। |

| सेटअप समय | डेटा के स्थिर होने की आवश्यकता है कि क्लॉक एज से पहले। | यह सुनिश्चित करता है कि लैच सही मान को पकड़े। |

| होल्ड समय | डेटा के क्लॉक एज के बाद भी स्थिर रहने की आवश्यकता है। | लैच के बदलते मान को पढ़ने से रोकता है। |

| क्लॉक अवधि | क्लॉक सिग्नल के एक पूर्ण चक्र की अवधि। | प्रणाली की गति को परिभाषित करता है। |

| ड्यूटी साइकिल | अवधि का प्रतिशत जब सिग्नल उच्च होता है। | पावर उपभोग और समय सीमा पर प्रभाव डालता है। |

गहन अध्ययन: सेटअप और होल्ड समय

सेटअप और होल्ड समय अनुक्रमिक तर्क के लिए सबसे महत्वपूर्ण सीमाएं हैं। यदि उल्लंघन होता है, तो प्रणाली एक अस्थिर अवस्था में प्रवेश कर सकती है जहां आउटपुट अनिर्णयात्मक होता है।

सेटअप समय उल्लंघन: यह तब होता है जब डेटा क्लॉक एज के बहुत निकट बदलता है। सर्किट को पकड़ने के लिए पर्याप्त समय नहीं मिलता है। परिणाम अक्सर तर्क त्रुटि होती है।

होल्ड समय उल्लंघन: यह तब होता है जब डेटा क्लॉक एज के बाद बहुत जल्दी बदलता है। सर्किट अभी भी पिछले मान को पकड़ने की कोशिश कर रहा होता है। यह अक्सर ठीक करने में कठिन होता है क्योंकि यह भौतिक व्यवस्था पर निर्भर करता है।

आरेखों को पढ़ना और विश्लेषित करना 🔍

समय आरेख का विश्लेषण करने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। दृश्य डेटा को सही तरीके से समझने के लिए इन चरणों का पालन करें।

- क्लॉक की पहचान करें: आवर्ती सिग्नल को ढूंढें। यह आपका संदर्भ बिंदु है।

- सक्रिय एज को स्थापित करें: तय करें कि प्रणाली राइजिंग या फॉलिंग एज पर ट्रिगर होती है।

- सिग्नल निर्भरता का अनुसरण करें: देखें कि एक सिग्नल में परिवर्तन दूसरों को कैसे प्रभावित करता है।

- ग्लिचेस के लिए जांच करें: छोटी पल्स के लिए तलाश करें जो शोर या अनचाहे संक्रमण हो सकते हैं।

- सीमाओं की पुष्टि करें: सुनिश्चित करें कि सभी रजिस्टर के लिए सेटअप और होल्ड समय का पालन किया जाता है।

एक सरल डेटा स्थानांतरण परिदृश्य पर विचार करें। एक CPU मेमोरी को डेटा भेजता है। समय आरेख में पहले एड्रेस लाइन्स के स्थिर होने को दिखाया जाएगा, फिर डेटा लाइन्स, और अंत में लिखने वाला सिग्नल। प्रत्येक चरण को एक विशिष्ट खंड के भीतर होना चाहिए।

सामान्य उल्लंघन और उनका प्रभाव ⚠️

यहां तक कि अनुभवी � ingineers को भी समय संबंधी समस्याओं का सामना करना पड़ता है। सामान्य उल्लंघनों को समझना समस्या निवारण में मदद करता है।

1. अस्थिरता

जब कोई सिग्नल सेटअप या होल्ड समय का उल्लंघन करता है, तो फ्लिप-फ्लॉप आउटपुट स्थिर होने से पहले दोलन कर सकता है। इस स्थिति को अस्थिरता कहा जाता है। यह प्रणाली के माध्यम से फैल सकती है, जिससे अप्रत्याशित व्यवहार होता है। इस जोखिम को कम करने के लिए सिंक्रोनाइजेशन सर्किट का अक्सर उपयोग किया जाता है।

2. विचलन

क्लॉक विचलन तब होता है जब क्लॉक सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुंचता है। इससे प्रभावी समय सीमा कम हो सकती है। सकारात्मक विचलन अधिक सेटअप समय देता है लेकिन कम होल्ड समय देता है। ऋणात्मक विचलन इसके विपरीत करता है।

3. दौड़ स्थितियां

दौड़ स्थितियां तब होती हैं जब आउटपुट घटनाओं के क्रम पर निर्भर करता है। यदि दो सिग्नल एक साथ बदलते हैं, तो उनके प्रसंस्करण का क्रम अंतिम स्थिति निर्धारित करता है। समय आरेख समय के अनुक्रम को देखने में मदद करते हैं ताकि दौड़ स्थितियों से बचा जा सके।

कंप्यूटर आर्किटेक्चर में अनुप्रयोग 🖥️

समय आरेख केवल सैद्धांतिक उपकरण नहीं हैं। वे वास्तविक दुनिया की आर्किटेक्चर में व्यापक रूप से उपयोग किए जाते हैं।

मेमोरी इंटरफेस

DRAM और SRAM के सख्त समय संबंधी आवश्यकताएं होती हैं। मेमोरी कंट्रोलर को पढ़ने या लिखने से पहले विशिष्ट देरी का इंतजार करना होता है। समय आरेख कमांड बस अनुक्रम को परिभाषित करते हैं। वे यह सुनिश्चित करते हैं कि डेटा को प्राप्त करने से पहले मेमोरी बैंक तैयार हो।

बस प्रोटोकॉल

I2C, SPI और UART जैसे प्रोटोकॉल संचार के लिए समय पर निर्भर होते हैं। SPI में क्लॉक लाइन डेटा स्थानांतरण को समकालिक बनाती है। UART में समय बॉड दर पर आधारित होता है। रिसीवर को बिट अवधि के ठीक मध्य में डेटा लाइन का नमूना लेना होता है। एक समय आरेख शुरुआत बिट, डेटा बिट्स और स्टॉप बिट के संरेखण को दिखाता है।

पाइपलाइन चरण

आधुनिक CPU प्रत्येक चरण को एक क्लॉक साइकिल के भीतर पूरा करने के लिए बहुत निर्देशों को एक साथ निष्पादित करने के लिए पाइपलाइनिंग का उपयोग करते हैं। समय आरेख फेच, डिकोड, एक्जीक्यूट और राइट-बैक चरणों के माध्यम से डेटा के प्रवाह को नक्शा बनाते हैं। वे उन रुकावटों को पहचानने में मदद करते हैं जहां एक चरण दूसरे का इंतजार करता है।

दस्तावेजीकरण के लिए सर्वोत्तम व्यवहार 📝

स्पष्ट समय आरेख बनाने से यह सुनिश्चित होता है कि अन्य इंजीनियर आपके डिजाइन को समझ सकें। प्रभावी दस्तावेजीकरण के लिए इन दिशानिर्देशों का पालन करें।

- समान पैमाने का उपयोग करें: सुनिश्चित करें कि समय अक्ष दस्तावेज के पूरे भाग में समान हो।

- स्पष्ट रूप से लेबल करें: हर सिग्नल का नाम रखें। “सिग्नल 1” जैसे सामान्य लेबल से बचें।

- सीमाओं को उजागर करें: सेटअप और होल्ड विंडो को दिखाने के लिए कोष्ठक या छायांकित क्षेत्रों का उपयोग करें।

- संबंधित सिग्नलों को समूहित करें: नियंत्रण सिग्नलों को एक साथ रखें और डेटा सिग्नलों को एक साथ रखें।

- अनुमान शामिल करें: जटिल संक्रमण या विशेष व्यवहार को समझाने वाले नोट जोड़ें।

उन्नत Pertimbangan 🔬

जैसे-जैसे प्रणालियां तेज होती हैं, समय विश्लेषण अधिक जटिल हो जाता है। कई कारक कठिनाइयों के तहत जोड़ते हैं।

1. पावर सप्लाई नॉइज

वोल्टेज उतार-चढ़ाव लॉजिक गेट्स के प्रतिबंध स्तरों को बदल सकते हैं। इससे प्रसारण देरी में प्रभावी बदलाव आता है। समय आरेखों में सबसे खराब संभावित वोल्टेज परिस्थितियों को शामिल करना आवश्यक है।

2. तापमान में भिन्नता

इलेक्ट्रॉनिक घटक अलग-अलग तापमान पर अलग-अलग व्यवहार करते हैं। उच्च तापमान प्रतिरोध और देरी बढ़ाता है। कम तापमान धारिता को प्रभावित कर सकता है। डिजाइनरों को पूरी संचालन तापमान सीमा में समय की जांच करनी चाहिए।

3. सिग्नल अखंडता

सर्किट बोर्ड पर लंबे ट्रेस ट्रांसमिशन लाइन के रूप में काम करते हैं। प्रतिबिंब और क्रॉसटॉक निश्चित रूप से सिग्नल को विकृत कर सकते हैं। उच्च गति वाले लिंक के लिए समय आरेखों में आई डायग्राम या सिग्नल गुणवत्ता मापदंड शामिल करने चाहिए।

समय विश्लेषण पर निष्कर्ष 🎯

समय आरेख डिजिटल लॉजिक के नेविगेशन के लिए नक्शा हैं। वे संकेत बाइनरी अवस्थाओं को भौतिक समय घटनाओं में बदलते हैं। कंप्यूटर विज्ञान के छात्र के लिए इन आरेखों को पढ़ने और बनाने में निपुणता एक मूल क्षमता है।

क्लॉक साइकिल, प्रसारण देरी और सेटअप सीमाओं को समझकर आप दृढ़ और कुशल प्रणालियों का डिजाइन कर सकते हैं। सिग्नल प्रवाह को दृश्य रूप से देखने की क्षमता हार्डवेयर डिजाइन में महंगी त्रुटियों को रोकती है। तकनीक विकसित होती रहे, सिद्धांत वही रहते हैं। समय स्थिर चर है।

मूल सिद्धांतों पर ध्यान केंद्रित करें। मौजूदा आरेखों को पढ़ने का अभ्यास करें। हर नए सर्किट के लिए अपना आरेख बनाएं। यह अनुशासन आपके तकनीकी करियर में बहुत मदद करेगा।