डिजिटल प्रणालियाँ सही कार्य करने के लिए सटीक समन्वय पर निर्भर करती हैं। जब सिग्नल गलत समय पर आते हैं, तो तर्क विफलताएँ होती हैं, जिसके परिणामस्वरूप अप्रत्याशित व्यवहार होता है। डिजिटल तर्क, कंप्यूटर इंजीनियरिंग या इलेक्ट्रॉनिक्स के अध्ययन करने वाले किसी भी व्यक्ति के लिए इन समस्याओं के विश्लेषण और निवारण को समझना आवश्यक है। यह मार्गदर्शिका अनुक्रमिक परिपथों और डेटा संचरण में सामना की जाने वाली समय समस्याओं की पहचान और निवारण के लिए मूल अवधारणाओं और व्यावहारिक चरणों को कवर करती है।

घड़ी सिग्नलों और किनारों को समझना ⏱️

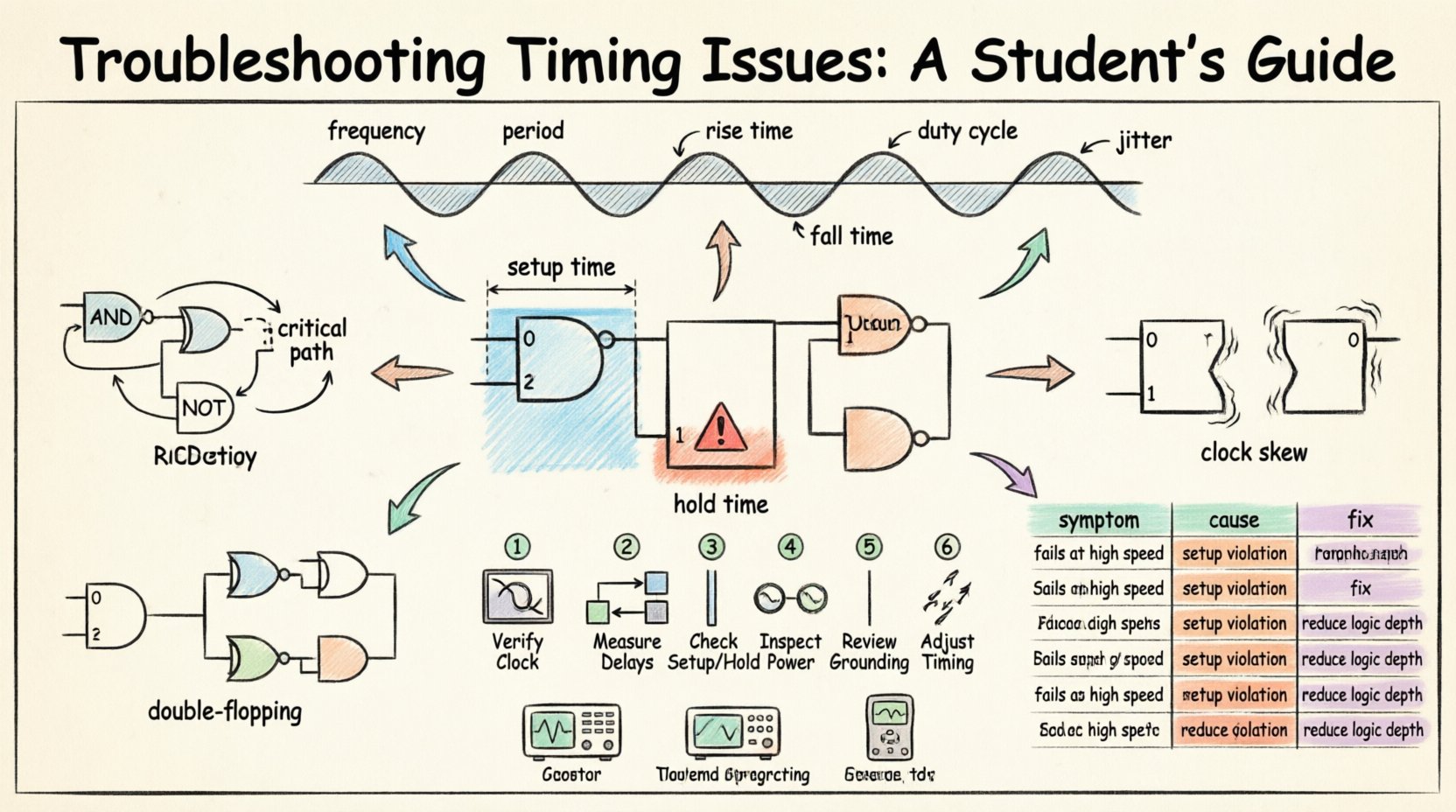

अधिकांश डिजिटल डिजाइनों के केंद्र में घड़ी सिग्नल होता है। यह आवर्ती तरंगरूप निर्धारित करता है कि डेटा कब नमूना लिया जाता है और अवस्था परिवर्तन कब होता है। निराकरण की प्रक्रिया अक्सर इस मूलभूत सिग्नल की अखंडता की जांच करके शुरू होती है।

- आवृत्ति और आवर्तकाल: घड़ी आवृत्ति संचालन की गति निर्धारित करती है। आवर्तकाल एक पूर्ण चक्र के समय के अंतराल को दर्शाता है। यदि परिपथ को 100 मेगाहर्ट्ज की घड़ी की आवश्यकता है, तो आवर्तकाल 10 नैनोसेकंड है। यहाँ कोई भी विचलन सभी निर्गम तर्क पर प्रभाव डालता है।

- उठाव और गिरावट के समय: एक संपूर्ण वर्ग तरंग सिद्धांतात्मक है। वास्तविक सिग्नलों में सीमित उठाव और गिरावट के समय होते हैं। यदि संक्रमण बहुत धीमा है, तो सिग्नल अपरिभाषित वोल्टेज क्षेत्र में बहुत समय बिता सकता है, जिससे बार-बार टॉगल होना या तर्क त्रुटियाँ हो सकती हैं।

- ड्यूटी साइकिल: यह सिग्नल के उच्च रहने के समय का कुल आवर्तकाल से अनुपात है। 50% ड्यूटी साइकिल मानक है, लेकिन कुछ डिजाइनों को असममित चक्रों की आवश्यकता होती है। विचलन सेटअप या होल्ड आवश्यकताओं के लिए समय सीमा को विकृत कर सकते हैं।

जब किसी परिपथ की जांच कर रहे हों, तो घड़ी तरंगरूप को देखने के लिए ऑसीलोस्कोप या लॉजिक एनालाइजर का उपयोग करें। शोर के चोटे, रिंगिंग या अत्यधिक जिटर के लिए देखें। जिटर का अर्थ है घड़ी के किनारे का समय में आदर्श स्थिति से विचलन। उच्च जिटर डेटा के स्थिर होने के लिए उपलब्ध प्रभावी समय सीमा को कम कर देता है।

सेटअप और होल्ड समय उल्लंघन ⚠️

ये अनुक्रमिक तर्क डिजाइन में सामना की जाने वाली सबसे आम समय उल्लंघन हैं। फ्लिप-फ्लॉप और लैच में डेटा के घड़ी के किनारे के संबंध में स्थिर रहने के लिए विशिष्ट आवश्यकताएँ होती हैं।

सेटअप समय

सेटअप समय घड़ी के किनारे से पहले डेटा के स्थिर रहने के लिए न्यूनतम समय की मात्रा है। यदि डेटा घड़ी के किनारे के बहुत निकट बदलता है, तो फ्लिप-फ्लॉप सही मान को पकड़ नहीं पाएगा।

- प्रतिबंध: फ्लिप-फ्लॉप को भोजन देने वाले संयोजी तर्क के प्रसारण देरी को घड़ी के आवर्तकाल माइनस सेटअप समय से कम होना चाहिए।

- लक्षण: प्रणाली कम आवृत्ति पर काम कर सकती है, लेकिन गति बढ़ने पर विफल हो सकती है। आउटपुट में यादृच्छिक बिट त्रुटियाँ अक्सर होती हैं।

- समाधान: रजिस्टरों के बीच तर्क की गहराई को कम करें, घड़ी के आवर्तकाल को बढ़ाएं, या तेज घटकों का उपयोग करें।

होल्ड समय

होल्ड समय घड़ी के किनारे के बाद डेटा के स्थिर रहने के लिए न्यूनतम समय की मात्रा है। यदि डेटा घड़ी के किनारे के बाद बहुत जल्दी बदलता है, तो फ्लिप-फ्लॉप पकड़े गए मान को खो सकता है।

- प्रतिबंध: संयोजी तर्क के प्रसारण देरी को गंतव्य फ्लिप-फ्लॉप के होल्ड समय से अधिक होना चाहिए।

- लक्षण: होल्ड उल्लंघन आवृत्ति के बावजूद अक्सर होते हैं। इसका कारण यह है कि देरी निरपेक्ष होती है, आवर्तकाल के सापेक्ष नहीं।

- समाधान: डेटा पथ में देरी बफर जोड़कर सिग्नल को धीमा करें, या तर्क को पुनर्डिजाइन करके देरी को कम करें।

इन दोनों में अंतर करना बहुत महत्वपूर्ण है। सेटअप उल्लंघन आवृत्ति-निर्भर होते हैं, जबकि होल्ड उल्लंघन पथ-निर्भर होते हैं। एक सामान्य गलती होल्ड उल्लंघन को घड़ी को धीमा करके ठीक करने की कोशिश करना है; यह काम नहीं करेगा और इसे और बदतर बना सकता है।

प्रसारण देरी और पथ विश्लेषण 📉

सिग्नल तुरंत यात्रा नहीं करते हैं। प्रत्येक तार, गेट और घटक एक देरी उत्पन्न करता है। डेटा समय पर पहुंचता है या नहीं, इसकी गारंटी देने के लिए इन देरियों का विश्लेषण क्रांतिक है।

- संयोजी तर्क देरी: यह एक सिग्नल के AND, OR और NOT जैसे गेट्स से गुजरने में लगने वाला समय है। लंबी गेट श्रृंखलाएं महत्वपूर्ण लेटेंसी उत्पन्न करती हैं।

- इंटरकनेक्ट देरी: एक भौतिक बोर्ड पर, तारों में धारिता और प्रतिरोध होता है। लंबे ट्रेस अधिक देरी उत्पन्न करते हैं। इसे अक्सर RC नेटवर्क के रूप में मॉडल किया जाता है।

- पिन-टू-पिन देरी: घटक में क्लॉक इनपुट से डेटा आउटपुट तक का समय। इसे आमतौर पर डेटाशीट में निर्दिष्ट किया जाता है।

जब समस्या का निराकरण कर रहे हों, तो क्रांतिक पथ का नक्शा बनाएं। यह दो क्रमागत तत्वों के बीच सबसे लंबी देरी वाला पथ है। यदि क्रांतिक पथ क्लॉक अवधि से अधिक हो जाता है, तो डिज़ाइन विफल हो जाएगा। इसे खोजने के लिए, सभी संभावित पथों के देरी के योग की गणना करें और अधिकतम को पहचानें।

क्लॉक स्क्यू और जिटर 📶

यहां तक कि यदि क्लॉक स्रोत पूर्ण है, तो सिग्नल अलग-अलग घटकों पर अलग-अलग समय पर पहुंच सकता है। इस घटना को स्क्यू के रूप में जाना जाता है।

- क्लॉक स्क्यू: यह तब होता है जब क्लॉक सिग्नल अलग-अलग फ्लिप-फ्लॉप्स तक पहुंचने के लिए अलग-अलग दूरी तय करता है। सकारात्मक स्क्यू कैप्चर क्लॉक को देरी देता है, जिससे सेटअप समय ढीला होता है लेकिन होल्ड समय संकुचित होता है। ऋणात्मक स्क्यू सेटअप समय को संकुचित करता है लेकिन होल्ड समय को ढीला करता है।

- क्लॉक जिटर: क्लॉक एज के समय में अल्पकालिक भिन्नताएं। जिटर डेटा सेटअप के लिए उपलब्ध समय बजट को कम करता है।

- ड्रिफ्ट: तापमान या पावर सप्लाई में उतार-चढ़ाव के कारण समय के साथ क्लॉक आवृत्ति में धीमी बदलाव।

जटिल डिज़ाइनों में स्क्यू को आमतौर पर क्लॉक ट्री सिंथेसिस द्वारा प्रबंधित किया जाता है। छात्र परियोजनाओं में, इसे आमतौर पर क्लॉक ट्रेस को समान रूप से रूट करके और छोटा रखकर न्यूनतम किया जाता है। यदि स्क्यू के संदेह हैं, तो सर्किट के बहुत सारे बिंदुओं पर एक साथ क्लॉक को मापें।

मेटास्टेबिलिटी और असमानक इनपुट्स 🌀

जब डेटा क्लॉक एज के साथ ही बदलता है, तो फ्लिप-फ्लॉप एक मेटास्टेबिल स्थिति में प्रवेश करता है। यह तुरंत 0 या 1 पर स्थिर नहीं होता है, बल्कि एक मध्यवर्ती वोल्टेज स्तर पर लटकता रहता है।

- खतरा: मेटास्टेबिलिटी प्रणाली में फैल सकती है, जिससे ऐसी तर्क त्रुटियां होती हैं जिन्हें दोहराना मुश्किल होता है।

- असमानक सिग्नल: बाहरी स्विच या संचार पोर्ट से आने वाले इनपुट आमतौर पर आंतरिक क्लॉक के साथ समान नहीं होते हैं। इन्हें सिंक्रोनाइज़ किया जाना चाहिए।

- डबल फ्लॉपिंग: मेटास्टेबिलिटी को दूर करने की एक सामान्य तकनीक दो फ्लिप-फ्लॉप्स को श्रृंखला में प्रवाहित करना है। पहला मेटास्टेबिल स्थिति को कैप्चर करता है, और दूसरा अगले चक्र के दौरान इसे हल करता है।

हमेशा असमानक इनपुट्स को संभावित मेटास्टेबिलिटी स्रोत के रूप में मानें। उन्हें सख्त समय सीमा वाले तर्क से सीधे जोड़ें नहीं। अलग-अलग क्लॉक डोमेनों के बीच सुरक्षित डेटा स्थानांतरण सुनिश्चित करने के लिए सिंक्रोनाइज़र सर्किट का उपयोग करें।

एक स्टेप-बाय-स्टेप त्रुटि निवारण कार्य प्रवाह 🛠️

जब समय संबंधी समस्या उत्पन्न होती है, तो कारण को अलग करने के लिए एक संरचित दृष्टिकोण अपनाएं। यादृच्छिक बदलाव परिणाम देने की संभावना कम है।

- क्लॉक की पुष्टि करें: आवृत्ति, ड्यूटी साइकिल और आयाम की जांच करें। सुनिश्चित करें कि सिग्नल स्थिर और साफ है।

- देरी का मापन करें: इनपुट और आउटपुट तरंगरूपों को कैप्चर करने के लिए लॉजिक एनालाइजर का उपयोग करें। मार्ग की वास्तविक प्रसारण देरी का मापन करें।

- सेटअप और होल्ड की जांच करें: मापी गई देरियों के आधार पर यह गणना करें कि क्या मार्ग सेटअप और होल्ड सीमाओं को पूरा करता है।

- पावर की जांच करें: वोल्टेज ड्रॉप गेट्स को धीमा कर सकते हैं। सुनिश्चित करें कि पावर सप्लाई स्थिर है और पर्याप्त धारा प्रदान करती है।

- ग्राउंडिंग की समीक्षा करें: खराब ग्राउंडिंग समय संबंधी त्रुटियों की नकल करने वाली शोर उत्पन्न कर सकती है। ग्राउंड लूप और साझा रिटर्न पथ की जांच करें।

- समय संचालन को समायोजित करें: यदि डिज़ाइन लचीला है, तो क्लॉक आवृत्ति को समायोजित करें या मार्ग को संतुलित करने के लिए बफर जोड़ें।

इस प्रक्रिया के दौरान दस्तावेज़ीकरण महत्वपूर्ण है। तरंगरूपों और मापदंडों को रिकॉर्ड करें। इस डेटा की सहायता से अपेक्षित व्यवहार की तुलना वास्तविक प्रदर्शन से की जा सकती है।

सामान्य त्रुटियों की संदर्भ सारणी 📊

विशिष्ट लक्षणों के निदान के लिए इस सारणी का त्वरित संदर्भ के रूप में उपयोग करें।

| अवलोकित लक्षण | संभावित कारण | सिफारिश की गई कार्रवाई |

|---|---|---|

| सिस्टम उच्च गति पर विफल हो जाता है | सेटअप समय उल्लंघन | लॉजिक गहराई को कम करें या क्लॉक अवधि बढ़ाएं |

| सिस्टम निम्न गति पर विफल हो जाता है | होल्ड समय उल्लंघन | डेटा मार्ग में देरी बफर जोड़ें |

| यादृच्छिक बिट फ्लिप | सिग्नल शोर या जिटर | शील्डिंग और पावर सप्लाई स्थिरता की जांच करें |

| आउटपुट लटकता है या रीसेट होता है | मेटास्टेबिलिटी | सिंक्रोनाइज़र श्रृंखला कार्यान्वित करें |

| असंगत व्यवहार | घड़ी विचलन | घड़ी के ट्रेस की लंबाई को संतुलित करें |

| कोई आउटपुट ही नहीं | घड़ी सक्षम नहीं है | घड़ी वितरण और सक्षम संकेतों की पुष्टि करें |

उपकरण और उपकरण 📏

जबकि सिमुलेशन उपकरण उपयोगी हैं, भौतिक पुष्टि के लिए अक्सर विशिष्ट हार्डवेयर की आवश्यकता होती है। इन उपकरणों का सही तरीके से उपयोग करने की समझ त्रुटि निवारण कौशल सेट का हिस्सा है।

- ऑसीलोस्कोप:वोल्टेज स्तर और सिग्नल आकृति देखने के लिए आवश्यक। सर्किट को लोड न करने के लिए उच्च प्रतिरोध वाले प्रोब का उपयोग करें।

- लॉजिक एनालाइजर: डिजिटल सिग्नल के लिए बेहतर। यह समय के साथ लॉजिक स्थिति (0 या 1) को कैप्चर करता है। यह विशिष्ट पैटर्न पर ट्रिगर कर सकता है ताकि त्रुटियों को अलग किया जा सके।

- आवृत्ति गिनती: यदि स्कोप उपलब्ध नहीं है, तो घड़ी स्रोत की ठीक आवृत्ति की पुष्टि करने के लिए उपयोग किया जाता है।

सुनिश्चित करें कि प्रोब सही तरीके से कैंपेंसेट हैं। अकैंपेंसेट प्रोब सिग्नल आकृति को विकृत कर सकता है, जिससे राइज समय और देरी के बारे में गलत निष्कर्ष निकल सकते हैं।

सिग्नल अखंडता के लिए अंतिम विचार 🔒

टाइमिंग समस्याएं अक्सर व्यापक सिग्नल अखंडता समस्याओं के लक्षण होती हैं। जैसे-जैसे सर्किट तेज होते हैं, बोर्ड के भौतिक गुणों का महत्व बढ़ता है।

- क्रॉसटॉक:पड़ोसी तारों पर सिग्नल एक-दूसरे के साथ बाधा डाल सकते हैं। उच्च गति वाली लाइनों को संवेदनशील लाइनों से अलग रखें।

- प्रतिरोध संतुलन: यदि ट्रेस प्रतिरोध ड्राइवर या रिसीवर के साथ मेल नहीं खाता है, तो प्रतिबिंब उत्पन्न होते हैं। इन प्रतिबिंबों को समय विलंब की तरह दिखाई दे सकता है।

- तापीय प्रभाव: जैसे-जैसे घटक गर्म होते हैं, उनके विद्युतीय गुण बदल जाते हैं। इससे प्रसारण देरी में परिवर्तन हो सकता है और लोड के तहत समय संबंधी विफलता हो सकती है।

समय के लिए डिजाइन करने के लिए एक समग्र दृष्टिकोण की आवश्यकता होती है। यह केवल लॉजिक गेट्स के बारे में नहीं है; यह सिग्नल के यात्रा करने वाले भौतिक माध्यम के बारे में है। इन सिद्धांतों का पालन करके, छात्र विभिन्न परिस्थितियों में विश्वसनीय रूप से काम करने वाले टिकाऊ प्रणालियां बना सकते हैं।

वास्तविक हार्डवेयर के साथ नियमित अभ्यास इन अवधारणाओं को आंतरिक करने में मदद करता है। सिद्धांत ढांचा प्रदान करता है, लेकिन हाथों-हाथ डिबगिंग कठिन समय समस्याओं को कुशलतापूर्वक हल करने के लिए आवश्यक तर्क को बनाता है।