डिजिटल प्रणालियाँ सही कार्य करने के लिए सटीक समन्वय पर निर्भर करती हैं। सटीक समय के बिना, डेटा क्षति, सिस्टम क्रैश और सुरक्षा विफलताएँ अनिवार्य हो जाती हैं। एक समय आरेख संकेतों के समय के साथ परिवर्तन का दृश्य प्रतिनिधित्व प्रदान करता है, जो घड़ी चक्रों, डेटा वैधता और नियंत्रण संकेतों के बीच संबंधों को स्पष्ट रूप से दिखाता है। यह मार्गदर्शिका विभिन्न क्षेत्रों में समय आरेखों की महत्वपूर्ण भूमिका का अध्ययन करती है, आम चुनौतियों के लिए व्यावहारिक उदाहरणों और तकनीकी समाधानों का वर्णन करती है।

🔍 मूल सिद्धांतों को समझना

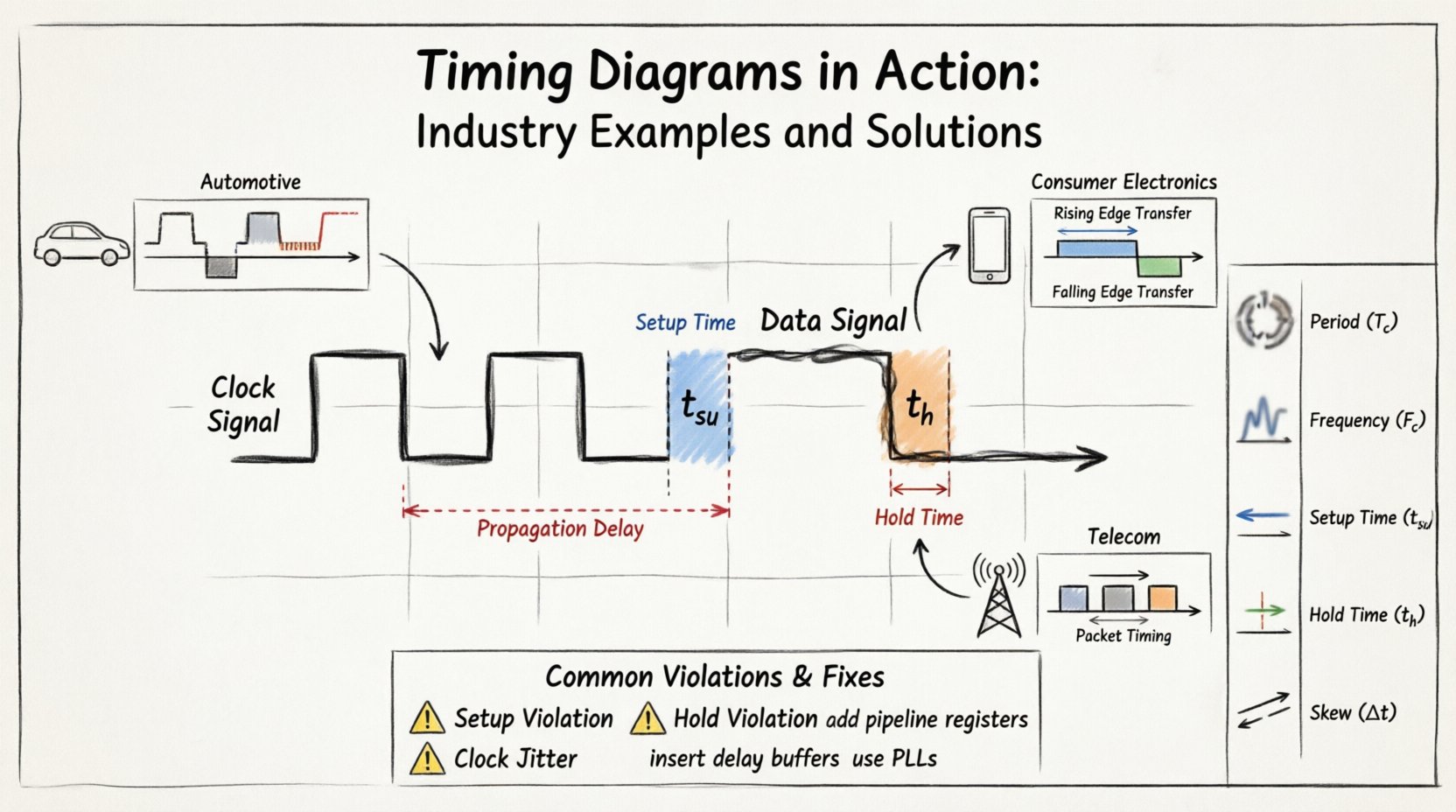

विशिष्ट अनुप्रयोगों में डुबकी लगाने से पहले, समय आरेख के मूल घटकों को समझना आवश्यक है। इन आरेखों में संकेतों के एक संदर्भ घड़ी के संबंध में व्यवहार का नक्शा बनाया जाता है। ये केवल चित्र नहीं हैं; ये गणितीय सीमाएँ हैं जो हार्डवेयर के व्यवहार को निर्धारित करती हैं।

- संकेत किनारे: निम्न से उच्च (राइजिंग एज) या उच्च से निम्न (फॉलिंग एज) के संक्रमण अनुक्रमिक तर्क में अवस्था परिवर्तन को प्रेरित करता है।

- घड़ी अवधि: एक ही ध्रुवता वाले दो क्रमागत किनारों के बीच की अवधि तर्क के स्थिर होने के लिए उपलब्ध समय को परिभाषित करती है।

- प्रसारण देरी: तर्क गेटों के माध्यम से एक संकेत के इनपुट पिन से आउटपुट पिन तक यात्रा करने में लगने वाला समय।

- सेटअप और होल्ड समय: महत्वपूर्ण सीमाएँ जो सुनिश्चित करती हैं कि घड़ी के किनारे से पहले और बाद में डेटा स्थिर रहे।

जब इन पैरामीटर्स का उल्लंघन किया जाता है, तो सर्किट मेटास्टेबल अवस्था में प्रवेश कर सकता है, जिससे अप्रत्याशित व्यवहार होता है। � ingineers समय आरेखों का उपयोग यह सत्यापित करने के लिए करते हैं कि डिज़ाइन के भौतिक कार्यान्वयन इन तार्किक आवश्यकताओं का पालन करता है।

🚗 ऑटोमोटिव इलेक्ट्रॉनिक्स: सुरक्षा-महत्वपूर्ण समय

ऑटोमोटिव उद्योग उच्चतम स्तर की विश्वसनीयता की मांग करता है। वाहनों में CAN (कंट्रोलर एरिया नेटवर्क), LIN (लोकल इंटरकनेक्ट नेटवर्क) और फ्लेक्सरे जैसे बसों के माध्यम से संचार करने वाले दर्जनों इलेक्ट्रॉनिक कंट्रोल यूनिट्स (ECUs) होते हैं। यहाँ समय विश्लेषण केवल गति के बारे में नहीं है; यह निर्णायकता और सुरक्षा के बारे में है।

1. CAN बस अर्बिट्रेशन

CAN बस एक ही तार पर कई नोड्स के बीच संचार की अनुमति देती है। CAN अर्बिट्रेशन के लिए समय आरेख बताता है कि बस प्रतिस्पर्धा के दौरान प्राथमिकता कैसे निर्धारित की जाती है।

- प्रमुख बनाम प्रतिस्पर्धी: तर्क स्तरों को वोल्टेज अवस्थाओं द्वारा दर्शाया जाता है। एक प्रमुख बिट (0) एक प्रतिस्पर्धी बिट (1) को ओवरराइड करता है।

- समन्वय: नोड्स समन्वय खंडों के उपयोग से फ्रेम बिट की शुरुआत के साथ समन्वय करते हैं।

- नमूना बिंदु: शोर को बचने के लिए डेटा बिट समय के एक विशिष्ट प्रतिशत पर नमूना लिया जाता है।

यदि नमूना बिंदु किनारे के बहुत करीब है, तो शोर के कारण बिट त्रुटियाँ हो सकती हैं। यदि यह बहुत देर हो जाता है, तो डेटा स्थिर नहीं हो सकता है। समय आरेख इंजीनियरों को नमूना बिंदु को सही तरीके से सेट करने में मदद करते हैं, जो आमतौर पर बिट समय के लगभग 80% पर होता है।

2. सेंसर फ्यूजन में ADC नमूनाकरण

आधुनिक वाहन वातावरण की अनुभूति बनाने के लिए कई सेंसर (रडार, लिडार, कैमरे) का उपयोग करते हैं। एनालॉग-टू-डिजिटल कन्वर्टर्स (ADCs) को एलियसिंग से बचने के लिए संकेतों को सटीक अंतरालों पर नमूना लेना चाहिए।

- घड़ी जिटर: घड़ी के किनारे के समय में भिन्नता डिजिटाइज्ड संकेत में शोर प्रवेश करती है।

- लेटेंसी: सेंसर इनपुट से प्रोसेस्ड डेटा आउटपुट तक का समय वास्तविक समय नियंत्रण के लिए न्यूनतम करना चाहिए।

- इंटरलीविंग:बहुत सारे ADCs अक्सर समानांतर में काम करते हैं। समय आरेख यह सुनिश्चित करते हैं कि उनके चरण समायोजित हों ताकि डेटा में अंतराल न बनें।

📱 उपभोक्ता इलेक्ट्रॉनिक्स: उच्च गति इंटरफेस

उपभोक्ता उपकरण प्रदर्शन और शक्ति दक्षता को प्राथमिकता देते हैं। DDR मेमोरी और डिस्प्ले लिंक जैसे इंटरफेस को उच्च बैंडविड्थ प्राप्त करने के लिए तनावपूर्ण समय खंडों की आवश्यकता होती है बिना शक्ति खपत बढ़ाए।

1. DDR मेमोरी इंटरफेस

डबल डेटा रेट (DDR) मेमोरी क्लॉक के उठाव और गिरावट दोनों किनारों पर डेटा स्थानांतरित करती है। इससे प्रभावी डेटा दर दोगुनी हो जाती है लेकिन डेटा स्थिरता के लिए समय खंड आधा हो जाता है।

| पैरामीटर | परिभाषा | उल्लंघन का प्रभाव |

|---|---|---|

| सेटअप समय | क्लॉक किनारे से पहले डेटा को स्थिर रहना चाहिए | डेटा स्थानांतरण छूटना, सिस्टम लटकना |

| होल्ड समय | क्लॉक किनारे के बाद डेटा को स्थिर रहना चाहिए | क्षतिग्रस्त डेटा, बिट उलटना |

| क्लॉक स्क्यू | विभिन्न चिप्स तक क्लॉक के आगमन समय में अंतर | समय सीमा कम होना, अस्थिरता |

| ड्यूटी साइकिल | उच्च समय का कुल अवधि से अनुपात | असंतुलित प्रदर्शन, बढ़ी हुई जिटर |

DDR4 और DDR5 में, कमांड और एड्रेस बस को अक्सर डेटा बस की तुलना में कम आवृत्ति पर चलाया जाता है। समय आरेखों में डेटा के साथ आने वाले स्रोत-सिंक्रोनस स्ट्रोब सिग्नल (DQS) को ध्यान में रखना आवश्यक है ताकि मान्य खंडों को दर्शाया जा सके।

2. डिस्प्ले इंटरफेस (MIPI DSI)

मोबाइल उपकरण प्रोसेसर को स्क्रीन से जोड़ने के लिए MIPI डिस्प्ले सीरियल इंटरफेस (DSI) का उपयोग करते हैं। इस इंटरफेस में उच्च गति वाले डिफरेंशियल लेन उपयोग किए जाते हैं।

- LP कमांड मोड:कमांड भेजने के लिए कम शक्ति मोड, जागरूकता अनुक्रम के लिए सख्त समय नियमों पर निर्भर।

- HS डेटा मोड:उच्च गति स्थानांतरण जहां क्लॉक पुनर्प्राप्ति डेटा प्रवाह पर की जाती है।

- टर्नाराउंड समय: एक ही लेन पर ट्रांसमिट से रिसीव मोड में स्विच करने के लिए आवश्यक समय।

इन समय आरेखों में असंगति के कारण स्क्रीन के दोष, झिलमिलाहट या वीडियो आउटपुट का पूर्ण नुकसान होता है।

📡 दूरसंचार: लैटेंसी और बैंडविड्थ

दूरसंचार में, समय लैटेंसी के समान होता है। 5जी और उच्च आवृत्ति वाले व्यापार जैसी सेवाओं के लिए पैकेट डिलीवरी समय और वितरित नेटवर्कों में समन्वय निर्णायक है।

1. PCIe संकेतन

पेरिफेरल कंपोनेंट इंटरकनेक एक्सप्रेस (PCIe) मानक उच्च गति वाले घटकों को जोड़ने के लिए व्यापक रूप से उपयोग किया जाता है। इसमें एम्बेडेड क्लॉक या सोर्स-सिंक्रोनस क्लॉक वाले सीरियल लेन में उपयोग किया जाता है।

- समायोजन: सिग्नल अखंडता दूरी के साथ घटती है। समय आरेख दिखाते हैं कि समायोजन फिल्टर क्षति की भरपाई कैसे करते हैं।

- लिंक प्रशिक्षण: लिंक गति और लेन चौड़ाई स्थापित करने के लिए समयबद्ध अवस्थाओं का क्रम।

- फ्लो नियंत्रण: क्रेडिट-आधारित फ्लो नियंत्रण के लिए समय खंड बफर ओवरफ्लो को रोकते हैं।

2. ईथरनेट PHYs

मानक ईथरनेट एक साझा क्लॉक या क्लॉक रिकवरी पर निर्भर है। गीगाबिट ईथरनेट और उससे आगे 8b/10b कोडिंग का उपयोग करता है ताकि क्लॉक रिकवरी के लिए पर्याप्त संक्रमण सुनिश्चित किए जा सकें।

- आइडल अवधि: परिभाषित समय खंड जहां कोई डेटा नहीं भेजा जाता है ताकि समन्वय बनाए रखा जा सके।

- फ्रेम शुरुआत विभाजक: एक विशिष्ट बिट पैटर्न जो पैकेट की शुरुआत को चिह्नित करता है, जिसके लिए सटीक डिटेक्शन समय की आवश्यकता होती है।

- पैकेट के बीच का अंतराल: हार्डवेयर को रीसेट करने के लिए पैकेटों के बीच अनिवार्य देरी।

⚠️ सामान्य समय उल्लंघन और समाधान

सावधानीपूर्वक डिजाइन करने के बावजूद, समय उल्लंघन होते हैं। मूल कारण की पहचान करने के लिए समय आरेख का विश्लेषण करना आवश्यक है ताकि पता लगाया जा सके कि सिग्नल अपेक्षाओं से कहाँ विचलित हो रहे हैं।

1. सेटअप समय उल्लंघन

तब होता है जब डेटा क्लॉक किनारे द्वारा कैप्चर किए जाने से बहुत देर से आता है।

- कारण: अत्यधिक लॉजिक गहराई, लंबे तार देरी, या क्लॉक स्क्यू।

- समाधान:

- लंबे मार्गों को तोड़ने के लिए पाइपलाइन रजिस्टर डालें।

- गेट काउंट को कम करने के लिए लॉजिक सिंथेसिस को अनुकूलित करें।

- अधिक समय प्रदान करने के लिए क्लॉक आवृत्ति को समायोजित करें।

2. होल्ड समय उल्लंघन

जब डेटा क्लॉक एज के बाद बहुत तेजी से बदलता है, तो यह घटित होता है, जिससे कैप्चर किए गए मान को ओवरराइट कर दिया जाता है।

- कारण:छोटे पथ देरी, क्लॉक स्क्यू जहां कैप्चर क्लॉक बहुत देर से आता है।

- समाधान:

- डेटा पथ में देरी बफर डालें।

- पथों को संतुलित करने के लिए रीटाइमिंग तकनीकों का उपयोग करें।

- यह सुनिश्चित करें कि क्लॉक वितरण नेटवर्क में न्यूनतम स्क्यू हो।

3. क्लॉक स्क्यू और जिटर

स्क्यू विभिन्न रजिस्टरों पर क्लॉक सिग्नल के आगमन समय के बीच का अंतर है। जिटर क्लॉक एज के छोटे समय अंतर का विचलन है।

- प्रभाव:डेटा के लिए उपलब्ध प्रभावी समय सीमा को कम करता है।

- समाधान:

- कम जिटर वाले क्लॉक जनरेटर का उपयोग करें।

- समान लंबाई वाले ट्रेस के साथ संतुलित क्लॉक ट्री डिज़ाइन करें।

- क्लॉक सिग्नल को साफ करने के लिए फेज-लॉक्ड लूप (PLLs) कार्यान्वित करें।

✅ कार्यान्वयन के लिए सर्वोत्तम व्यवहार

टिकाऊ समय सीमा प्राप्त करने के लिए डिज़ाइन जीवनचक्र के दौरान एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। दस्तावेज़ीकरण और सत्यापन सर्किट के समान महत्वपूर्ण हैं।

1. समय सीमा को जल्दी निर्धारित करें

कार्यान्वयन चरण तक इंतजार न करें और समय सीमा के आवश्यकताओं को निर्धारित करें। डिज़ाइन विवरण में क्लॉक आवृत्तियों, इनपुट देरी और आउटपुट देरी को दस्तावेज़ीकृत करें। इससे सुनिश्चित होता है कि सभी हितधारक प्रणाली की सीमाओं को समझते हैं।

2. स्थिर समय विश्लेषण का उपयोग करें

स्थिर समय विश्लेषण (STA) उपकरण प्रत्येक इनपुट संयोजन के सिमुलेशन किए बिना सबसे खराब स्थिति वाले देरी पथ की गणना करते हैं। यह विधि कुशल है और सभी संभावित स्थितियों को कवर करती है, जिससे कोई समय सीमा उल्लंघन नहीं छूटता।

3. सिमुलेशन के साथ प्रमाणीकरण करें

जबकि STA शक्तिशाली है, डायनामिक सिमुलेशन विशिष्ट स्थितियों में सिग्नल व्यवहार का दृश्य प्रदान करता है। समानांतर तर्क या जटिल राज्य मशीनों वाले महत्वपूर्ण पथों को सत्यापित करने के लिए सिमुलेशन का उपयोग करें।

4. भौतिक डिज़ाइन के मामले

चिप या बोर्ड की भौतिक व्यवस्था सीधे समय सीमा को प्रभावित करती है।

- तार की लंबाई:लंबे तार अधिक धारिता और प्रतिरोध जोड़ते हैं, जिससे देरी बढ़ती है।

- क्रॉसटॉक:पड़ोसी सिग्नल शोर में योगदान कर सकते हैं, जिससे गलत संक्रमण होते हैं।

- पावर सप्लाई शोर: वोल्टेज ड्रॉप गेट स्विचिंग गति को धीमा कर सकते हैं।

🛠️ वास्तविक दुनिया के परिदृश्यों का निराकरण

जब कोई प्रणाली समय सीमा को पूरा नहीं करती है, तो एक संरचित डीबगिंग प्रक्रिया की आवश्यकता होती है। निम्नलिखित चरण समय समस्याओं के समाधान के लिए एक तार्किक दृष्टिकोण को चिह्नित करते हैं।

- चरण 1: पथ की पहचान करें।विफलता के कारण विशिष्ट रजिस्टर-टू-रजिस्टर पथ को ढूंढें। सबसे नकारात्मक स्लैक के लिए समय रिपोर्ट देखें।

- चरण 2: तरंगरूपों का विश्लेषण करें। वास्तविक सिग्नल संक्रमण की जांच करने के लिए समय आरेख दर्शक का उपयोग करें। उन्हें अपेक्षित मानों के विपरीत तुलना करें।

- चरण 3: क्लॉक की जांच करें। क्लॉक सिग्नल की गुणवत्ता की पुष्टि करें। जिटर, ड्यूटी साइकिल विकृति या ग्लिच के लिए देखें।

- चरण 4: प्रतिबंधों की समीक्षा करें। सुनिश्चित करें कि डिज़ाइन फ़ाइल में प्रतिबंध हार्डवेयर की भौतिक वास्तविकता के अनुरूप हैं।

- चरण 5: पुनरावृत्ति करें। लॉजिक या लेआउट में बदलाव करें, फिर समय विश्लेषण को दोहराएं।

📊 समय संकेतकों का सारांश

त्वरित संदर्भ के लिए, उद्योगों में उपयोग किए जाने वाले मुख्य समय संकेतकों का सारांश यहां दिया गया है।

| पैरामीटर | प्रतीक | सामान्य इकाई | विवरण |

|---|---|---|---|

| अवधि | टीसी | नैनोसेकंड | क्रमागत क्लॉक एज के बीच का समय |

| आवृत्ति | एफसी | हर्ट्ज | अवधि का व्युत्क्रम |

| सेटअप समय | tsu | निम | घड़ी के किनारे से पहले डेटा स्थिरता की आवश्यकता होती है |

| होल्ड समय | th | निम | घड़ी के किनारे के बाद डेटा स्थिरता की आवश्यकता होती है |

| प्रसारण देरी | tपीडी | निम | सिग्नल के लॉजिक से गुजरने में लगने वाला समय |

| विचलन | Δt | पीएस | घड़ी के आगमन समय का अंतर |

🔄 असमान डिजाइनों का प्रबंधन

सभी प्रणालियाँ एकल घड़ी पर नहीं चलती हैं। असमान डिजाइन में डेटा अलग-अलग घड़ी क्षेत्रों के बीच पार करता है। इससे अस्थिरता का जोखिम उत्पन्न होता है, जहाँ एक फ्लिप-फ्लॉप अपरिभाषित अवस्था में प्रवेश कर जाता है।

- समकालीन श्रृंखला: सिग्नल के उपयोग से पहले स्थिर होने की अनुमति देने के लिए बहु-चरण समकालीन उपकरण (आमतौर पर दो फ्लिप-फ्लॉप) का उपयोग करें।

- हैंडशेक प्रोटोकॉल: सुनिश्चित करने के लिए अनुरोध-पुष्टि तंत्र कार्यान्वित करें कि डेटा भेजे जाने से पहले प्राप्तकर्ता तैयार हो।

- FIFO बफर: उत्पादक और उपभोक्ता की गति को अलग करने के लिए पहले आए, पहले जाए वाली मेमोरी संरचना का उपयोग करें।

असमान डिजाइन के लिए समय आरेख दो स्वतंत्र घड़ियों के बीच संबंध को दर्शाते हैं। मुख्य बात यह सुनिश्चित करना है कि डेटा पथ को प्राप्त करने वाली घड़ी द्वारा इसे नमूना लेने से पहले स्थिर होने के लिए पर्याप्त समय मिले।

🌟 अंतिम विचार

समय आरेख डिजिटल प्रणाली के सत्यापन की रीढ़ हैं। वे अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं। सेटअप समय, होल्ड समय, घड़ी विचलन और जिटर के बारे में समझकर � ingineers ऐसी प्रणालियाँ डिज़ाइन कर सकते हैं जो दृढ़, कुशल और विश्वसनीय हों।

कार सुरक्षा प्रणालियों, उपभोक्ता उपकरणों या दूरसंचार बुनियादी ढांचे में, सिद्धांत एक जैसे रहते हैं। समय में निपुणता प्रदर्शन में निपुणता की ओर जाती है। निरंतर निगरानी और उत्तम व्यवहारों का पालन सुनिश्चित करता है कि डिजाइन अपने जीवनचक्र के दौरान कार्यात्मक रहें। तकनीक विकसित होने और गति बढ़ने के साथ, विस्तृत समय विश्लेषण का महत्व केवल बढ़ेगा।

डिज़ाइन गुणवत्ता में सुधार करने के लिए तैयार टीमों के लिए, सटीक समय आरेखों और सत्यापन प्रवाह में समय निवेश करना आवश्यक है। यह जोखिम को कम करता है, डिबगिंग लागत को कम करता है, और यह सुनिश्चित करता है कि अंतिम उत्पाद अपनी विशिष्टताओं को पूरा करता है। सही उपकरणों और विधियों के साथ, समय संबंधी चुनौतियाँ अवरोधों के बजाय प्रबंधनीय सीमाओं में बदल जाती हैं।