एम्बेडेड इंजीनियरिंग की जटिल दुनिया में, समय सब कुछ है। एक माइक्रोकंट्रोलर सिमुलेशन में पूरी तरह से काम कर सकता है, लेकिन कुछ नैनोसेकंड के देरी के कारण हार्डवेयर पर भयंकर तरीके से विफल हो सकता है। यहीं पर समय आरेख एक अनिवार्य उपकरण बन जाता है। ये दृश्य प्रतिनिधित्व समय के साथ सिग्नल के व्यवहार को दर्शाते हैं, जो डिजिटल सिस्टम के भीतर घटकों के बीच बातचीत का स्पष्ट तस्वीर प्रदान करते हैं। चाहे आप कम्युनिकेशन विफलता का निराकरण कर रहे हों या एक नए पेरिफेरल इंटरफेस को डिज़ाइन कर रहे हों, समय आरेख पढ़ने और बनाने की समझ मूलभूत है।

यह मार्गदर्शिका सिग्नल समय के मूल तत्वों से लेकर जटिल प्रोटोकॉल इंटरैक्शन तक के आवश्यक यांत्रिकी को कवर करती है। हम तरंगरूपों के अर्थ निकालने, मापन डेटा से सटीक आरेख बनाने और ऐसी सामान्य गलतियों की पहचान करने का अध्ययन करेंगे जो सिस्टम अस्थिरता के कारण बनती हैं। इन दृश्य उपकरणों को स्वामित्व में लाने से आपको सिस्टम के व्यवहार का अनुमान लगाने और डिज़ाइन की पुष्टि करने की क्षमता मिलती है, जब तक वे कभी बेंच से बाहर नहीं निकलते।

🔍 सिग्नल समय के मूल सिद्धांतों को समझना

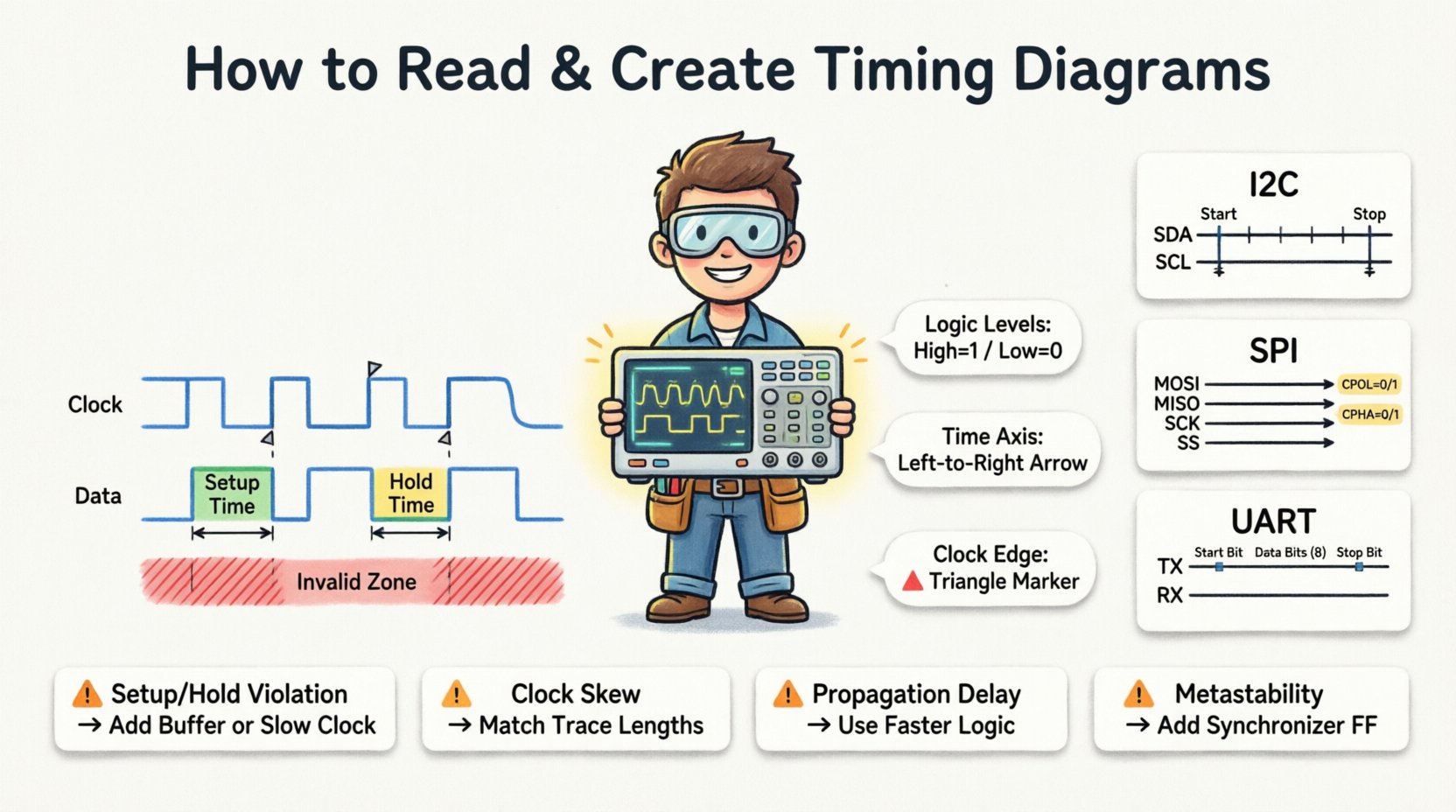

एक समय आरेख सिर्फ एक ड्राइंग नहीं है; यह समय अक्ष के संबंध में तार्किक अवस्थाओं का गणितीय प्रतिनिधित्व है। एम्बेडेड सिस्टम में, हम मुख्य रूप से डिजिटल लॉजिक स्तरों के साथ काम करते हैं, जो द्विआधारी होते हैं: हाई (1) और लो (0)। हालांकि, इन स्तरों के बीच संक्रमण ही जटिलता का केंद्र है।

- लॉजिक स्तर:अधिकांश एम्बेडेड सिस्टम विशिष्ट वोल्टेज सीमाओं पर काम करते हैं। उदाहरण के लिए, 3.3V सिस्टम हाई को 2.0V से ऊपर के किसी भी मान के रूप में परिभाषित करता है और लो को 0.8V से नीचे के किसी भी मान के रूप में परिभाषित करता है।

- समय अक्ष:समय बाएं से दाएं की ओर बहता है। क्षैतिज दूरी विशिष्ट अवस्थाओं की अवधि या घटनाओं के बीच देरी का प्रतिनिधित्व करती है।

- सिग्नल ट्रेस: प्रत्येक क्षैतिज रेखा एक विशिष्ट तार या नेट का प्रतिनिधित्व करती है। क्षैतिज रूप से बैठी बहुत सी रेखाएं सिग्नल संबंधों की तुलना करने की अनुमति देती हैं।

एक सिस्टम के विश्लेषण करते समय, आप कारणता की तलाश कर रहे होते हैं। क्या क्लॉक सिग्नल डेटा बदलाव को ट्रिगर करता है? क्या एनेबल सिग्नल को डेटा वैध होने से पहले सक्रिय होना चाहिए? समय आरेख इन प्रश्नों के दृश्य रूप से उत्तर देते हैं।

🛠️ समय आरेख के मुख्य घटक

एक आरेख को सही तरीके से समझने के लिए, आपको सिग्नल व्यवहार को दर्शाने के लिए उपयोग किए जाने वाले मानक तत्वों को पहचानना होगा। इन घटकों द्वारा हार्डवेयर के लिए नियमों को परिभाषित किया जाता है।

| घटक | विवरण | दृश्य संकेतक |

|---|---|---|

| सिग्नल नाम | विशिष्ट तार या नेट की पहचान करता है | बाएं ओर टेक्स्ट लेबल |

| लॉजिक स्तर | हाई (1) या लो (0) अवस्था | ऊपर या नीचे समतल क्षैतिज रेखा |

| संक्रमण किनारा | हाई से लो या इसके विपरीत परिवर्तन | स्तरों को जोड़ने वाली ऊर्ध्वाधर रेखा |

| क्लॉक किनारा | सिंक्रोनस लॉजिक के लिए ट्रिगर बिंदु | डैश्ड रेखा या त्रिभुज संकेतक |

| अमान्य क्षेत्र | वह क्षेत्र जहां डेटा को पढ़ा नहीं जा सकता है | छायांकित या छेद वाला क्षेत्र |

इन घटकों को समझने से आप जटिल बातचीत को विघटित करने में सक्षम होते हैं। उदाहरण के लिए, छायांकित क्षेत्र अक्सर एक सेटअप या होल्ड समय की आवश्यकता को इंगित करता है, जहां प्राप्त करने वाले उपकरण को डेटा को विश्वसनीय रूप से कैप्चर करने में असमर्थता होती है।

👁️ समय आरेख को चरण दर चरण पढ़ने का तरीका

समय आरेख को पढ़ने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। आप मूल रूप से एक दृश्य पैटर्न को घटनाओं के क्रम में बदल रहे हैं। सटीकता सुनिश्चित करने के लिए इस प्रक्रिया का पालन करें।

1. क्लॉक स्रोत की पहचान करें

अधिकांश एम्बेडेड प्रणालियां सिंक्रोनस होती हैं, जिसका अर्थ है कि क्लॉक सिग्नल संचालन की गति को निर्धारित करता है। क्लॉक ट्रेस को ढूंढें। यह आमतौर पर एक नियमित, आवर्ती वर्ग तरंग प्रदर्शित करता है।

- आवृत्ति की जांच करें। क्या यह 1 मेगाहर्ट्ज़ है या 100 मेगाहर्ट्ज़? इससे पूरी प्रणाली की गति निर्धारित होती है।

- किनारे के प्रकार की पहचान करें। क्या उपकरण राइजिंग एज (लो से हाई) या फॉलिंग एज (हाई से लो) पर ट्रिगर होता है?

2. डेटा वैधता विंडो को मैप करें

डेटा केवल क्लॉक के संबंध में विशिष्ट विंडो में ही वैध होता है। क्लॉक एज और डेटा लाइन के बीच संबंध को देखें।

- सेटअप समय: डेटा को एक निश्चित अवधि तक स्थिर रहना चाहिए पहले क्लॉक एज के बाद।

- होल्ड समय: डेटा को एक निश्चित अवधि तक स्थिर रहना चाहिए बाद में क्लॉक एज के बाद।

यदि डेटा इन विंडो में बदलता है, तो समय संबंधी उल्लंघन होता है, जिसके परिणामस्वरूप अस्थायी स्थिति या गलत डेटा कैप्चर हो सकता है।

3. नियंत्रण सिग्नलों का विश्लेषण करें

नियंत्रण सिग्नल जैसे चिप सेलेक्ट (CS), एनेबल (EN) या रीसेट (RST) निर्धारित करते हैं कि संचार कब हो सकता है।

- क्या चिप सेलेक्ट एक्टिव लो है या एक्टिव हाई?

- क्या एनेबल सिग्नल को क्लॉक के टॉगल होने से पहले असर्ट करने की आवश्यकता है?

- क्या कोई असिंक्रोनस घटनाएं हैं जो क्लॉक तर्क को ओवरराइड करती हैं?

4. हैंडशेकिंग तंत्र की पुष्टि करें

बहुत से प्रोटोकॉल फ्लो कंट्रोल को प्रबंधित करने के लिए हैंडशेकिंग का उपयोग करते हैं। एक्नॉलेज या रेडी सिग्नल को देखें।

- क्या भेजने वाला अगले बाइट को भेजने से पहले किसी सिग्नल का इंतजार करता है?

- क्या आरेख में टाइमआउट की स्थिति का प्रतिनिधित्व किया गया है?

📐 सटीक समय आरेख बनाने का तरीका

समय आरेख बनाना उसे पढ़ने के बराबर महत्वपूर्ण है। यह हार्डवेयर इंजीनियरों के लिए एक विनिर्देश के रूप में काम करता है और सॉफ्टवेयर विकासकर्ताओं के लिए एक सत्यापन मार्गदर्शिका है। आप इन्हें आवश्यकताओं, मापन उपकरणों या सिमुलेशन डेटा से उत्पन्न कर सकते हैं।

चरण 1: प्रोटोकॉल आवश्यकताओं को परिभाषित करें

चित्र बनाने से पहले विनिर्देशों को एकत्र करें। आमतौर पर ये उस घटक के डेटाशीट से आते हैं जिसके साथ आप इंटरफेस कर रहे हैं।

- न्यूनतम और अधिकतम क्लॉक आवृत्तियाँ निकालें।

- लॉजिक हाई और लो के लिए वोल्टेज स्तरों को नोट करें।

- सेटअप और होल्ड समय की सीमाओं को रिकॉर्ड करें।

चरण 2: सिग्नल डेटा को कैप्चर करें

वास्तविक दुनिया के व्यवहार को कैप्चर करने के लिए हार्डवेयर उपकरणों का उपयोग करें। इससे यह सुनिश्चित होता है कि आपका आरेख तैरते सिद्धांतों के बजाय वास्तविकता का प्रतिनिधित्व करे।

- ऑसीलोस्कोप्स:एनालॉग सिग्नल अखंडता और वोल्टेज स्तरों के लिए सर्वोत्तम।

- लॉजिक एनालाइजर्स:डिजिटल स्थिति संक्रमण और बहु-चैनल समय के लिए सर्वोत्तम।

- सिमुलेशन मॉडल्स: हार्डवेयर उपलब्ध होने से पहले लॉजिक के सत्यापन के लिए अच्छा।

चरण 3: तरंगरूपों को आरेखित करें

सिग्नलों को क्रमानुसार बनाएं। सुनिश्चित करें कि सभी चैनलों में समय पैमाना समान हो।

- लॉजिक स्तरों के लिए सीधी रेखाओं का उपयोग करें।

- उठाने और गिराने के समय को दर्शाने के लिए संक्रमण के लिए तिरछी रेखाओं का उपयोग करें।

- महत्वपूर्ण बिंदुओं जैसे क्लॉक किनारे और डेटा परिवर्तन को लेबल करें।

चरण 4: महत्वपूर्ण सीमाओं को टिप्पणी करें

टिप्पणियाँ ऐसी संदर्भ प्रदान करती हैं जो चित्रों के अकेले नहीं बता सकते।

- सेटअप और होल्ड समय के खंडों को स्पष्ट रूप से चिह्नित करें।

- विशिष्ट प्रोटोकॉल स्थितियों के अवधि (उदाहरण के लिए, स्टार्ट बिट, स्टॉप बिट) को इंगित करें।

- सिग्नल पथ में किसी भी ज्ञात लेटेंसी या देरी को उजागर करें।

🌐 सामान्य एम्बेडेड प्रोटोकॉल में समय आरेख

अलग-अलग संचार प्रोटोकॉल में अलग-अलग समय विशेषताएँ होती हैं। इन बातों को समझना एकीकरण के लिए आवश्यक है।

1. इंटर-इंटीग्रेटेड सर्किट (I2C)

I2C एक दो-तार सिंक्रोनस सीरियल बस है। इसमें SDA (डेटा) और SCL (क्लॉक) का उपयोग किया जाता है।

- शुरुआत की स्थिति: SCL उच्च होने के दौरान SDA उच्च से निम्न में संक्रमण करता है।

- स्टॉप शर्त: SCL उच्च होने के दौरान SDA कम से उच्च में संक्रमित होता है।

- डेटा स्थानांतरण: जब SCL उच्च होता है तो डेटा मान्य होता है; जब SCL कम होता है तो परिवर्तन होते हैं।

- एके/नैक: प्राप्तकर्ता नौवें क्लॉक पल्स के दौरान SDA को कम करके प्राप्ति की पुष्टि करता है।

2. सीरियल पेरिफेरल इंटरफेस (SPI)

SPI एक चार तार वाला सिंक्रोनस बस है जो I2C की तुलना में अधिक गति प्रदान करता है।

- रेखाएँ: MOSI (मास्टर आउट), MISO (मास्टर इन), SCK (क्लॉक), SS (स्लेव चयन)।

- CPOL: क्लॉक पोलैरिटी आराम की स्थिति (उच्च या कम) निर्धारित करती है।

- CPHA: क्लॉक चरण निर्धारित करता है कि डेटा कब नमूना लिया जाता है (पहले या दूसरे किनारे)।

- चिप चयन: क्लॉक के टॉगल होने से पहले आवश्यक है (सक्रिय)।

3. यूनिवर्सल एसिंक्रोनस रिसीवर-ट्रांसमीटर (UART)

UART एसिंक्रोनस है, जिसका अर्थ है कि कोई साझा क्लॉक सिग्नल नहीं है। समय का निर्धारण बॉड दर पर निर्भर करता है।

- स्टार्ट बिट: फ्रेम के आरंभ को संकेत देने के लिए लाइन को कम करता है।

- डेटा बिट्स: सामान्यतः 8 बिट्स के साथ एलएसबी पहले प्रसारित किया जाता है।

- स्टॉप बिट: फ्रेम के अंत को संकेत देने के लिए लाइन को उच्च करता है।

- पैरिटी: त्रुटि जांच के लिए वैकल्पिक बिट।

| विशेषता | I2C | SPI | UART |

|---|---|---|---|

| घड़ी | समकालिक (साझा) | समकालिक (साझा) | असमकालिक (कोई घड़ी नहीं) |

| तार | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| पता निर्धारण | हाँ (बाइट पता) | नहीं (तार आधारित) | नहीं |

| अधिकतम गति | ~400 किलोहर्ट्ज़ | ~50 मेगाहर्ट्ज़ | ~3 मेगाबिट प्रति सेकंड |

⚠️ सामान्य समय संबंधी उल्लंघन और डिबगिंग

सावधानी से डिज़ाइन करने पर भी समय संबंधी उल्लंघन हो सकते हैं। ये अक्सर ऐसी अस्थायी बग्स का मूल कारण होते हैं जिन्हें पुनर्उत्पादित करना मुश्किल होता है।

1. सेटअप और होल्ड समय उल्लंघन

ये तब होते हैं जब डेटा घड़ी के किनारे के संबंध में बहुत जल्दी या बहुत देर से आता है।

- लक्षण: लॉजिक एनालाइज़र के कैप्चर में डेटा क्षति या यादृच्छिक त्रुटियाँ।

- समाधान: घड़ी की गति को धीमा करें या PCB ट्रेस लंबाई को अनुकूलित करें।

2. घड़ी विचलन

घड़ी विचलन तब होता है जब घड़ी सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुँचता है।

- लक्षण: रेस स्थितियाँ जहाँ एक फ्लिप-फ्लॉप दूसरे के तैयार होने से पहले डेटा कैप्चर कर लेता है।

- समाधान: ट्रेस लंबाई को मैच करें या एक निर्दिष्ट घड़ी वितरण नेटवर्क का उपयोग करें।

3. प्रसारण देरी

सिग्नलों को तारों और गेट्स के माध्यम से यात्रा करने में समय लगता है। लंबे ट्रेस निर्णायक देरी जोड़ते हैं।

- लक्षण:उच्च गति वाली लाइनों पर सिग्नल अखंडता की समस्या या प्रतिबिंब।

- समाधान: टर्मिनेशन प्रतिरोधकों का उपयोग करें और ट्रेस को संभव हो उतना छोटा रखें।

4. अस्थिरता

जब असिंक्रोनस सिग्नल क्लॉक डोमेन को पार करते हैं, तो प्राप्त करने वाला फ्लिप-फ्लॉप एक अस्थिर अवस्था में प्रवेश कर सकता है।

- लक्षण: सिस्टम लटक जाता है या यादृच्छिक रीसेट होता है।

- समाधान: सिग्नल को हल करने के लिए सिंक्रोनाइज़र श्रृंखला (एक के बाद एक दो या अधिक फ्लिप-फ्लॉप) का उपयोग करें।

📝 दस्तावेज़ीकरण के लिए सर्वोत्तम प्रथाएं

दस्तावेज़ीकरण के लिए समय आरेख बनाने से यह सुनिश्चित होता है कि भविष्य के विकासकर्ता उपकरण को उलटे डिज़ाइन किए बिना भी प्रणाली को समझ सकें।

- सुसंगतता: प्रोजेक्ट के सभी आरेखों में मानक प्रतीकों और रेखा शैलियों का उपयोग करें।

- मापदंड: सुनिश्चित करें कि समय अक्ष रेखीय हो और इकाइयों (नैनोसेकंड, माइक्रोसेकंड, मिलीसेकंड) के साथ स्पष्ट रूप से लेबल किया गया हो।

- संदर्भ: हमेशा आरेख को विशिष्ट डेटाशीट खंड या प्रोटोकॉल मानक से जोड़ें।

- स्पष्टता: भारी बनावट से बचें। यदि कोई सिग्नल स्थिर है, तो उसे टॉगलिंग शोर के बजाय एक समतल रेखा के रूप में दिखाएं।

- संस्करण निर्धारण: हार्डवेयर या फर्मवेयर में महत्वपूर्ण परिवर्तन होने पर आरेखों को अद्यतन करें।

🔗 सिग्नल अखंडता पर अंतिम विचार

समय आरेख अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं। वे � ingineers को डिजिटल इलेक्ट्रॉनिक्स की अदृश्य सीमाओं को देखने में सक्षम बनाते हैं। उन्हें पढ़ने के लिए सीखने से आप जटिल हार्डवेयर समस्याओं का निदान कर सकते हैं। उन्हें बनाने के लिए सीखने से आप सभी परिस्थितियों में विश्वसनीय रूप से काम करने वाली टिकाऊ प्रणालियों का डिज़ाइन कर सकते हैं।

प्रक्रिया में धैर्य और विवरण में ध्यान लगता है। हर किनारा, हर देरी और हर वोल्टेज स्तर महत्वपूर्ण है। जैसे-जैसे एम्बेडेड प्रणालियां तेज और अधिक जटिल होती जाती हैं, सटीक समय आरेखों पर निर्भरता और बढ़ती जाएगी। उन्हें वैकल्पिक दस्तावेज़ीकरण के बजाय महत्वपूर्ण विनिर्देशों के रूप में लें।

अपने उपयोग किए जाने वाले घटकों के डेटाशीट का विश्लेषण करके शुरुआत करें। समय संबंधी विनिर्देशों को खोजें। फिर उन संख्याओं के आधार पर आरेख बनाने की कोशिश करें। अपने आरेखों की अपने उपकरणों से वास्तविक मापदंडों के साथ तुलना करें। इस भविष्यवाणी और पुष्टि के चक्र से उच्च स्तर के एम्बेडेड डिज़ाइन के लिए आवश्यक तर्कशक्ति विकसित होती है।

याद रखें कि एक आरेख संचार का एक उपकरण है। इसे दूसरे इंजीनियर को न्यूनतम अस्पष्टता के साथ आवश्यक जानकारी प्रसारित करनी चाहिए। स्पष्ट और सटीक समय आरेख विकास समय को कम करते हैं और महंगे हार्डवेयर संशोधनों को रोकते हैं। इस कौशल को सीखने के लिए समय निवेश करें, और यह आपके इंजीनियरिंग कैरियर में लाभ देगा।