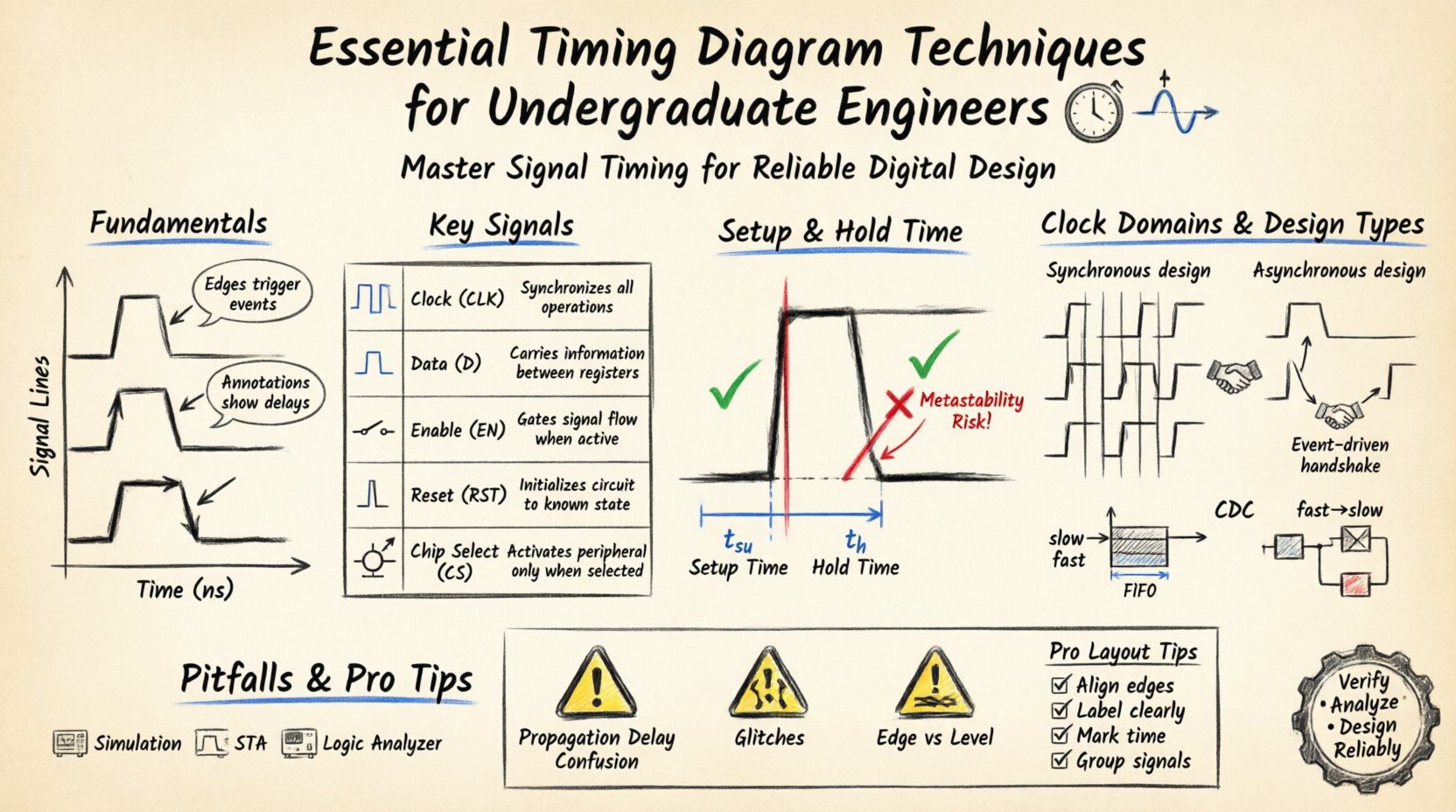

समय के साथ सिग्नल के प्रवाह को समझना डिजिटल इलेक्ट्रॉनिक्स के लिए मूलभूत है। स्नातक इंजीनियरों के लिए समय आरेखों की व्याख्या को समझना केवल एक शैक्षणिक अभ्यास नहीं है; यह विश्वसनीय प्रणालियों के डिज़ाइन के लिए एक महत्वपूर्ण कौशल है। इन दृश्य प्रतिनिधित्वों में समय अक्ष के साथ सिग्नलों के व्यवहार को दर्शाया जाता है, जो क्लॉक चक्करों, डेटा वैधता और नियंत्रण सिग्नलों के बीच संबंधों को उजागर करते हैं। इन तकनीकों को अच्छी तरह से समझे बिना, वास्तविक दुनिया की स्थितियों में यहां तक कि सरल परिपथ भी विफल हो सकते हैं।

यह मार्गदर्शिका समय आरेखों को पढ़ने, बनाने और विश्लेषण करने के लिए आवश्यक मूल सिद्धांतों को कवर करती है। हम सिंक्रोनस और एसिंक्रोनस डिज़ाइन के यांत्रिकी, सेटअप और होल्ड समय के महत्व, और परिपथ विफलता के कारण होने वाली आम गलतियों से बचने के तरीकों का अध्ययन करेंगे। इस लेख के अंत तक, आप जटिल डिजिटल लॉजिक समस्याओं का सामना करने के लिए एक ठोस आधार बना लेंगे।

1. समय आरेखों के मूल सिद्धांत 📐

एक समय आरेख समय के साथ सिग्नलों का एक आलेखीय प्रतिनिधित्व है। यह इंजीनियरों को डिजिटल परिपथ में विभिन्न लाइनों की स्थिति को देखने में सक्षम बनाता है। जैसे कि लॉजिक आरेख संबंधता दिखाते हैं, समय आरेख व्यवहार दिखाते हैं। इनका उपयोग डिबगिंग, डिज़ाइन की पुष्टि और हार्डवेयर मॉड्यूल के बीच सिग्नल अंतरक्रिया के संचार के लिए आवश्यक है।

समय आरेख के मुख्य घटक

- समय अक्ष (X-अक्ष): समय के प्रगति का प्रतिनिधित्व करता है। इसे आमतौर पर नैनोसेकंड (ns) या क्लॉक चक्करों में चिह्नित किया जाता है।

- सिग्नल लाइनें (Y-अक्ष): अलग-अलग तारों या बस का प्रतिनिधित्व करने वाली क्षैतिज रेखाएं। प्रत्येक रेखा एक विशिष्ट सिग्नल नाम के साथ मेल खाती है।

- लॉजिक स्तर: सिग्नल आमतौर पर द्विआधारी होते हैं, जिन्हें उच्च (1) या निम्न (0) के रूप में दर्शाया जाता है। कभी-कभी, बस डिज़ाइन में ‘हाई-ज़ी’ (उच्च प्रतिरोध) स्थितियां दिखाई देती हैं।

- किनारे: ऊर्ध्वाधर संक्रमण अवस्था में परिवर्तन को दर्शाते हैं। राइजिंग एज (निम्न से उच्च) और फॉलिंग एज (उच्च से निम्न) घटनाओं के तुरंत आरंभ करने के लिए महत्वपूर्ण हैं।

- अनोटेशन: पाठ लेबल आमतौर पर देरी, विशिष्ट समय या सिग्नल को प्रभावित करने वाली स्थितियों को दर्शाते हैं।

डिजिटल लॉजिक में समय का महत्व क्यों है

डिजिटल प्रणालियां सटीक समनिर्देशन पर निर्भर करती हैं। यदि कोई सिग्नल क्लॉक एज के सापेक्ष बहुत जल्दी या बहुत देर से आता है, तो प्रणाली डेटा के बारे में गलत व्याख्या कर सकती है। समय आरेख इन सीमाओं को दृश्यमान बनाते हैं। वे ऐसे प्रश्नों के उत्तर देने में मदद करते हैं जैसे:

- क्लॉक एज से पहले डेटा स्थिर है?

- एक गेट के माध्यम से सिग्नल को प्रसारित होने में कितना समय लगता है?

- क्या दो अलग-अलग क्षेत्रों से आने वाले क्लॉक एक-दूसरे के साथ अंतर्क्रिया करते हैं?

2. मुख्य सिग्नल और घटक ⚡

जटिल तरंगरूपों के विश्लेषण से पहले, आपको डिजिटल इंजीनियरिंग में उपयोग किए जाने वाले मानक सिग्नलों को पहचानना होगा। इन सिग्नलों के द्वारा डेटा के गतिशीलता और उसके वैध मान्यता के समय को निर्धारित किया जाता है।

सामान्य सिग्नल प्रकार

| सिग्नल नाम | कार्य | सामान्य व्यवहार |

|---|---|---|

| घड़ी (CLK) | समनिर्देशन स्रोत | 0 और 1 के बीच नियमित रूप से पल्सिंग |

| डेटा (D) | जानकारी वाहक | इनपुट या तर्क के आधार पर अवस्था बदलता है |

| सक्षम करें (EN) | एक मॉड्यूल को सक्रिय करता है | संचालन की अनुमति देने के लिए उच्च, अक्षम करने के लिए निम्न |

| रीसेट (RST) | अवस्था को प्रारंभ करता है | शुरुआत में सक्रिय निम्न या सक्रिय उच्च पल्स |

| चिप चयन (CS) | एक उपकरण का चयन करता है | विशिष्ट घटक को पता लगाने के लिए सक्रिय निम्न |

नियंत्रण संकेतों की सक्रिय अवस्था को समझना महत्वपूर्ण है। कुछ संकेत सक्रिय उच्च होते हैं, जिसका अर्थ है कि वे वोल्टेज उच्च होने पर कार्य करते हैं। अन्य सक्रिय निम्न होते हैं, जिन्हें नाम के ऊपर एक रेखा द्वारा दर्शाया जाता है (उदाहरण के लिए, /रीसेट या RST_N), जिसका अर्थ है कि वे वोल्टेज कम होने पर कार्य करते हैं।

3. सेटअप और होल्ड समय विश्लेषण 🕒

समय विश्लेषण के सबसे महत्वपूर्ण पहलुओं में से एक सेटअप और होल्ड समय का विश्लेषण है। इन पैरामीटर्स उस खंड को परिभाषित करते हैं जिसमें डेटा को क्लॉक किनारे के संबंध में स्थिर रहना चाहिए। इन सीमाओं के उल्लंघन से डेटा क्षति या मेटास्टेबिलिटी का खतरा होता है।

सेटअप समय (tsu)

सेटअप समय वह न्यूनतम अवधि है जिसके लिए डेटा स्थिर रहना चाहिए पहलेसक्रिय क्लॉक किनारे आने से पहले। यदि डेटा क्लॉक किनारे के बहुत निकट बदलता है, तो फ्लिप-फ्लॉप सही मान को कैप्चर नहीं कर सकता है।

- आवश्यकता:डेटा को tsuऊपरी किनारे से पहले स्थिर रहना चाहिए।

- उल्लंघन का परिणाम: रजिस्टर गलत डेटा को कैप्चर कर सकता है या अपरिभाषित स्थिति में प्रवेश कर सकता है।

होल्ड समय (th)

होल्ड समय वह न्यूनतम अवधि है जिसके दौरान डेटा स्थिर रहना चाहिएबाद में सक्रिय क्लॉक किनारे के बाद। फ्लिप-फ्लॉप को मान को लैच करने के लिए एक पल की आवश्यकता होती है जब तक नए डेटा के संभावित आगमन के पहले नहीं होता।

- आवश्यकता: डेटा को t के लिए स्थिर रहना चाहिएh उत्थान किनारे के बाद।

- उल्लंघन का परिणाम: सेटअप उल्लंघन के समान, इससे डेटा त्रुटियाँ या मेटास्टेबिलिटी होती है।

सेटअप और होल्ड समय को दृश्याकृत करना

जब टाइमिंग आरेख पढ़ते हैं, तो क्लॉक किनारे के संबंध में डेटा सिग्नल को देखें। सेटअप विंडो (पहले) और होल्ड विंडो (बाद में) के दौरान डेटा लाइन समतल और अपरिवर्तित होनी चाहिए। यदि डेटा लाइन इन विंडो में टॉगल होती है, तो डिज़ाइन संभवतः दोषपूर्ण है।

4. क्लॉक डोमेन क्रॉसिंग ⏱️

जटिल प्रणालियों में, सर्किट के अलग-अलग हिस्से अलग-अलग क्लॉक गति या आवृत्ति पर काम कर सकते हैं। इन अलग-अलग क्लॉक डोमेनों के बीच डेटा ले जाने को क्लॉक डोमेन क्रॉसिंग (CDC) कहा जाता है। इस प्रक्रिया में महत्वपूर्ण समय संबंधी चुनौतियाँ आती हैं।

क्लॉक डोमेन के प्रकार

- समान आवृत्ति, समान चरण: सिंक्रोनस डिज़ाइन। सरल समय विश्लेषण लागू होता है।

- समान आवृत्ति, अलग चरण: चरण समन्वय जांच की आवश्यकता होती है।

- अलग-अलग आवृत्तियाँ: हैंडशेक या FIFO बफर जैसी समन्वय तकनीकों की आवश्यकता होती है।

टाइमिंग आरेखों में CDC का प्रबंधन

जब बहु-क्लॉक डोमेन वाले आरेखों का विश्लेषण करते हैं, तो सुनिश्चित करें कि आप क्लॉक लाइनों के बीच स्पष्ट अंतर करें। यदि व्यवस्थित नहीं किया गया है, तो धीमे डोमेन से तेज़ डोमेन में डेटा का पारगमन जोखिम भरा हो सकता है। विपरीत रूप से, तेज़ से धीमे के पारगमन से डेटा के नुकसान का खतरा हो सकता है यदि प्राप्त करने वाला बहुत तेज़ी से नमूना लेता है।

- हैंडशेक प्रोटोकॉल: डेटा स्थानांतरण पूर्ण होने की पुष्टि करने के लिए वैध/तैयार सिग्नल का उपयोग करें।

- FIFO बफर: उत्पादन और उपभोग दरों को अलग करें।

- सिंक्रोनाइज़र्स: मेटास्टेबिलिटी के जोखिम को कम करने के लिए बहु-चरण फ्लिप-फ्लॉप का उपयोग करें।

5. सिंक्रोनस बनाम एसिंक्रोनस डिज़ाइन 🔄

डिज़ाइन आर्किटेक्चर निर्धारित करता है कि टाइमिंग डायग्राम कैसे दिखते हैं। अंतर को समझना सिग्नल व्यवहार के अनुमान लगाने में मदद करता है।

सिंक्रोनस डिज़ाइन

अधिकांश डिजिटल लॉजिक सिंक्रोनस होता है। सभी स्थिति परिवर्तन केंद्रीय क्लॉक सिग्नल के किनारे पर होते हैं।

- पूर्वानुमान योग्यता: समय नियंत्रित होने के कारण विश्लेषण करना आसान होता है।

- टाइमिंग डायग्राम: नियमित, ग्रिड-जैसे पैटर्न। डेटा परिवर्तन क्लॉक किनारों के साथ संरेखित होते हैं।

- सीमाएँ: बड़े डिज़ाइन में क्लॉक स्क्यू एक समस्या बन सकता है।

एसिंक्रोनस डिज़ाइन

स्थिति परिवर्तन सिग्नल के आगमन पर होते हैं, एक वैश्विक क्लॉक के बजाय। यह हैंडशेक प्रोटोकॉल और इंटरप्ट हैंडलिंग में सामान्य है।

- लचीलापन: विशिष्ट कार्यों के लिए तेज हो सकता है क्योंकि यह केवल डेटा के लिए प्रतीक्षा करता है।

- टाइमिंग डायग्राम: अनियमित। सिग्नल पिछली घटनाओं पर निर्भर करते हैं, न कि निश्चित समय के अंतराल पर।

- जोखिम: यदि ध्यान से डिज़ाइन नहीं किया गया है, तो रेस कंडीशन और खतरों के लिए अधिक झुकाव होता है।

6. सामान्य गलतियाँ और त्रुटियाँ ❌

यहाँ तक कि अनुभवी � ingineers टाइमिंग डायग्राम के व्याख्या या निर्माण करते समय गलतियाँ करते हैं। इन सामान्य त्रुटियों के बारे में जागरूक रहने से बड़े पैमाने पर डिबगिंग समय बच सकता है।

1. प्रसारण देरी को नजरअंदाज करना

सिग्नल तुरंत नहीं बदलते हैं। गेट्स में प्रसारण देरी होती है। यदि आप तुरंत परिवर्तन की धारणा के साथ एक डायग्राम बनाते हैं, तो आपका सिमुलेशन वास्तविकता से मेल नहीं खाएगा।

- सुधार: अपने डायग्राम में लॉजिक ट्रांज़िशन के बीच हमेशा देरी के मान शामिल करें।

2. एक्टिव लो सिग्नल के गलत व्याख्या करना

एक सिग्नल जिसे चिह्नित किया गया है/CS सक्रिय होने पर निम्न होता है। यदि आप मान लेते हैं कि यह उच्च है, तो आपकी लॉजिक उलट जाएगी।

- समाधान: सक्रिय अवस्थाओं के लिए डेटाशीट या आरेख की जांच करें। तर्क गेट पर बबल्स की तलाश करें।

3. ग्लिचेस को नजरअंदाज करना

ग्लिचेस छोटे, अनचाहे पल्स होते हैं। जब सिग्नल विभिन्न रास्तों से गुजरते हैं जिनमें अलग-अलग देरी होती है, तो ये उत्पन्न हो सकते हैं।

- समाधान: हाजर-फ्री तर्क का उपयोग करें या डिजाइन में फिल्टरिंग चरण जोड़ें।

4. किनारे बनाम स्तर में भ्रम

कुछ सर्किट राइजिंग किनारे पर ट्रिगर होते हैं, कुछ फॉलिंग किनारे पर, और कुछ स्तर पर ही।

- समाधान: घटक विवरण में ट्रिगर स्थिति की पुष्टि करें।

7. पेशेवर आरेख पढ़ना और बनाना 📝

स्पष्ट संचार इंजीनियरिंग में बहुत महत्वपूर्ण है। एक अच्छी तरह से बनाया गया समय आरेख एक नजर में जटिल जानकारी संचारित करता है। इनके निर्माण के लिए बेस्ट प्रैक्टिसेज यहां दी गई हैं।

लेआउट के लिए बेस्ट प्रैक्टिसेज

- किनारों को समायोजित करें: सुनिश्चित करें कि संबंधित सिग्नल निरंतर अंतराल पर बदलते हैं।

- स्पष्ट रूप से लेबल करें: केवल सामान्य रेखाओं के बजाय सिग्नल नामों का उपयोग करें।

- समय को चिह्नित करें: चक्करों या विशिष्ट देरी की अवधि को चिह्नित करें।

- सिग्नलों को समूहित करें: संबंधित सिग्नलों (जैसे डेटा बस लाइनें) को एक साथ व्यवस्थित करें।

चरण-दर-चरण निर्माण प्रक्रिया

- घड़ी को पहचानें: सबसे पहले घड़ी की रेखाएं बनाएं। वे समय की रीढ़ हैं।

- नियंत्रण सिग्नल जोड़ें: एनेबल, रीसेट और चिप सेलेक्ट लाइनें रखें।

- डेटा को बनाएं: तर्क प्रवाह के आधार पर डेटा लाइनें जोड़ें।

- टिप्पणी करें: सेटअप/होल्ड समय या विशिष्ट देरी के लिए नोट जोड़ें।

- समीक्षा: उल्लंघनों और तार्किक सुसंगतता की जांच करें।

8. वास्तविक दुनिया के परिदृश्यों का विश्लेषण 🔍

आइए एक स्मृति पठन क्रिया से जुड़े परिदृश्य पर विचार करें। यह माइक्रोकंट्रोलर्स के साथ काम कर रहे इंजीनियरों के लिए एक सामान्य कार्य है।

स्मृति पठन चक्र

एक स्मृति पठन में, प्रोसेसर एक पता भेजता है, पठन आदेश को सक्रिय करता है, और डेटा के लिए प्रतीक्षा करता है।

- पता बस: क्लॉक किनारे से पहले मान्य।

- चिप चयन: स्मृति को सक्रिय करने के लिए नीचे जाता है।

- पठन आदेश: स्थानांतरण शुरू करने के लिए नीचे जाता है।

- डेटा बस: स्मृति द्वारा इसे चलाने तक हाई-जी में रहता है।

- समय सीमा: प्रोसेसर द्वारा इसे नमूना लेने से पहले डेटा स्थिर होना चाहिए।

सिग्नल अखंडता पर विचार

जैसे-जैसे आवृत्ति बढ़ती है, सिग्नल अखंडता एक महत्वपूर्ण कारक बन जाती है। प्रतिबिंब, क्रॉसटॉक और शोर तरंग आकृतियों को विकृत कर सकते हैं। उच्च गति डिजाइन में समय आरेखों को इन भौतिक परत की समस्याओं को ध्यान में रखना चाहिए।

- स्ल्यू दर: सिग्नल के संक्रमण की गति। बहुत तेज होने से शोर उत्पन्न होता है; बहुत धीमा होने से समय सीमा त्रुटियाँ होती हैं।

- वोल्टेज स्तर: तापमान और वोल्टेज परिवर्तनों के दौरान लॉजिक प्रांतों को पूरा करने की गारंटी दें।

9. उन्नत समय संकल्पनाएँ 🧠

जो लोग अपने विशेषज्ञता को गहरा करना चाहते हैं, उनके लिए कई उन्नत अवधारणाएँ मूल समय विश्लेषण को बढ़ाती हैं।

अस्थिरता

अस्थिरता तब होती है जब फ्लिप-फ्लॉप आवश्यक समय के भीतर एक स्थिर 0 या 1 अवस्था में निर्णय नहीं ले पाता है। यह आमतौर पर तब होता है जब डेटा क्लॉक किनारे के बहुत निकट बदलता है।

- संभावना: यह एक संभाव्य घटना है, निश्चित नहीं।

- उपाय: संभावना को लगभग शून्य तक कम करने के लिए सिंक्रोनाइज़र श्रृंखला (श्रृंखला में बहुत से फ्लिप-फ्लॉप) का उपयोग करें।

घड़ी विचलन

घड़ी विचलन सर्किट के विभिन्न हिस्सों में घड़ी सिग्नल के आगमन समय के बीच का अंतर है। सकारात्मक विचलन (बाद में आता है) सेटअप समय में मदद कर सकता है, लेकिन होल्ड समय को नुकसान पहुँचा सकता है। ऋणात्मक विचलन इसके विपरीत करता है।

- डिज़ाइन प्रभाव: समय बजट में विचलन को ध्यान में रखना आवश्यक है।

- मापन: विचलन को मापने के लिए ऑसीलोस्कोप या सिमुलेशन उपकरणों का उपयोग करें।

जिटर

जिटर घड़ी के किनारे के आदर्श स्थान से विचलन है। यह प्रभावी सेटअप और होल्ड मार्जिन को कम करता है।

- प्रकार: आवर्ती जिटर, साइकिल-टू-साइकिल जिटर, और यादृच्छिक जिटर।

- प्रभाव: उच्च जिटर सिस्टम की अधिकतम संचालन आवृत्ति को सीमित करता है।

10. उपकरण और पद्धतियाँ 🛠️

जबकि हाथ से विश्लेषण शैक्षिक है, आधुनिक � ingineering उपकरणों पर निर्भर है। हालांकि, आधारभूत सिद्धांत को समझना ही आपको इन उपकरणों का प्रभावी रूप से उपयोग करने में सक्षम बनाता है।

सिमुलेशन सॉफ्टवेयर

हार्डवेयर वर्णन भाषाएँ (HDL) सिमुलेशन की अनुमति देती हैं। इन उपकरणों को कोड से स्वचालित रूप से समय आरेख उत्पन्न करने की अनुमति मिलती है। आपको कोड की सहीता की पुष्टि करने के लिए आउटपुट को समझना होगा।

स्थैतिक समय विश्लेषण (STA)

STA उपकरण गणितीय रूप से यह सत्यापित करते हैं कि सभी मार्ग सिमुलेशन के बिना समय सीमाओं को पूरा करते हैं। वे सभी कोनों (तापमान, वोल्टेज) में सेटअप और होल्ड उल्लंघन की जांच करते हैं।

लॉजिक एनालाइज़र के साथ डीबगिंग

हार्डवेयर डीबगर बोर्ड से वास्तविक सिग्नल को कैप्चर करते हैं। वे समय आरेख प्रदर्शित करते हैं जो वास्तविकता के अनुरूप होते हैं, जिससे सिमुलेशन द्वारा छूट जाने वाली भौतिक परत की समस्याओं को पहचानने में मदद मिलती है।

निष्कर्ष 🏁

समय आरेख डिजिटल सिग्नल व्यवहार की भाषा हैं। वे अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं। स्नातक इंजीनियरों के लिए इन तकनीकों को समझने में समय निवेश करना आपके कैरियर भर लाभ देता है। चाहे आप एक सरल काउंटर या एक जटिल प्रोसेसर का डिज़ाइन कर रहे हों, समय सीमाओं को पढ़ने और विश्लेषण करने की क्षमता अनिवार्य है।

सेटअप और होल्ड समय पर ध्यान केंद्रित करने, घड़ी क्षेत्रों को समझने और सामान्य त्रुटियों से बचने के द्वारा आप एक मजबूत आधार बनाते हैं। हमेशा सक्रिय अवस्थाओं की पुष्टि करने और प्रसारण देरी को ध्यान में रखने की याद रखें। जैसे-जैसे आप आगे बढ़ेंगे, आपको अधिक जटिल परिस्थितियों का सामना करना पड़ेगा, लेकिन मूल सिद्धांत वही रहेंगे। आरेख विश्लेषण के अभ्यास जारी रखें, और आपके डिज़ाइन अधिक विश्वसनीय और कुशल होंगे।

डेटाशीट्स का अध्ययन करने और वास्तविक दुनिया के सर्किट तरंगरूपों का अध्ययन करके अपने कौशल को आगे बढ़ाते रहें। डिजिटल इंजीनियरिंग के क्षेत्र में तेजी से बदलाव आता है, लेकिन समय विश्लेषण के मूल सिद्धांत अपरिवर्तित रहते हैं।