आधुनिक डिजिटल डिज़ाइन में, समय के आधार पर सिग्नल के प्रवाह को समझना सिस्टम की विश्वसनीयता सुनिश्चित करने के लिए महत्वपूर्ण है। असमान सिस्टम, जहां संचालन एकल वैश्विक घड़ी द्वारा नियंत्रित नहीं होते, समान सिस्टम की तुलना में विशिष्ट चुनौतियां प्रस्तुत करते हैं। इन जटिल बातचीत को दृश्याकृत करने और डिबग करने के लिए प्राथमिक उपकरण समय आरेख है। यह मार्गदर्शिका असमान वातावरण में समय आरेखों के निर्माण, पढ़ने और विश्लेषण के तरीकों के बारे में गहन जानकारी प्रदान करती है।

असमान डिज़ाइन की प्रकृति 🌐

असमान सिस्टम एक केंद्रीकृत घड़ी सिग्नल के बिना चलते हैं जो हर राज्य परिवर्तन को संचालित करता है। इसके बजाय, घटनाएं पिछले संचालन के समापन या डेटा के आगमन द्वारा उत्पन्न होती हैं। इस दृष्टिकोण के लाभ शामिल हैं जैसे कि शक्ति की खपत कम करना और विशिष्ट संदर्भों में उच्च संभावित प्रदर्शन। हालांकि, यह सिग्नल समकालिकता और समय जांच के संबंध में जटिलता लाता है।

जब � ingineers इन सिस्टमों का विश्लेषण करते हैं, तो वे चर देरी, प्रसार समय और एक सार्वभौमिक संदर्भ बिंदु की कमी को ध्यान में रखने की आवश्यकता होती है। समय आरेख इन घटनाओं को मैप करने के लिए दृश्य भाषा के रूप में कार्य करते हैं। वे टीमों को समय के साथ सिग्नल संक्रमणों के बीच सटीक संबंध देखने में सक्षम बनाते हैं।

समय आरेख की रचना 📐

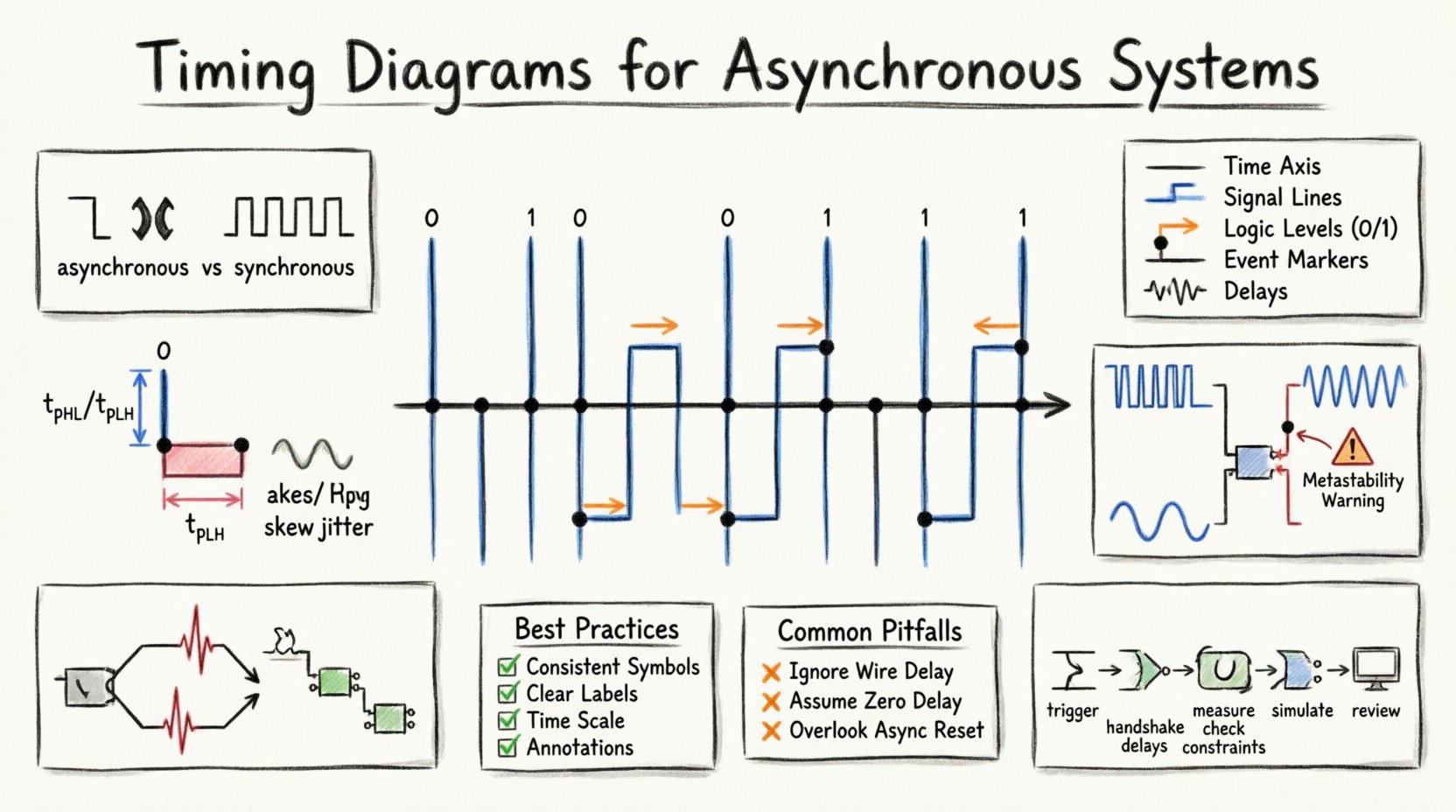

एक समय आरेख सिग्नल व्यवहार का एक आलेखीय प्रतिनिधित्व है। इसमें समय को क्षैतिज अक्ष के साथ और सिग्नल अवस्थाओं को ऊर्ध्वाधर अक्ष के साथ दर्शाया जाता है। एक असमान सिस्टम के प्रभावी विश्लेषण के लिए, इन आरेखों को बनाने वाले मूल घटकों को समझना आवश्यक है।

- समय अक्ष: समय के प्रगति का प्रतिनिधित्व करता है। असमान विश्लेषण में, इसका अक्सर एक विशिष्ट घटना ट्रिगर के संदर्भ में होना चाहिए, घड़ी चक्कर के बजाय।

- सिग्नल रेखाएं: विशिष्ट तारों या नेट्स का प्रतिनिधित्व करने वाली क्षैतिज रेखाएं। प्रत्येक रेखा एक विशिष्ट सिग्नल के लॉजिक स्तर (उच्च, निम्न या अज्ञात) का अनुसरण करती है।

- लॉजिक स्तर: आमतौर पर

0(निम्न/भूमि) और1(उच्च/VCC) के रूप में दर्शाया जाता है। इन अवस्थाओं के बीच संक्रमण विश्लेषण का केंद्र बिंदु है। - घटना चिह्न: विशिष्ट घटनाओं को दर्शाने वाली ऊर्ध्वाधर रेखाएं या अनोतेशन, जैसे कि हैंडशेक सिग्नल की अवस्था बदलना।

- देरी: इनपुट परिवर्तन और संबंधित आउटपुट परिवर्तन के बीच दृश्य अंतराल, जो प्रसार देरी का प्रतिनिधित्व करता है।

समान आरेखों के विपरीत जो घड़ी के किनारों का प्रतिनिधित्व करने वाली ग्रिड रेखाओं पर निर्भर होते हैं, असमान आरेख घटना सीमाओं पर निर्भर होते हैं। इसके लिए संक्रमणों के बीच दूरी के अधिक सावधानी से व्याख्या करने की आवश्यकता होती है।

महत्वपूर्ण समय संबंधी पैरामीटर ⚙️

एक असमान सिस्टम की अखंडता का विश्लेषण करने के लिए, विशिष्ट समय संबंधी पैरामीटरों को मापना और डिज़ाइन विनिर्देशों के बीच तुलना करना आवश्यक है। इन पैरामीटरों द्वारा वह खंड निर्धारित किया जाता है जिसमें एक सिग्नल को स्थिर रहना चाहिए ताकि एक ग्राहक द्वारा सही तरीके से व्याख्या किया जा सके।

प्रसार देरी

प्रसार देरी उस समय को दर्शाती है जो एक सिग्नल के घटक के इनपुट से आउटपुट तक यात्रा करने में लगता है। असमान तर्क में, यह देरी अनिश्चितता का प्राथमिक स्रोत है। उत्पादन, तापमान और वोल्टेज में भिन्नता इस देरी को बदल सकती है।

- tpHL: सिग्नल के उच्च से निम्न में संक्रमण करने में लगने वाला समय।

- tpLH: सिग्नल के निम्न से उच्च में संक्रमण करने में लगने वाला समय।

- tpd: सामान्य प्रसारण देरी, जो अक्सर tpHL और tpLH के औसत के रूप में गणना की जाती है।

जब किसी समय आरेख का विश्लेषण कर रहे हों, तो इनपुट किनारे और परिणामी आउटपुट किनारे के बीच क्षैतिज दूरी को देखें। यह दूरी प्रसारण देरी है।

सेटअप और होल्ड समय

असिंक्रोनस प्रणालियों में भी, फ्लिप-फ्लॉप और लॉचेस को अक्सर विशिष्ट स्थिरता के खंडों की आवश्यकता होती है। सेटअप समय वह अवधि है जो एक त्रिज्या घटना से पहले होती है, जिसमें डेटा स्थिर होना चाहिए। होल्ड समय वह अवधि है जो त्रिज्या घटना के बाद होती है, जिसमें डेटा स्थिर रहना चाहिए।

यदि इन खंडों का उल्लंघन किया जाता है, तो प्रणाली एक अस्थिर अवस्था में प्रवेश कर सकती है, जहां आउटपुट न तो उच्च है और न ही निम्न, बल्कि एक अपरिभाषित वोल्टेज स्तर है। समय आरेख इन उल्लंघनों को दिखाने में मदद करते हैं, जब डेटा नियंत्रण किनारे के बहुत निकट बदलता है।

स्क्यू और जिटर

- S स्क्यू: परिपथ के दो अलग-अलग बिंदुओं पर एक ही सिग्नल के आगमन समय का अंतर।

- जिटर: सिग्नल समय में अल्पकालिक भिन्नताएं। असिंक्रोनस प्रणालियों में, जिटर पावर शोर या क्रॉसटॉक के कारण हो सकता है।

घड़ी क्षेत्र पार करना 🔄

मिश्रित मोड प्रणालियों में त्रुटियों के सबसे सामान्य स्रोतों में से एक विभिन्न घड़ी क्षेत्रों के बीच पार करना है। भले ही कोई प्रणाली मुख्य रूप से असिंक्रोनस हो, लेकिन अक्सर विभिन्न आवृत्तियों पर काम करने वाले सिंक्रोनस उप-ब्लॉक्स शामिल होते हैं। समय आरेख इन पार करने की जांच करने के लिए आवश्यक हैं।

जब कोई सिग्नल एक घड़ी क्षेत्र से दूसरे घड़ी क्षेत्र में जाता है, तो रिसीवर सिग्नल को उस समय नमूना ले सकता है जब सिग्नल बदल रहा होता है। इससे अस्थिर अवस्था होती है। इसके बचाव के लिए मानक तरीका एक सिंक्रोनाइज़र का उपयोग करना है, जो आमतौर पर फ्लिप-फ्लॉप की श्रृंखला होती है।

| पैरामीटर | विवरण | समय आरेख पर प्रभाव |

|---|---|---|

| अस्थिरता समाधान समय | सिंक्रोनाइज़र द्वारा वैध लॉजिक स्तर तक पहुंचने के लिए आवश्यक समय | सिग्नल स्थिर होने से पहले अपरिभाषित अवस्था की विस्तारित अवधि दिखाता है |

| क्रॉस डोमेन लेटेंसी | सिंक्रोनाइज़र द्वारा पेश की गई अतिरिक्त देरी | स्रोत घटना और गंतव्य घटना के बीच समय के अंतर को बढ़ाता है |

| हैंडशेक लेटेंसी | असिंक्रोनस प्रोटोकॉल में पुष्टि सिग्नल के लिए लिया गया समय | सिग्नल समय रेखा में आगे-पीछे का पैटर्न बनाता है |

विश्लेषकों को यह सुनिश्चित करना चाहिए कि समय आरेख समाधान समय को ध्यान में रखे। यदि नीचे के ब्लॉक सिंक्रोनाइज़र के समाधान से पहले सिग्नल को पढ़ने की कोशिश करता है, तो डेटा क्षति होती है।

रेस कंडीशन की पहचान और समाधान ⚠️

एक रेस कंडीशन तब होता है जब प्रणाली का व्यवहार उन घटनाओं के सापेक्ष समय पर निर्भर करता है जो एक-दूसरे को प्रभावित नहीं करना चाहिए। असिंक्रोनस लॉजिक में, यह एक बार-बार चिंता का विषय है। समय आरेख इन शर्तों का पता लगाने का प्राथमिक तरीका है।

स्थैतिक हाजर्ड

एक स्थिर खतरा तब होता है जब एक सिग्नल को एक स्थिर स्तर पर रहना चाहिए, लेकिन पथ देरी के कारण अचानक उलट जाता है। उदाहरण के लिए, यदि एक सिग्नल को तार्किक रूप से हाई रहना चाहिए, लेकिन इनपुट में परिवर्तन के कारण लो की एक छोटी अवधि के लिए गिर जाता है, तो इसे स्थिर-1 खतरा कहा जाता है।

- दृश्य संकेतक:एक सिग्नल लाइन पर एक संकीर्ण शीर्ष या पल्स जो समतल होना चाहिए।

- मूल कारण:विभिन्न लॉजिक गेट्स के माध्यम से असमान प्रसार देरी।

गतिशील खतरे

गतिशील खतरे में एक ही संकेत के बजाय एक से अधिक संक्रमण शामिल होते हैं। यह अक्सर जटिल लॉजिक पथों में होता है जहां सिग्नल विभिन्न संख्या में गेट्स के माध्यम से यात्रा करते हैं।

रेस स्थितियों के लिए विश्लेषण चरण

- पथों का अनुसरण करें:स्रोत से गंतव्य तक सिग्नल के सभी पथों की पहचान करें।

- देरी को मापें:समय आरेख का उपयोग करके प्रत्येक पथ के लिए देरी की गणना करें।

- किनारों की तुलना करें:जांचें कि प्रतिस्पर्धी सिग्नलों के आगमन समय एक ऐसे तरीके से ओवरलैप नहीं करते हैं जिससे अस्पष्टता उत्पन्न हो।

- स्थिरता की पुष्टि करें:यह सुनिश्चित करें कि नियंत्रण सिग्नल डेटा आगमन की महत्वपूर्ण खिड़की के दौरान स्थिर रहें।

यदि एक रेस स्थिति पाई जाती है, तो डिज़ाइन को पुनर्गठित करने की आवश्यकता हो सकती है। सामान्य समाधानों में देरी को समान करने के लिए बफर जोड़ना, हैंडशेक प्रोटोकॉल सम्मिलित करना, या असिंक्रोनस FIFO संरचनाओं का उपयोग करना शामिल है।

सिग्नल अखंडता और शोर संबंधी विचार 🔌

समय आरेख एक निर्जीव वातावरण में नहीं होते हैं। भौतिक परत शोर लाती है जो सिग्नल गुणवत्ता को प्रभावित करता है। असिंक्रोनस प्रणालियों के विश्लेषण के दौरान, � ingineers को तार्किक समय त्रुटियों और भौतिक सिग्नल विकृति के बीच अंतर करना चाहिए।

सिग्नल ग्लिचेस

ग्लिचेस छोटे जीवनकाल वाले पल्स होते हैं जो परिपथ में प्रसारित हो सकते हैं। असिंक्रोनस प्रणालियों में, एक ग्लिच लैच या फ्लिप-फ्लॉप को गलत तरीके से ट्रिगर कर सकता है। समय आरेख अक्सर इन्हें पतले शीर्ष के रूप में दिखाते हैं।

- फ़िल्टरिंग:यह सुनिश्चित करें कि निचले लॉजिक में इन पल्स को फ़िल्टर करने के लिए पर्याप्त देरी हो।

- किनारे की दर:अधिक तीखे किनारे (तेज उठाने/गिराने के समय) शोर के संयोजन के प्रति अधिक संवेदनशील होते हैं।

क्रॉसटॉक

क्रॉसटॉक तब होता है जब एक तार पर सिग्नल एक पड़ोसी तार पर वोल्टेज उत्पन्न करता है। इससे सिग्नल के समय को बदला जा सकता है, जिससे यह अपेक्षित समय से पहले या बाद में आने लगता है।

समय आरेख में, क्रॉसटॉक किनारे की स्थिति में विस्थापन या अतिरिक्त शोर शीर्ष के रूप में दिखाई दे सकता है। इसके निवारण के लिए, भौतिक डिज़ाइन चरण के दौरान सिग्नलों के बीच दूरी को ध्यान में रखना आवश्यक है।

दस्तावेज़ीकरण के लिए सर्वोत्तम प्रथाएं 📝

स्पष्ट दस्तावेज़ीकरण सुनिश्चित करता है कि समय विश्लेषण को दूसरे इंजीनियरों द्वारा पुनर्निर्मित और समझा जा सके। एक अच्छी तरह से संरचित समय आरेख में विशिष्ट मेटाडेटा और टिप्पणियां शामिल होती हैं।

मानकीकरण

- तर्क स्तरों के लिए स्थिर प्रतीकों का उपयोग करें।

- सभी सिग्नलों को उनके कार्य के साथ स्पष्ट रूप से लेबल करें।

- समय मापदंड को स्पष्ट रूप से दर्शाएं (उदाहरण के लिए, प्रति विभाजन नैनोसेकंड)।

अनुमान

प्रतिवेदन के विशिष्ट व्यवहार को समझाने के लिए पाठ अनुमान अत्यंत महत्वपूर्ण हैं। महत्वपूर्ण संक्रमण या संभावित समस्या क्षेत्रों को इंगित करने के लिए तीर का उपयोग करें। प्रसारण देरी के मानों को सीधे आरेख पर लेबल करें।

संस्करण नियंत्रण

डिज़ाइन में परिवर्तन होने पर समय आरेख विकसित होते हैं। विश्लेषण के लिए वर्तमान हार्डवेयर स्थिति के अनुरूप होने की गारंटी के लिए सभी आरेखों के लिए संस्करण संख्या बनाए रखें। समय संबंधी विवरणों के लिए स्मृति पर भरोसा न करें।

चरण-दर-चरण विश्लेषण प्रक्रिया 🛠️

एक असमान सिस्टम के प्रभावी विश्लेषण के लिए, एक संरचित दृष्टिकोण का पालन करें। इससे यह सुनिश्चित होता है कि कोई भी महत्वपूर्ण समय संबंधी पैरामीटर न छूटे।

- ट्रिगर को परिभाषित करें:वह घटना की पहचान करें जो अनुक्रम की शुरुआत करती है। आमतौर पर यह समय अक्ष का शुरुआती बिंदु होता है।

- हैंडशेक को नक्शा बनाएं:अनुरोध और स्वीकृति सिग्नल का अनुसरण करें। सुनिश्चित करें कि वे सही प्रोटोकॉल का पालन करते हैं (उदाहरण के लिए, चार चरण या दो चरण हैंडशेक)।

- देरी को मापें:ट्रिगर से अंतिम आउटपुट तक की कुल देरी की गणना करें। इसे घटक देरी में विभाजित करें।

- प्रतिबंधों की जांच करें:सुनिश्चित करें कि सभी शामिल स्टोरेज तत्वों के लिए सेटअप और होल्ड समय पूरे हो रहे हैं।

- परिवर्तनों का सिमुलेशन करें:अधिकतम तापमान या न्यूनतम वोल्टेज जैसी न्यूनतम स्थितियों के तहत आरेख का विश्लेषण करें।

- मेटास्टेबिलिटी की समीक्षा करें:सिंक्रोनाइज़र के माध्यम से मेटास्टेबिलिटी की संभावना को स्वीकार्य स्तर तक कम करने की गारंटी दें।

समय विश्लेषण में आम त्रुटियाँ ⚡

यहां तक कि अनुभवी � ingineers भी सूक्ष्म समस्याओं को छोड़ सकते हैं। आम त्रुटियों के बारे में जागरूक रहने से लागत वाले पुनर्डिज़ाइन से बचा जा सकता है।

- वायर देरी को नजरअंदाज करना:इंटरकनेक्ट्स के प्रतिरोध और धारिता को नजरअंदाज करते हुए केवल गेट देरी पर भरोसा करना।

- शून्य देरी मानना:फीडबैक लूप को तत्काल मानना, जो भौतिक रूप से असंभव है।

- असमान रीसेट को नजरअंदाज करना:डेटा सिग्नलों के सापेक्ष रीसेट सिग्नलों के समय को ध्यान में न रखना।

- किनारे और स्तर को भ्रमित करना: आरेख के व्याख्या में किनारा-द्वारित और स्तर-द्वारित व्यवहार को गलती से मिलाना।

सत्यापन पर निष्कर्ष ✅

समय-आधारित आरेख असिंक्रोनस प्रणालियों के सत्यापन के लिए अनिवार्य हैं। वे अमूर्त समय संबंधों का एक ठोस दृश्य प्रतिनिधित्व प्रदान करते हैं। इन आरेखों के तीव्र विश्लेषण से इंजीनियर रेस स्थितियों की पहचान कर सकते हैं, हैंडशेक प्रोटोकॉल की पुष्टि कर सकते हैं और सिग्नल अखंडता सुनिश्चित कर सकते हैं।

असिंक्रोनस डिजाइन की जटिलता सटीकता की मांग करती है। हर नैनोसेकंड महत्वपूर्ण है। प्रसारण देरी, सेटअप समय और होल्ड समय की गहन समझ से लचीली प्रणालियों का निर्माण संभव होता है। जबकि एक वैश्विक घड़ी के अभाव से कठिनाई बढ़ती है, विस्तृत समय विश्लेषण से प्राप्त ज्ञान अधिक कुशल और विश्वसनीय डिजाइनों की ओर ले जाता है।

इन विश्लेषण कौशल को आगे बढ़ाते रहने से यह सुनिश्चित होता है कि प्रणालियां विभिन्न पर्यावरणीय स्थितियों में सही तरीके से काम करें। लक्ष्य स्थिरता और पूर्वानुमान क्षमता है, जो ध्यान से दस्तावेजीकरण और माप के माध्यम से प्राप्त की जाती है।

उन्नत विचारों 🔬

उच्च प्रदर्शन वाले अनुप्रयोगों के लिए, अतिरिक्त कारक महत्वपूर्ण होते हैं। इनमें चिप के आर-पार तापमान ढलान और स्विचिंग घटनाओं के दौरान वोल्टेज गिरावट शामिल हैं।

- तापमान ढलान: चिप के गर्म केंद्र से ठंडे किनारे तक यात्रा करने वाले सिग्नलों को अलग-अलग गति का अनुभव होगा। इस भिन्नता को समय विश्लेषण में प्रतिबिंबित करना आवश्यक है।

- पावर ग्रिड शोर: समानांतर स्विचिंग शोर स्थिति के स्तर को बदल सकता है। समय आरेखों में आदर्श रूप से पावर रेल स्थिरता का प्रतिनिधित्व शामिल होना चाहिए।

- चर लेटेंसी: कुछ असिंक्रोनस प्रोटोकॉल में चर लेटेंसी की अनुमति होती है। समय आरेख में स्वीकार्य लेटेंसी की सीमा को दिखाना आवश्यक है, केवल एक मान के बजाय।

इन उन्नत विचारों को शामिल करने से समय विश्लेषण एक समग्र उपकरण बन जाता है प्रणाली के सत्यापन के लिए। यह सरल सत्यापन से आगे बढ़कर वास्तविक प्रदर्शन अनुकूलन तक पहुंचता है।

याद रखें कि समय केवल गति के बारे में नहीं है; यह सही होने के बारे में है। समय त्रुटियों के कारण विफल होने वाली तेज प्रणाली, विश्वसनीय रूप से काम करने वाली धीमी प्रणाली से कम उपयोगी है। समय आरेख वह नक्शा है जो आपको उस विश्वसनीयता तक ले जाता है।