डिजिटल प्रणाली के भीतर सिग्नल के प्रवाह को समझना हार्डवेयर, फर्मवेयर या एम्बेडेड सॉफ्टवेयर पर काम कर रहे � ingineers के लिए महत्वपूर्ण है। एक समय आरेख एक विशिष्ट अवधि के दौरान विभिन्न सिग्नलों के बीच बातचीत को नक्शा बनाने के लिए मुख्य दृश्य उपकरण के रूप में कार्य करता है। इस दृश्य प्रस्तुतीकरण के कारण टीमें यह सत्यापित कर सकती हैं कि डेटा सही तरीके से ली जा रही है, घड़ी स्थिर है, और तर्क संक्रमण बिना दुर्घटना के हो रहे हैं। इन आरेखों की सटीक समझ के बिना, प्रणाली की विश्वसनीयता में गंभीर कमी आ सकती है। यह मार्गदर्शिका समय आरेख के बनने वाले मूल तत्वों का अध्ययन करती है, जिससे डिजाइन और विश्लेषण सही हो सके।

समय आरेख क्या है? 📊

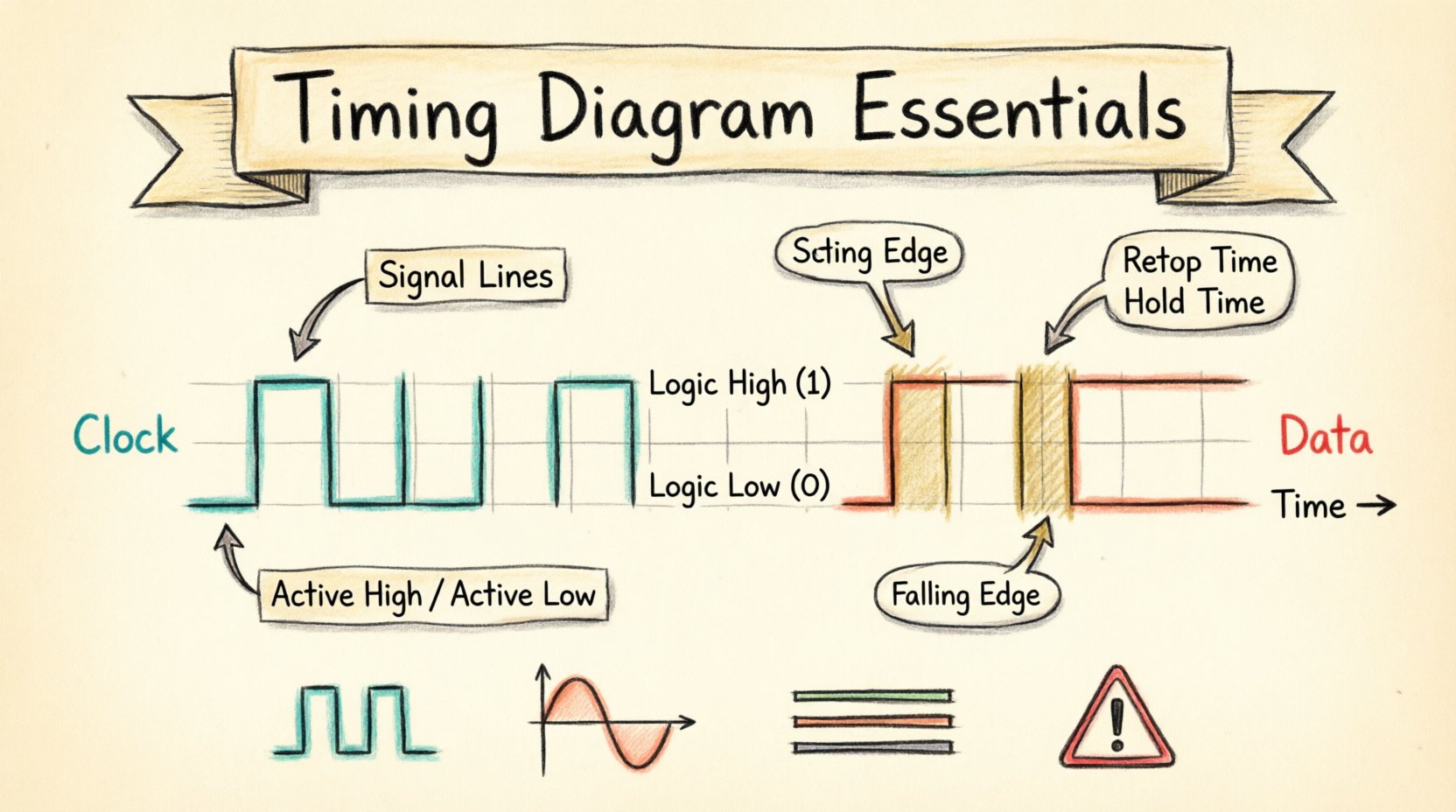

एक समय आरेख एक ग्राफिकल चित्र है जो समय के दौरान दो या अधिक सिग्नलों के व्यवहार को दर्शाता है। यह घटनाओं के क्रम को नक्शा बनाता है, जिसमें बताया जाता है कि सिग्नल कब अवस्था बदलते हैं, वे कितनी देर तक उस अवस्था में रहते हैं, और वे घड़ी स्रोत से कैसे संबंधित हैं। हार्डवेयर डिजाइन में, इन आरेखों का उपयोग घटकों के सही संचार की जांच करने के लिए अनिवार्य है। सॉफ्टवेयर में, इनका उपयोग समानांतरता, दौड़ स्थितियों और समन्वय बिंदुओं को दृश्य रूप से देखने में मदद करता है।

इन आरेखों में आमतौर पर समय को क्षैतिज अक्ष (x-अक्ष) पर और सिग्नल स्तर या अवस्था को ऊर्ध्वाधर अक्ष (y-अक्ष) पर दर्शाया जाता है। ऊर्ध्वाधर रेखाएं समय के विशिष्ट बिंदुओं का प्रतिनिधित्व करती हैं, जबकि क्षैतिज रेखाएं सिग्नल की स्थिर अवस्था को दर्शाती हैं। इन अवस्थाओं के बीच के संक्रमण महत्वपूर्ण हैं, क्योंकि वे वास्तविक डेटा स्थानांतरण या प्रणाली के भीतर हो रहे नियंत्रण क्रियाकलापों को दर्शाते हैं।

समय आरेख के मुख्य घटक 🔧

एक प्रभावी समय आरेख को पढ़ने या बनाने के लिए, एक को मूल निर्माण तत्वों को समझना आवश्यक है। प्रत्येक आरेख, जटिलता के बावजूद, सूचना को सही तरीके से प्रस्तुत करने के लिए एक स्थिर सेट तत्वों पर निर्भर करता है।

- समय अक्ष: समय के प्रगति का क्षैतिज आधार रेखा। यह आमतौर पर बाएं से दाएं बहती है, जो “अतीत” से “भविष्य” को दर्शाती है।

- सिग्नल रेखाएं: विशिष्ट तारों, बसों या चरों के लिए निर्धारित क्षैतिज ट्रैक। प्रत्येक रेखा एक विशिष्ट सिग्नल के तर्क स्तर का प्रतिनिधित्व करती है।

- तर्क स्तर: सिग्नल रेखा पर ऊर्ध्वाधर स्थितियां। आमतौर पर उच्च (1, Vcc, सत्य) और निम्न (0, Gnd, असत्य) अवस्थाएं दिखाई जाती हैं।

- संक्रमण: तर्क स्तरों को जोड़ने वाली ऊर्ध्वाधर रेखाएं। एक बढ़ता किनारा निम्न से उच्च की ओर जाता है, जबकि एक गिरता किनारा उच्च से निम्न की ओर जाता है।

- अनोटेशन: विशिष्ट घटनाओं, देरी या अवस्थाओं को स्पष्ट करने वाले पाठ लेबल या चिह्न।

समय अक्ष: सटीकता महत्वपूर्ण है ⏳

समय अक्ष आरेख की नींव है। यह हमेशा वास्तविक दुनिया के सेकंड का प्रतिनिधित्व नहीं करता है; अक्सर यह डिजाइन की गति के आधार पर घड़ी चक्कर या नैनोसेकंड का प्रतिनिधित्व करता है। स्केलिंग में स्थिरता बहुत महत्वपूर्ण है। यदि आरेख के एक भाग में प्रति ग्रिड वर्ग 10 नैनोसेकंड दिखाए जाते हैं, तो दूसरे भाग में भी उसी स्केल को बनाए रखना चाहिए, जब तक कि विस्तार से देखने के लिए विशेष रूप से जूम नहीं किया गया है।

प्रणाली के प्रदर्शन के विश्लेषण के दौरान, समय अक्ष बॉटलनेक्स को पहचानने में मदद करता है। उदाहरण के लिए, यदि डेटा सिग्नल को स्थिर होने में 50 नैनोसेकंड की आवश्यकता होती है, लेकिन घड़ी का किनारा 40 नैनोसेकंड के बाद आता है, तो उल्लंघन होता है। अक्ष इंजीनियरों को इन अंतरालों को सीधे मापने की अनुमति देता है।

सिग्नल रेखाएं और तर्क स्तर 🔄

प्रत्येक सिग्नल रेखा एक भौतिक तार या एक तार्किक चर के संगत होती है। जटिल प्रणालियों में, बस को एक मोटी रेखा के रूप में दर्शाया जा सकता है जिसमें कई सिग्नल एक साथ समूहित होते हैं, या प्रत्येक बिट के लिए अलग-अलग रेखाएं। तर्क स्तर सिग्नल की अवस्था को परिभाषित करते हैं:

- एक्टिव हाई: जब वोल्टेज उच्च होता है, तो सिग्नल को “चालू” या “सत्य” माना जाता है।

- एक्टिव लो: जब वोल्टेज निम्न होता है, तो सिग्नल को “चालू” या “सत्य” माना जाता है। इसे आमतौर पर प्रतीक पर एक बबल या विशिष्ट नामकरण पद्धति द्वारा इंगित किया जाता है।

नियंत्रण सिग्नलों जैसे “चिप सेलेक्शन” या “लेखन सक्षम” के व्याख्या करने के लिए सक्रिय अवस्था को समझना महत्वपूर्ण है। एक एक्टिव-लो सिग्नल को एक्टिव-हाई के रूप में गलत व्याख्या करने से डिजाइन विफलताएं हो सकती हैं जिन्हें डिबग करना मुश्किल होता है।

संक्रमण और किनारे ⚡

जब कोई सिग्नल एक तर्क स्तर से दूसरे तर्क स्तर में बदलता है, तो संक्रमण होता है। भौतिक दुनिया में इन परिवर्तनों के तत्काल होने की संभावना बहुत कम होती है, लेकिन समय आरेख में इन्हें आदर्श परिवर्तन के क्षण का प्रतिनिधित्व करने के लिए अक्सर ऊर्ध्वाधर रेखाओं के रूप में बनाया जाता है।

- बढ़ता किनारा: निम्न से उच्च की ओर संक्रमण। यह अक्सर समकालिक तर्क के लिए ट्रिगर बिंदु होता है।

- गिरता किनारा: उच्च से निम्न की ओर संक्रमण। कुछ प्रणालियाँ इस किनारे का उपयोग डेटा कैप्चर के लिए करती हैं।

- किनारा-ट्रिगर्ड: तर्क जो संक्रमण के क्षण मात्र प्रतिक्रिया करता है।

- स्तर-ट्रिगर्ड: तर्क जो तब तक प्रतिक्रिया करता है जब तक सिग्नल एक विशिष्ट अवस्था में रहता है।

वास्तविक दुनिया के सिग्नलों में राइज और फॉल टाइम होते हैं। एक सही ऊर्ध्वाधर रेखा एक अमूर्तता है। उच्च गति डिजाइन में, संक्रमण की ढलान महत्वपूर्ण होती है क्योंकि यह विद्युत चुंबकीय हस्तक्षेप और सिग्नल अखंडता को प्रभावित करती है।

समय संबंधी पैरामीटर और सीमाएँ 📐

दृश्य रेखाओं से आगे, समय आरेख का महत्वपूर्ण मूल्य सिग्नलों के साथ परिभाषित मात्रात्मक पैरामीटर में निहित है। इन पैरामीटर्स उन भौतिक सीमाओं को निर्धारित करते हैं जिनके भीतर हार्डवेयर को संचालित करना होता है।

सेटअप और होल्ड समय ⚙️

ये अनुक्रमिक तर्क डिजाइन में दो सबसे सामान्य सीमाएँ हैं, विशेष रूप से जब डेटा किसी फ्लिप-फ्लॉप द्वारा क्लॉक किनारे पर कैप्चर किया जा रहा होता है।

- सेटअप समय: डेटा सिग्नल के स्थिर रहने के लिए न्यूनतम समयपहले सक्रिय क्लॉक किनारे के। यदि डेटा क्लॉक किनारे के बहुत निकट बदलता है, तो फ्लिप-फ्लॉप सही मान कैप्चर नहीं कर सकता है।

- होल्ड समय: डेटा सिग्नल के स्थिर रहने के लिए न्यूनतम समयके बाद सक्रिय क्लॉक किनारे के। यदि डेटा किनारे के बाद बहुत जल्दी बदलता है, तो कैप्चर क्षतिग्रस्त हो सकता है।

| पैरामीटर | परिभाषा | उल्लंघन का परिणाम |

|---|---|---|

| सेटअप समय | क्लॉक किनारे से पहले डेटा के स्थिर रहने का समय | अस्थिरता या गलत डेटा कैप्चर |

| होल्ड समय | क्लॉक किनारे के बाद डेटा के स्थिर रहने का समय | अस्थिरता या गलत डेटा कैप्चर |

| प्रसारण देरी | गेट के माध्यम से सिग्नल के यात्रा करने में लगा समय | समय के आराम में कमी, धीमी अधिकतम आवृत्ति |

| क्लॉक स्क्यू | क्लॉक सिग्नल के आगमन समय में अंतर | प्रभावी समय सीमा का कम होना |

प्रसारण देरी ⏱️

प्रसारण देरी इनपुट में परिवर्तन के आउटपुट को प्रभावित करने में लगने वाला समय है। समय आरेख में, यह क्लॉक के किनारे और परिणामी डेटा परिवर्तन के बीच के अंतर के रूप में दिखाई देता है। यह देरी भौतिक सीमाओं के कारण होती है, जैसे तारों में धारिता और ट्रांजिस्टर की स्विचिंग गति।

एक प्रणाली के डिजाइन करते समय, एक मार्ग के अनुदिश प्रसारण देरियों का योग क्लॉक अवधि माइनस सेटअप समय से कम होना चाहिए। यदि देरी बहुत अधिक है, तो प्रणाली अभीष्ट क्लॉक गति पर नहीं चल सकती है।

क्लॉक स्क्यू और जिटर 📉

क्लॉक स्क्यू सर्किट के विभिन्न भागों पर क्लॉक सिग्नल के आगमन समय में अंतर को संदर्भित करता है। एक आदर्श आरेख में, क्लॉक लाइन लंबवत होती है और सभी घटकों के लिए समकालीन होती है। वास्तविकता में, रूटिंग के अंतर के कारण स्क्यू होता है। सकारात्मक स्क्यू का अर्थ है कि क्लॉक गंतव्य पर बाद में पहुंचता है, जो सेटअप समय के लिए मदद कर सकता है लेकिन होल्ड समय को नुकसान पहुंचाता है।

जिटर सिग्नल के किनारों के समय में भिन्नता है। यह शोर है जो किनारे को अपेक्षित समय से पहले या बाद में आने के लिए बाध्य करता है। उच्च जिटर प्रभावी समय सीमा को कम करता है, जिसके कारण स्थिरता बनाए रखने के लिए प्रणाली को धीमी गति से चलाने की आवश्यकता होती है।

सिग्नल और बस के प्रकार 📡

विभिन्न प्रणालियाँ विभिन्न संकेतन विधियों का उपयोग करती हैं। सटीक होने के लिए, समय आरेख में इन अंतरों को दर्शाना आवश्यक है।

डिजिटल सिग्नल

अधिकांश समय आरेख डिजिटल तर्क पर केंद्रित होते हैं। इन सिग्नलों के द्विआधारी होना चाहिए, 0 और 1 के बीच स्विच करते हैं। आरेख की स्पष्टता तर्क सीमाओं को स्पष्ट रूप से चिह्नित करने पर निर्भर करती है। कुछ सिग्नलों में मध्यवर्ती अवस्थाएँ या “देखभाल नहीं” की स्थिति हो सकती है, जिन्हें आमतौर पर X के साथ चिह्नित किया जाता है।

एनालॉग सिग्नल

शुद्ध डिजिटल समय आरेखों में कम आम होने के बावजूद, वोल्टेज रेल या सेंसर आउटपुट जैसे एनालॉग सिग्नल को कभी-कभी शामिल किया जाता है। इन्हें तीखे चरणों के बजाय ढलान वाली या वक्र रेखाओं के रूप में दर्शाया जाता है, जो लगातार परिवर्तन को दर्शाता है, बजाय अलग-अलग अवस्था परिवर्तन के।

बसें और समानांतर डेटा

जब कई बिट एक साथ यात्रा करते हैं, तो उन्हें आमतौर पर समूहित किया जाता है। एक बस समय आरेख सभी बिट्स की स्थिति एक साथ दिखाता है। बस की चौड़ाई (जैसे 8-बिट, 32-बिट) को लेबल करना और वैध डेटा विंडो दिखाना आवश्यक है जहां सभी बिट एक साथ स्थिर होते हैं।

समय आरेख पढ़ना: एक चरण-दर-चरण मार्गदर्शिका 🔍

इन आरेखों की व्याख्या करने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है ताकि महत्वपूर्ण विवरण छूट न जाएं।

- क्लॉक की पहचान करें: मुख्य समय संदर्भ को खोजें। सभी अन्य घटनाओं को इस रेखा के संबंध में मापा जाना चाहिए।

- किनारे संवेदनशीलता निर्धारित करें: जांचें कि क्या प्रणाली क्लॉक के उत्थान या गिरावट वाले किनारे पर ट्रिगर होती है।

- डेटा वैधता का अनुसरण करें: उस अवधि को खोजें जहां डेटा लाइनें स्थिर हों। यही “वैध विंडो” है।

- नियंत्रण सिग्नल की जांच करें: ऐसी लाइनों की पहचान करें जो डेटा स्थानांतरण को नियंत्रित करती हैं, जैसे एनेबल, रीसेट या चिप सेलेक्ट।

- अंतराल मापें: समय अक्ष का उपयोग देरी, सेटअप समय और पल्स चौड़ाई को मापने के लिए उपयोग करें।

आम समय संबंधी उल्लंघन और त्रुटियाँ ⚠️

सावधानी से योजना बनाने के बावजूद, समय संबंधी उल्लंघन होते हैं। एक आरेख में लक्षणों को पहचानना उन्हें ठीक करने का पहला चरण है।

- सेटअप उल्लंघन: डेटा अगले क्लॉक एज के लिए बहुत देर से आता है। समाधान में अक्सर क्लॉक को धीमा करना या लॉजिक पथ को अनुकूलित करना शामिल होता है ताकि देरी कम की जा सके।

- होल्ड उल्लंघन: डेटा क्लॉक एज के बाद बहुत जल्दी बदल जाता है। इसे ठीक करना अक्सर कठिन होता है क्योंकि डेटा पथ या क्लॉक पथ में देरी जोड़ने की आवश्यकता हो सकती है।

- मेटास्टेबिलिटी: एक ऐसी स्थिति जहाँ फ्लिप-फ्लॉप आउटपुट अनिश्चित अवधि के लिए न तो 0 होता है और न ही 1। यह आमतौर पर तब होता है जब सेटअप या होल्ड समय का उल्लंघन होता है।

- ग्लिचेस: संयोजक तर्क में रेस कंडीशन के कारण होने वाले छोटे, अनचाहे पल्स। यदि फ़िल्टर नहीं किए गए, तो ये गलत स्थिति परिवर्तन को ट्रिगर कर सकते हैं।

असिंक्रोनस बनाम सिंक्रोनस डिज़ाइन 🔄

समय आरेख डिज़ाइन विधि के आधार पर अलग-अलग दिखाई देते हैं।

सिंक्रोनस डिज़ाइन

घटनाओं को एक सामान्य क्लॉक द्वारा नियंत्रित किया जाता है। समय आरेख में स्पष्ट, आवर्ती क्लॉक लाइनें दिखाई जाती हैं। डेटा केवल क्लॉक एज पर ही बदलता है। इस दृष्टिकोण में विश्लेषण सरल हो जाता है क्योंकि समय का खंड निश्चित होता है।

असिंक्रोनस डिज़ाइन

घटनाओं को हैंडशेक सिग्नल (जैसे रिक्वेस्ट और एकॉनोलेज) द्वारा नियंत्रित किया जाता है। समय आरेख में घटनाओं के बीच अनियमित अंतर दिखाई देते हैं। यद्यपि अधिक लचीला है, लेकिन इन आरेखों का विश्लेषण करना कठिन होता है क्योंकि कोई निश्चित समय संदर्भ नहीं होता है।

प्रोटोकॉल में अनुप्रयोग 📡

संचार प्रोटोकॉल बहुत अधिक सटीक समय पर निर्भर करते हैं। आरेख को समझना इन मानकों को लागू करने के लिए महत्वपूर्ण है।

सीरियल संचार

सीरियल इंटरफेस डेटा एक बिट समय में भेजते हैं। समय आरेख बिट अवधि दिखाता है। क्लॉक और डेटा लाइन के बीच संबंध (उदाहरण के लिए, डेटा राइजिंग एज पर वैध) प्रोटोकॉल नियमों को परिभाषित करता है।

पैरेलल संचार

पैरेलल इंटरफेस एक साथ कई बिट्स भेजते हैं। समय आरेख में पूरे बस के लिए सेटअप समय दिखाना आवश्यक है। सभी बिट्स को लैच एज आने से पहले स्थिर होना चाहिए।

दस्तावेज़ीकरण के लिए सर्वोत्तम प्रथाएं 📝

स्पष्ट दस्तावेज़ीकरण बनाने से यह सुनिश्चित होता है कि अन्य � ingineers प्रणाली को अस्पष्टता के बिना समझ सकें।

- संगत लेबल का उपयोग करें: सिग्नल के नाम बिल्कुल उन्हीं तरीके से रखें जैसे वे कोड या स्कीमेटिक में दिखाई देते हैं।

- इकाइयाँ शामिल करें: हमेशा अक्ष पर समय इकाइयाँ (ns, µs, चक्कर) निर्दिष्ट करें।

- महत्वपूर्ण पथों को उजागर करें: सबसे समय-संवेदनशील सिग्नलों को इंगित करने के लिए मोटी रेखाएं या रंगों का उपयोग करें।

- उल्लंघनों को टिप्पणी करें: यदि कोई उल्लंघन ज्ञात है, तो इसे छिपाने के बजाय स्पष्ट रूप से चिह्नित करें।

- इसे ताजा रखें: डिज़ाइन में परिवर्तन होने पर आरेखों को अद्यतन करें। अद्यतन नहीं आरेख बग्स का मुख्य स्रोत हैं।

उन्नत Pertimbangan: बहु-घड़ी क्षेत्र 🌐

आधुनिक प्रणालियाँ अक्सर विभिन्न गतियों पर चलने वाले कई घड़ी क्षेत्रों के साथ संचालित होती हैं। इन प्रणालियों के लिए समय आरेख में घड़ियों के बीच संबंध स्पष्ट रूप से दिखाना आवश्यक है।

- घड़ी के बीच संक्रमण: तेज़ क्षेत्र से धीमे क्षेत्र में जाने वाले डेटा के लिए डेटा हानि से बचने के लिए सावधानीपूर्वक समन्वय आवश्यक है।

- फेज संबंध: यदि दो घड़ियाँ एक स्रोत साझा करती हैं लेकिन अलग-अलग चरणों में हैं, तो आरेख में चरण विस्थापन दिखाना आवश्यक है।

- हैंडशेक तर्क: क्षेत्रों के बीच असमान ब्रिज एक हैंडशेक सिग्नल पर निर्भर करते हैं। समय आरेख में पूर्ण अनुरोध-स्वीकृति चक्र को दिखाना आवश्यक है।

सिमुलेशन की भूमिका समय विश्लेषण में 💻

हार्डवेयर बनाए जाने से पहले, सिमुलेशन समय आरेखों की पुष्टि करते हैं। इंजीनियर तरंगरूप दृश्यकर्ता का उपयोग अपेक्षित व्यवहार की तुलना सिमुलेशन परिणामों के साथ करते हैं।

- स्थैतिक समय विश्लेषण: वास्तविक तरंगरूप के सिमुलेशन के बिना सबसे खराब मामले के देरी की गणना करता है।

- गतिशील समय सिमुलेशन: वास्तविक तरंगरूप उत्पन्न करने के लिए सर्किट की एक आभासी संस्करण चलाता है।

- लेआउट के बाद सिमुलेशन: चिप डिज़ाइन के बाद भौतिक तार की लंबाई और धारिता को ध्यान में रखता है।

इन उपकरणों के द्वारा इंजीनियर भौतिक वास्तविकता के खिलाफ समय आरेख की पुष्टि कर सकते हैं। यदि सिमुलेशन में सेटअप उल्लंघन दिखाता है, तो निर्माण से पहले डिज़ाइन को संशोधित करना होगा।

समय सटीकता पर निष्कर्ष ✅

समय आरेखों के निर्माण और व्याख्या को समझना तकनीकी पेशेवरों के लिए एक मूलभूत कौशल है। ये आरेख अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं। वे यह सुनिश्चित करते हैं कि सिग्नल जब आवश्यक हो, उचित अवस्था में और पर्याप्त स्थिरता के साथ आएं ताकि प्रणाली कार्य कर सके। इस गाइड में बताए गए तत्वों और सीमाओं का पालन करके टीमें त्रुटियों को कम कर सकती हैं और प्रणाली की विश्वसनीयता में सुधार कर सकती हैं। इन दृश्य प्रस्तुतियों में विवरण का ध्यान रखने से अंतिम उत्पाद की स्थिरता और प्रदर्शन में लाभ मिलता है।

चाहे उच्च गति वाले मेमोरी इंटरफेस, कम शक्ति वाले माइक्रोकंट्रोलर या जटिल डेटा बस पर काम कर रहे हों, सिद्धांत एक जैसे रहते हैं। समय स्थिरांक है, और सिग्नल चर हैं। उनके संबंध को समझना सफल इंजीनियरिंग की कुंजी है।