現代のデジタル設計において、時間の経過に伴う信号の流れを理解することは、システムの信頼性を確保するために不可欠である。非同期システムは、操作が単一のグローバルクロックによって制御されないものであり、同期システムと比較して特有の課題を呈する。これらの複雑な相互作用を可視化しデバッグするために用いられる主なツールがタイミング図である。このガイドでは、非同期環境内でタイミング図をどのように構築し、読み、分析するかについて詳しく解説する。

非同期設計の本質 🌐

非同期システムは、すべての状態変化を駆動する中央集権的なクロック信号を持たずに動作する。代わりに、イベントは前の操作の完了またはデータの到着によって引き起こされる。このアプローチは、特定の文脈において消費電力を低減し、より高い潜在的な性能を実現するという利点を持つ。しかし、信号の同期やタイミングの検証に関する複雑さをもたらす。

エンジニアがこれらのシステムを分析する際には、変動する遅延、伝播時間、および普遍的な基準点の欠如を考慮しなければならない。タイミング図は、これらのイベントをマッピングするための視覚的言語として機能する。これにより、チームは信号の遷移が時間の経過とともにどのように関係しているかを正確に把握できる。

タイミング図の構造 📐

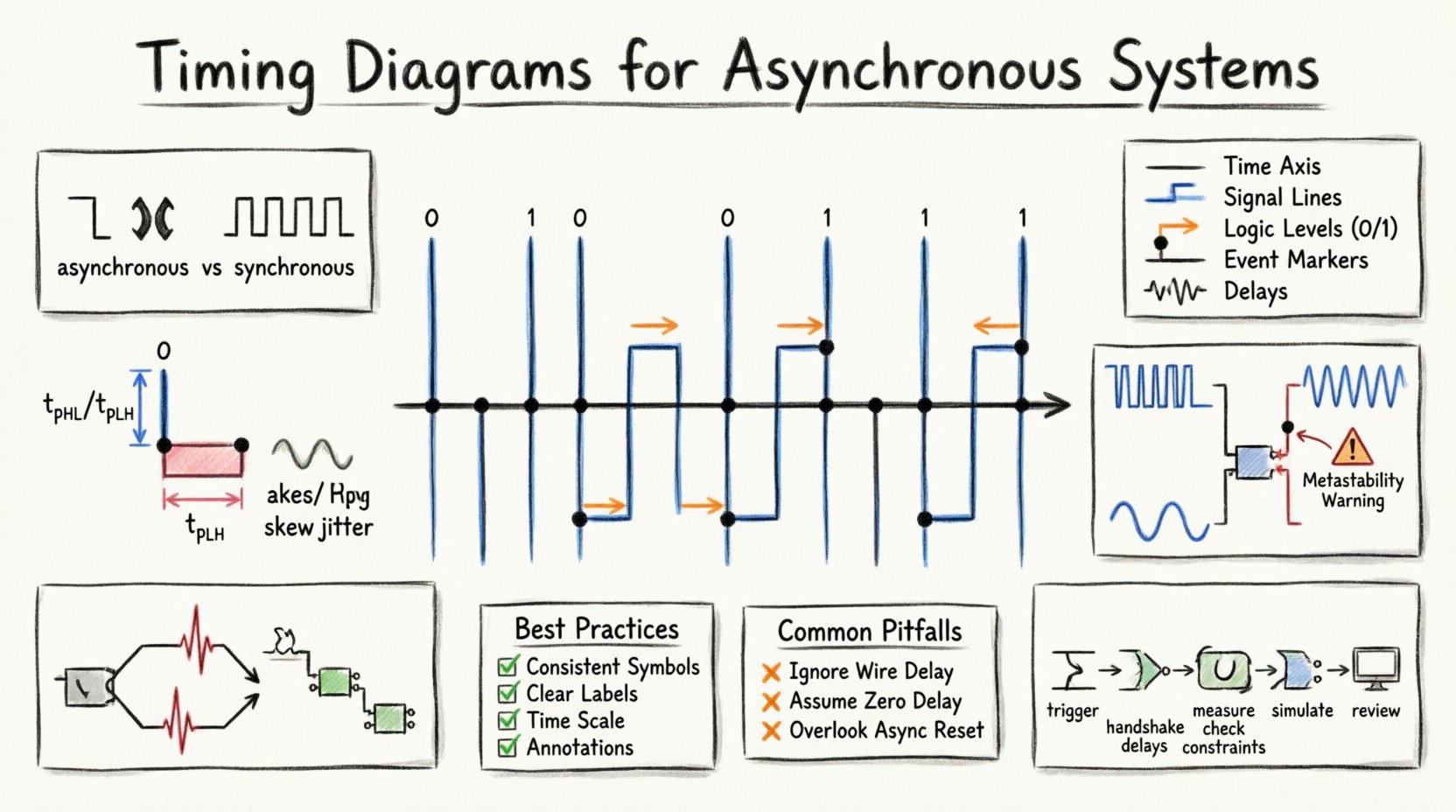

タイミング図は、信号の挙動をグラフィカルに表現したものです。横軸に時間を、縦軸に信号の状態をプロットする。非同期システムを効果的に分析するためには、これらの図を構成する基本的な要素を理解する必要がある。

- 時間軸: 時間の進行を表す。非同期解析では、クロックサイクルではなく、特定のイベントのトリガーを基準として相対的に扱われることが多い。

- 信号線: 個々のワイヤーやネットを表す水平線。各線は特定の信号の論理レベル(High、Low、またはUnknown)を追跡する。

- 論理レベル: 通常は「

0」(Low/Ground)および「1」(High/VCC)として表される。これらの状態間の遷移が分析の核心となる。 - イベントマーカー: 特定の出来事(たとえば、ハンドシェイク信号の状態変化など)を示す垂直線または注記。

- 遅延: 入力の変化とそれに応じた出力の変化の間の視覚的なギャップであり、伝播遅延を表す。

同期図がクロックエッジを表すグリッド線に依存するのに対し、非同期図はイベント境界に依存する。そのため、遷移間の間隔の解釈がより慎重でなければならない。

重要なタイミングパラメータ ⚙️

非同期システムの整合性を分析するためには、特定のタイミングパラメータを測定し、設計仕様と比較する必要がある。これらのパラメータは、受信側が信号を正しく解釈できるために信号が安定している必要がある時間窓を定義する。

伝播遅延

伝播遅延とは、信号がコンポーネントの入力から出力まで到達するまでの時間を指す。非同期論理では、この遅延が不確実性の主要な原因となる。製造のばらつき、温度、電圧の変化がこの遅延を変化させる可能性がある。

- tpHL:信号がHighからLowに遷移するまでの時間。

- tpLH:信号がLowからHighに遷移するまでの時間。

- tpd:一般的な伝播遅延で、通常はtpHLとtpLHの平均値として計算される。

タイミング図を分析する際は、入力エッジとそれに対応する出力エッジとの間の水平距離を確認する。この距離が伝播遅延である。

セットアップ時間とホールド時間

非同期システムにおいても、フリップフロップやラッチはしばしば特定の安定期間を必要とする。セットアップ時間とは、トリガイベントの前にデータが安定している必要がある期間を指す。ホールド時間とは、トリガイベントの後にデータが安定したまま維持されなければならない期間を指す。

これらの期間が違反されると、システムはメタスタビリティ状態に陥る可能性があり、出力はHighでもLowでもなく、定義されない電圧レベルとなる。タイミング図は、データが制御エッジに近すぎるように変化しているかどうかを示すことで、これらの違反を可視化する。

スキューとジッター

- S スキュー:同じ信号が回路内の2つの異なる点に到着する時間の差。

- ジッター:信号タイミングの短期的な変動。非同期システムでは、電源ノイズやクロストークによってジッターが発生することがある。

クロックドメイン間の遷移処理 🔄

混合モードシステムにおける誤りの最も一般的な原因の一つは、異なるクロックドメイン間を渡る際の処理である。システムが主に非同期であっても、異なる周波数で動作する同期サブブロックを含むことがよくある。タイミング図は、これらの遷移を検証するために不可欠である。

信号が1つのクロックドメインから別のクロックドメインに移動する際、受信側が信号が変化しているタイミングでサンプリングする可能性がある。これによりメタスタビリティが発生する。これを緩和する標準的なアプローチは、同期器(通常はフリップフロップの連鎖)を使用することである。

| パラメータ | 説明 | タイミング図への影響 |

|---|---|---|

| メタスタビリティ解消時間 | 同期器が有効な論理レベルに解消するのに必要な時間 | 信号が安定する前に、定義されない状態が長期間続くことを示す |

| ドメイン間レイテンシ | 同期器によって追加される遅延 | ソースイベントと宛先イベントの間の時間ギャップを増加させる |

| ハンドシェイクレイテンシ | 非同期プロトコルにおける確認信号にかかる時間 | 信号タイムラインに前後往復のパターンを生じさせる |

アナリストは、タイミング図が解消時間の影響を考慮していることを確認しなければならない。同期器が解消する前に下流ブロックが信号を読み取ろうとすると、データ破損が発生する。

ラス条件の特定と解決 ⚠️

システムの動作が、互いに影響を与えてはならないイベントの相対的なタイミングに依存する場合、ラス条件が発生する。非同期論理では、これが頻繁な懸念事項である。タイミング図は、これらの状態を検出する主な手法である。

スタティックハザード

静的ハザードは、信号が一定レベルを維持すべきなのに、パス遅延により一時的に反転するときに発生する。たとえば、論理的にHighのまま維持すべき信号が、入力の変化により一時的にLowに低下する場合、これは静的1ハザードである。

- 視覚的指標:平坦であるべき信号線に、細長いスパイクまたはパルスがある。

- 根本原因:異なる論理ゲートを通過する際の伝播遅延の不均衡。

動的ハザード

動的ハザードは、1つの遷移が期待されるのに複数の遷移が発生する状態を指す。これは、信号が異なる数のゲートを通過する複雑な論理パスで頻繁に発生する。

ラ race条件の分析手順

- パスを追跡する:信号がソースから宛先までたどるすべてのパスを特定する。

- 遅延を測定する:タイミング図を用いて、各パスの遅延を計算する。

- エッジを比較する:競合する信号の到着時刻が、曖昧さを生じるような形で重複していないか確認する。

- 安定性を検証する:データ到着の重要な期間中に、制御信号が安定したまま保たれていることを確認する。

ラ race条件が発見された場合、設計の再構築が必要になることがある。一般的な解決策には、遅延を均等化するためにバッファを追加する、ハンドシェイクプロトコルを挿入する、または非同期FIFO構造を使用するものがある。

信号整合性とノイズに関する考慮事項 🔌

タイミング図は真空状態に存在するわけではない。物理層は信号品質に影響を与えるノイズを導入する。非同期システムを分析する際には、論理的なタイミングエラーと物理的な信号劣化を区別する必要がある。

信号のギャップ(グリッチ)

グリッチは、回路を伝播する可能性のある短時間のパルスである。非同期システムでは、グリッチがラッチやフリップフロップを誤ってトリガーする可能性がある。タイミング図では、これらが細長いスパイクとして表示されることが多い。

- フィルタリング:下流の論理回路が、これらのパルスをフィルタリングできるだけの遅延を持っていることを確認する。

- エッジレート:急峻なエッジ(速い立ち上がり/立ち下がり時間)は、ノイズのカップリングに対してより敏感である。

クロストーク

クロストークは、1本のワイヤ上の信号が隣接するワイヤに電圧を誘導するときに発生する。これにより信号のタイミングがずれ、予想より早くまたは遅く到着する可能性がある。

タイミング図では、クロストークがエッジ位置のずれや追加のノイズスパイクとして現れることがある。これを緩和するためには、物理設計段階で信号間の間隔を検討する必要がある。

ドキュメント作成のベストプラクティス 📝

明確なドキュメントは、タイミング解析が他のエンジニアによって再現可能かつ理解可能であることを保証する。良好に構成されたタイミング図には、特定のメタデータと注釈が含まれる。

標準化

- 論理レベルには一貫した記号を使用する。

- すべての信号に、その機能を明確にラベル付けする。

- 時間スケールを明示的に示す(例:1目盛りあたりナノ秒)。

注記

テキスト注記は特定の動作を説明するために不可欠である。重要な遷移や潜在的な問題領域を示すために矢印を使用する。伝播遅延の値を図上に直接ラベルする。

バージョン管理

タイミング図は設計の変更に伴って進化する。分析が現在のハードウェア状態と一致することを保証するために、すべての図にバージョン番号を維持する。タイミングの詳細については記憶に頼らない。

ステップバイステップの解析プロセス 🛠️

非同期システムを効果的に解析するためには、構造的なアプローチに従う。これにより、重要なタイミングパラメータが見逃されることがない。

- トリガを定義する:シーケンスを開始するイベントを特定する。これは通常、時間軸の出発点となる。

- ハンドシェイクをマッピングする:リクエスト信号とアックノリッジ信号を追跡する。正しいプロトコル(例:4相または2相ハンドシェイク)に従っていることを確認する。

- 遅延を測定する:トリガから最終出力までの総遅延を計算する。これをコンポーネントごとの遅延に分解する。

- 制約を確認する:関与するすべての記憶素子について、セットアップ時間およびホールド時間の要件を満たしていることを確認する。

- 変動をシミュレートする:最大温度や最小電圧などの最悪条件のもとで図を分析する。

- メタスタビリティを確認する:同期回路を用いて、メタスタビリティの発生確率を許容可能なレベルまで低下させることを確認する。

タイミング解析における一般的な落とし穴 ⚡

経験豊富なエンジニアでも、微細な問題を見逃すことがある。一般的な落とし穴に注意することで、高コストな再設計を回避できる。

- 配線遅延を無視する:インターコネクトの抵抗および静電容量を無視して、ゲート遅延のみに依存する。

- ゼロ遅延を仮定する:フィードバックループを即時であると扱うが、これは物理的に不可能である。

- 非同期リセットを無視する:データ信号に対するリセット信号のタイミングを考慮しないこと。

- エッジとレベルの混同:図の解釈において、エッジトリガー型とレベルトリガー型の挙動を混同すること。

検証に関する結論 ✅

タイミング図は非同期システムの検証において不可欠である。それらは抽象的なタイミング関係を具体的な視覚的表現として提供する。これらの図を厳密に分析することで、エンジニアはラ race 条件を特定し、ハンドシェイクプロトコルを検証し、信号整合性を確保できる。

非同期設計の複雑さは正確さを要求する。1ナノ秒単位で差が生じる。伝播遅延、セットアップ時間、ホールド時間についての徹底的な理解があれば、堅牢なシステムの構築が可能になる。グローバルクロックの欠如が困難をもたらす一方で、詳細なタイミング解析から得られる知見は、より効率的で信頼性の高い設計につながる。

これらの分析スキルを継続的に磨き続けることで、システムが変化する環境条件下でも正しく動作することが保証される。目標は、きめ細かな文書化と測定によって達成される安定性と予測可能性である。

高度な考慮事項 🔬

高性能なアプリケーションでは、追加の要因が関与する。それらには、チップ上の温度勾配やスイッチングイベント中の電圧低下が含まれる。

- 温度勾配:チップの高温な中心部から低温な端部へと伝わる信号は、異なる速度を経験する。この変化はタイミング解析に反映されなければならない。

- 電源グリッドノイズ:同時スイッチングノイズは論理閾値をずらす可能性がある。タイミング図は理想的には電源レールの安定性を表現すべきである。

- 可変レイテンシ:一部の非同期プロトコルでは可変レイテンシを許容する。タイミング図は単一の値ではなく、許容可能なレイテンシの範囲を示さなければならない。

これらの高度な考慮事項を組み込むことで、タイミング解析はシステム検証の包括的なツールとなる。単なる検証を超えて、本質的なパフォーマンス最適化へと進化する。

タイミングはスピードだけの話ではない。正しさが重要である。タイミングエラーにより失敗する高速なシステムは、信頼性を持って動作する遅いシステムよりも有用性が低い。タイミング図は、その信頼性へと導く地図である。