組み込み工学の複雑な世界において、タイミングはすべてです。マイコンはシミュレーションでは完璧に動作するかもしれませんが、数ナノ秒の遅延によってハードウェア上で悲惨な失敗を起こすことがあります。これがタイミング図が不可欠なツールとなる場面です。これらの視覚的表現は、信号の時間的挙動をマッピングし、デジタルシステム内のコンポーネントの相互作用の明確なスナップショットを提供します。通信障害のデバッグを行っている場合でも、新しい周辺インターフェースを設計している場合でも、タイミング図の読み方と作成方法を理解することは、基礎中の基礎です。

このガイドでは、基本的な定義から複雑なプロトコル相互作用まで、信号タイミングの基本的なメカニズムをカバーします。波形の解釈方法、測定データから正確な図を構築する方法、システムの不安定化を引き起こす一般的な落とし穴の特定について探求します。これらの視覚的ツールを習得することで、システムの挙動を予測し、ベンチから出る前にも設計を検証できる能力が得られます。

🔍 信号タイミングの基本を理解する

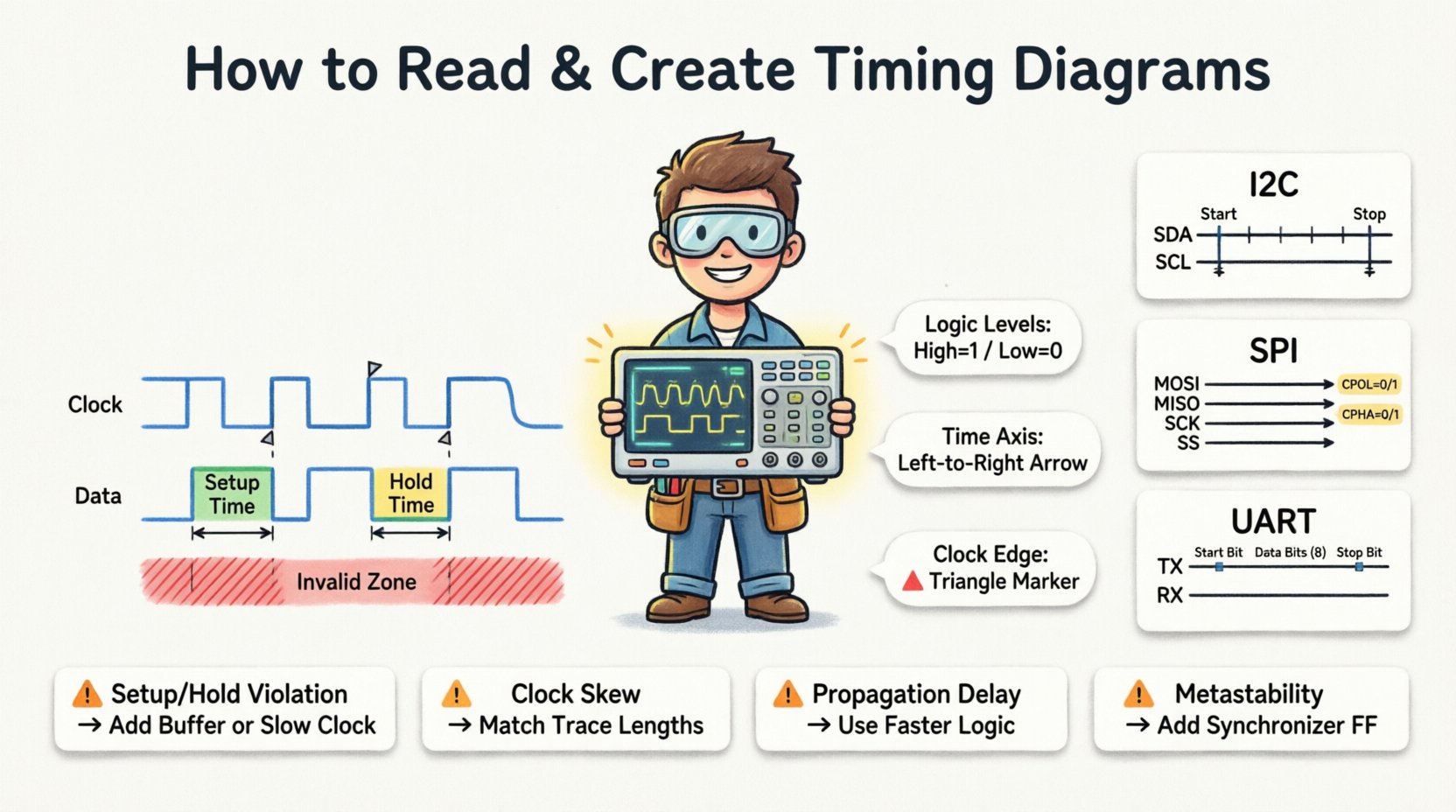

タイミング図は単なる図面ではなく、時間軸に対する論理状態の数学的表現です。組み込みシステムでは主にデジタル論理レベルを取り扱い、これらは2値です:High(1)とLow(0)。しかし、これらのレベル間の遷移が複雑さの本質です。

- 論理レベル:ほとんどの組み込みシステムは特定の電圧閾値で動作します。たとえば、3.3Vシステムでは、2.0V以上の電圧をHigh、0.8V以下の電圧をLowと定義します。

- 時間軸:時間は左から右へ流れます。水平方向の間隔は、特定の状態の持続時間またはイベント間の遅延を表します。

- 信号トレース:各水平線は特定のワイヤーやネットを表します。複数の線を垂直に積み重ねることで、信号間の関係を比較できます。

システムを分析する際には、因果関係を探しています。クロック信号がデータの変化をトリガーするか?データが有効になる前に、有効信号がアクティブである必要があるか?タイミング図はこれらの問いに視覚的に答えます。

🛠️ タイミング図の主要な構成要素

図を正しく解釈するためには、信号の挙動を示すために用いられる標準的な要素を認識する必要があります。これらの構成要素がハードウェアとのやり取りのルールを定義します。

| 構成要素 | 説明 | 視覚的インジケータ |

|---|---|---|

| 信号名 | 特定のワイヤーやネットを識別する | 左側のテキストラベル |

| 論理レベル | High(1)またはLow(0)の状態 | 上部または下部の水平なフラットライン |

| 遷移エッジ | HighからLowへの変化、またはその逆 | レベルをつなぐ垂直線 |

| クロックエッジ | 同期論理のトリガー点 | 破線または三角形マーカー |

| 無効領域 | データが読み取れない領域 | 陰影付きまたは斜線入りの領域 |

これらの要素を理解することで、複雑な相互作用を分解できるようになります。たとえば、陰影付きの領域は、受信デバイスがデータを信頼してキャプチャできない設定時間またはホールド時間の要件を示すことがよくあります。

👁️ 時系列図の読み方:ステップバイステップ

時系列図を読むには体系的なアプローチが必要です。本質的には、視覚的なパターンをイベントの順序に変換しているのです。正確さを確保するために、このプロセスに従ってください。

1. クロック信号源の特定

ほとんどの組み込みシステムは同期的であり、クロック信号が動作のペースを決定します。クロックトレースを特定してください。通常、規則的で周期的な方形波を示します。

- 周波数を確認してください。1 MHz か 100 MHz ですか?これにより、システム全体の速度が決まります。

- エッジタイプを特定してください。デバイスは立ち上がりエッジ(Low から High)でトリガするか、立ち下がりエッジ(High から Low)でトリガするか?

2. データ有効期間のマッピング

データはクロックに対して特定の期間内でのみ有効です。クロックエッジとデータラインの関係を確認してください。

- セットアップ時間: データは一定期間、安定している必要がある クロックエッジの後

- ホールド時間: データは一定期間、安定したまま維持されなければならない クロックエッジの後

これらの期間中にデータが変化すると、タイミング違反が発生し、メタスタビリティまたは誤ったデータキャプチャを引き起こします。

3. コントロール信号の分析

チップセレクト(CS)、イネーブル(EN)、リセット(RST)などのコントロール信号は、通信が行われるタイミングを決定します。

- チップセレクトはアクティブローかアクティブハイか?

- イネーブル信号はクロックのトグル開始前にアサートされる必要があるか?

- クロック論理を上回る非同期イベントは存在するか?

4. ハンドシェイキング機構の検証

多くのプロトコルはフロー制御を管理するためにハンドシェイキングを使用します。アスクノリッジ(ACK)またはリディ(RDY)信号を探してください。

- 送信側は次のバイトを送信する前に信号を待っているか?

- 図にタイムアウト条件が表現されているか?

📐 準確な時系列図の作成方法

タイミング図を作成することは、それを読むことと同等に重要です。ハードウェアエンジニアの仕様書として、ソフトウェア開発者の検証ガイドとして機能します。これらの図は要件、測定ツール、またはシミュレーションデータから生成できます。

ステップ1:プロトコル要件を定義する

描画する前に仕様を収集してください。これらの仕様は、接続しているコンポーネントのデータシートから通常得られます。

- 最小および最大のクロック周波数を抽出します。

- 論理HighおよびLowの電圧レベルをメモしてください。

- セットアップ時間およびホールド時間の制約を記録します。

ステップ2:信号データをキャプチャする

ハードウェアツールを使用して現実世界の動作をキャプチャします。これにより、図が理論的な理想ではなく、現実を反映していることを保証します。

- オシロスコープ:アナログ信号の整合性および電圧レベルに最適です。

- ロジックアナライザ:デジタル状態遷移およびマルチチャネルタイミングに最適です。

- シミュレーションモデル:ハードウェアが入手可能になる前に対応する論理を検証するのに適しています。

ステップ3:波形をプロットする

信号を時系列に描画してください。すべてのチャネルで時間スケールが一貫していることを確認してください。

- 論理レベルには直線を使用してください。

- 立ち上がり時間および立ち下がり時間を示すために、遷移には斜線を使用してください。

- クロックエッジやデータ変化などの重要なポイントにラベルを付けてください。

ステップ4:重要な制約を注釈する

注釈は、視覚情報だけでは伝えきれない文脈を提供します。

- セットアップ時間およびホールド時間のウィンドウを明確にマークしてください。

- 特定のプロトコル状態(例:スタートビット、ストップビット)の持続時間を示してください。

- 信号経路上の既知のレイテンシーや遅延を強調してください。

🌐 一般的な組み込みプロトコルにおけるタイミング図

異なる通信プロトコルにはそれぞれ特徴的なタイミング特性があります。これらのニュアンスを理解することは、統合において不可欠です。

1. インターフェース・インテグレーテッド回路(I2C)

I2Cは2線式の同期シリアルバスです。SDA(データ)とSCL(クロック)を使用します。

- スタート条件: SCLがHighの間に、SDAがHighからLowに遷移する。

- ストップ条件: SCLがHighの間にSDAがLowからHighに遷移する。

- データ転送: SCLがHighの間にデータは有効である;変更はSCLがLowの間に発生する。

- ACK/NACK: 受信側は9番目のクロックパルス中にSDAをLowに引き下げる事で受信を確認する。

2. シリアル周辺インターフェース(SPI)

SPIは、I2Cよりも高速な4線式同期バスである。

- ライン: MOSI(マスター出力)、MISO(マスター入力)、SCK(クロック)、SS(スレーブ選択)。

- CPOL: クロック極性はアイドル状態(HighまたはLow)を決定する。

- CPHA: クロックフェーズはデータがサンプリングされるタイミング(最初のエッジまたは2番目のエッジ)を決定する。

- チップ選択: クロックのトグルが開始される前にアサート(アクティブ)されなければならない。

3. ユニバーサル非同期受信送信機(UART)

UARTは非同期であり、共有クロック信号がないことを意味する。タイミングはバウドレートに依存する。

- スタートビット: フレームの開始を示すためにラインをLowに引き下げる。

- データビット: 最低位(LSB)から送信され、通常8ビットである。

- ストップビット: フレームの終了を示すためにラインをHighに引き上げる。

- パリティ: エラー検出のためのオプションビット。

| 特徴 | I2C | SPI | UART |

|---|---|---|---|

| クロック | 同期(共有) | 同期(共有) | 非同期(クロックなし) |

| 配線 | 2本(SDA、SCL) | 4本以上(MOSI、MISO、SCK、SS) | 2本(TX、RX) |

| アドレス指定 | はい(バイトアドレス) | いいえ(配線方式) | いいえ |

| 最大速度 | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ 一般的なタイミング違反とデバッグ

慎重な設計をしても、タイミング違反が発生する場合があります。これらは再現が難しい間欠的なバグの原因となることがよくあります。

1. ライズ時間とホールド時間の違反

データがクロックエッジに対して早すぎたり遅すぎたりするときに発生します。

- 症状:データ破損、またはロジックアナライザのキャプチャにおけるランダムなエラー。

- 修正:クロック速度を遅くする、またはPCBのトレース長を最適化する。

2. クロックスケュー

クロック信号が異なる部品に異なるタイミングで到達するときに発生します。

- 症状:1つのフリップフロップが他の部品が準備できていない間にデータをキャプチャするレースコンディション。

- 修正:トレース長を一致させる、または専用のクロック配布ネットワークを使用する。

3. 伝播遅延

信号は配線やゲートを通過するのに時間がかかります。長いトレースは顕著な遅延を引き起こします。

- 症状:高速ラインにおける信号整合性の問題や反射。

- 対策:終端抵抗を使用し、トレースを可能な限り短くする。

4. メタスタビリティ

非同期信号がクロックドメインを跨ぐ場合、受信側のフリップフロップがメタスタビリティ状態に入ることがある。

- 症状:システムがフリーズする、またはランダムにリセットされる。

- 対策:シナライザーチェーン(直列に2つ以上のフリップフロップ)を使用して信号を解決する。

📝 ドキュメント作成のベストプラクティス

ドキュメント用にタイミング図を作成することで、将来の開発者がハードウェアを逆引き解析せずにシステムを理解できることが保証される。

- 一貫性:プロジェクト内のすべての図において、標準的な記号と線形スタイルを使用する。

- スケール:時間軸が線形であり、明確に単位(ns、µs、ms)でラベル付けされていることを確認する。

- 参照: 図を特定のデータシートのセクションまたはプロトコル規格に常にリンクする。

- 明確さ:ごちゃごちゃしないようにする。信号が静的であれば、変動するノイズではなく、フラットな線で表示する。

- バージョン管理:ハードウェアまたはファームウェアに顕著な変更があるたびに、図を更新する。

🔗 信号整合性に関する最終的な考察

タイミング図は、抽象的な論理と物理的な現実の間の溝を埋める。エンジニアがデジタル電子回路の見えない制約を可視化できるようにする。それらを読み取る技術を学ぶことで、複雑なハードウェアの問題をトラブルシューティングできる。それらを描く技術を学ぶことで、あらゆる条件下でも信頼性高く動作する堅牢なシステムを設計できる。

このプロセスには忍耐と細部への注意が求められる。すべてのエッジ、すべての遅延、すべての電圧レベルが重要である。組み込みシステムがより高速かつ複雑になるにつれ、正確なタイミング図への依存はさらに増すだろう。それらをオプションのドキュメントではなく、重要な仕様として扱うべきである。

使用する部品のデータシートを分析することから始める。タイミング仕様を探し、その数値に基づいて図を描いてみる。自分の描いた図をツールからの実測値と比較する。この予測と検証のサイクルが、上位レベルの組み込み設計に必要な直感を育てる。

図はコミュニケーションのツールであることを忘れないでください。他のエンジニアに最小限の曖昧さで必要な情報を伝えるべきである。明確で正確なタイミング図は開発時間を短縮し、高コストなハードウェアの再設計を防ぐ。このスキルを習得する時間を投資すれば、エンジニアリングキャリアを通じて大きな利益が得られる。