信号の時間的な流れを理解することは、デジタル電子工学の基盤です。学部生エンジニアにとって、タイミング図の解釈を習得することは、単なる学術的な演習ではなく、信頼性の高いシステムを設計する上で不可欠なスキルです。これらの視覚的表現は、時間軸に沿った信号の挙動を明示し、クロックサイクル、データの有効性、制御信号の間の関係を明らかにします。これらの技術を十分に理解しないと、実際の環境下では単純な回路でさえも失敗する可能性があります。

本書では、タイミング図を効果的に読み取り、作成し、分析するために必要な基本原則をカバーします。同期設計と非同期設計のメカニズム、セットアップ時間およびホールド時間の重要性、回路の故障を引き起こすよくある落とし穴を避ける方法についても探求します。この記事の最後まで読んだ時点で、複雑なデジタル論理問題に取り組むための確固たる基礎が身につくでしょう。

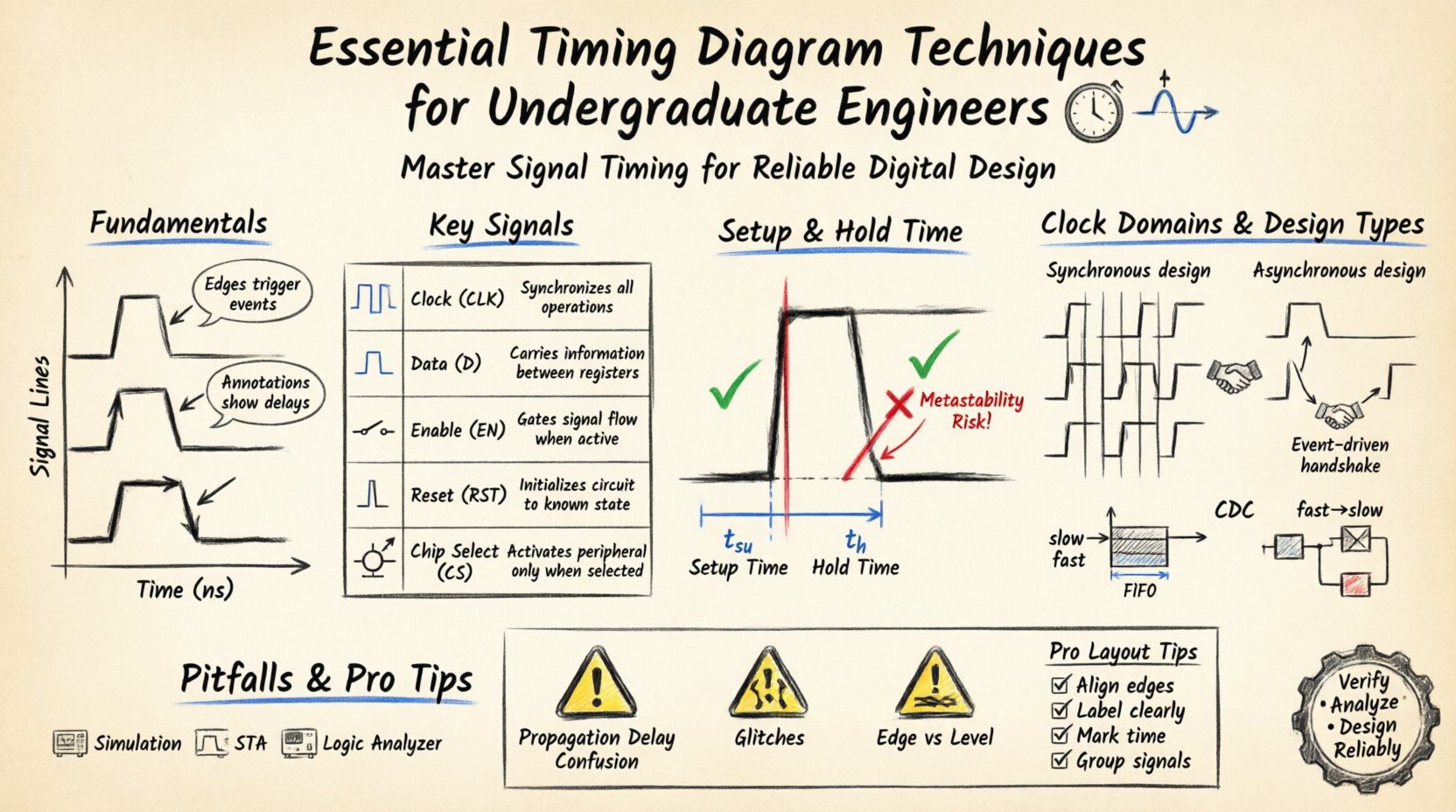

1. タイミング図の基礎 📐

タイミング図は、時間経過に伴う信号のグラフィカルな表現です。エンジニアがデジタル回路内のさまざまなラインの状態を可視化できるようにします。論理図が接続関係を示すのに対し、タイミング図は動作を示します。これらはデバッグや設計の検証、ハードウェアモジュール間の信号相互作用を伝えるために不可欠です。

タイミング図の主要な構成要素

- 時間軸(X軸):時間の進行を表します。通常はナノ秒(ns)またはクロックサイクル単位で目盛りが付けられます。

- 信号線(Y軸):個々のワイヤーやバスを表す水平線です。各線は特定の信号名に対応しています。

- 論理レベル:信号は一般的に2値であり、High(1)またはLow(0)として表されます。バス設計では、時折「High-Z」(高インピーダンス)状態が現れます。

- エッジ:垂直な遷移は状態の変化を示します。立ち上がりエッジ(LowからHigh)と立ち下がりエッジ(HighからLow)は、イベントのトリガーに重要です。

- 注記:テキストラベルは、遅延、特定の時間、または信号に影響を与える条件を示すことがよくあります。

デジタル論理におけるタイミングの重要性

デジタルシステムは正確な同期に依存しています。信号がクロックエッジに対して早すぎたり遅すぎたりすると、システムはデータを誤って解釈する可能性があります。タイミング図はこうした制約を可視化します。以下のような質問に答えるのに役立ちます:

- クロックエッジの前にデータは安定していますか?

- 信号がゲートを通過するのにどれくらいの時間がかかりますか?

- 異なるドメインからの2つのクロックは互いに干渉しますか?

2. 主要な信号とコンポーネント ⚡

複雑な波形を分析する前に、デジタル工学で使用される標準的な信号を認識する必要があります。これらの信号は、データの移動方法と、いつデータが有効とされるかを決定します。

一般的な信号タイプ

| 信号名 | 機能 | 典型的な挙動 |

|---|---|---|

| クロック(CLK) | 同期のソース | 0と1の間を定期的にパルスする |

| データ (D) | 情報の搬送体 | 入力または論理に基づいて状態を変更する |

| 有効化 (EN) | モジュールを有効化する | Highで動作を許可、Lowで無効化 |

| リセット (RST) | 状態を初期化する | スタート時にアクティブローまたはアクティブハイのパルス |

| チップ選択 (CS) | デバイスを選択する | アクティブローで特定のコンポーネントをアドレス指定する |

制御信号のアクティブ状態を理解することは重要です。一部の信号はアクティブハイであり、電圧が高いときに機能します。他の信号はアクティブローであり、名前の上にバーが付いている(例:/RESET または RST_N)と表記され、電圧が低いときに機能することを意味する。

3. ラッチアップ時間とホールド時間の解析 🕒

タイミング解析における最も重要な側面の一つが、セットアップ時間とホールド時間である。これらのパラメータは、データがクロックエッジに対して安定している必要がある時間窓を定義する。これらの制約を違反すると、データの破損やメタスタビリティが発生する。

セットアップ時間 (tsu)

セットアップ時間とは、データが安定している必要がある最小時間である。クロックエッジが到着するの前に安定している必要がある。データがクロックエッジに近すぎるように変化すると、フリップフロップは正しい値をキャプチャできなくなる可能性がある。

- 要件:データはtsuの立ち上がりエッジの前に安定している必要がある。

- 違反時の結果: レジスタは誤ったデータをキャプチャするか、定義されていない状態に入ることがあります。

ホールド時間 (th)

ホールド時間は、データが安定した状態を維持しなければならない最小時間です。の後アクティブなクロックエッジの後です。フリップフロップは、新しいデータが到着する可能性がある前に、値をロックするための時間が必要です。

- 要件: データはth リジングエッジの後、安定した状態を維持しなければなりません。

- 違反の結果:セットアップ違反と同様に、これによりデータエラーまたはメタスタビリティが発生します。

セットアップ時間とホールド時間の可視化

タイミング図を読む際には、データ信号がクロックエッジに対してどのように位置しているかを確認してください。セットアップウィンドウ(前)およびホールドウィンドウ(後)では、データラインは平坦で変化しない必要があります。これらのウィンドウ内でデータラインが切り替わっている場合、設計に問題がある可能性が高いです。

4. クロックドメインクロッシング ⏱️

複雑なシステムでは、回路の異なる部分が異なるクロック速度または周波数で動作することがあります。これらの異なるクロックドメイン間でデータを移動することをクロックドメインクロッシング(CDC)と呼びます。このプロセスは大きなタイミング上の課題をもたらします。

クロックドメインの種類

- 同じ周波数、同じ位相:同期設計。シンプルなタイミング解析が適用されます。

- 同じ周波数、異なる位相: 位相の整合性チェックが必要です。

- 異なる周波数: ハンドシェイクやFIFOバッファなどの同期技術が必要です。

タイミング図におけるCDCの取り扱い

複数のクロックドメインを含む図を分析する際には、クロックラインを明確に区別していることを確認してください。遅いドメインから速いドメインへデータを移動する場合、適切に管理されていないとリスクが高くなります。逆に、速いドメインから遅いドメインへ移動する場合、受信側が速くサンプリングするとデータ損失が発生する可能性があります。

- ハンドシェイクプロトコル: データ転送の完了を確認するために、valid/ready信号を使用します。

- FIFOバッファ: 生産速度と消費速度を分離します。

- 同期回路:メタスタビリティのリスクを低減するために、複数段のフリップフロップを使用する。

5. 同期設計と非同期設計 🔄

設計アーキテクチャがタイミング図の見た目を決定する。違いを理解することで、信号の挙動を予測しやすくなる。

同期設計

ほとんどのデジタル論理回路は同期的である。すべての状態変化は、中央のクロック信号のエッジで発生する。

- 予測可能性: 時刻が制御されているため、解析が容易になる。

- タイミング図: 定期的でグリッド状のパターン。データの変化はクロックエッジと整合する。

- 制限事項: 大規模な設計ではクロックスキーが問題になることがある。

非同期設計

状態変化は、グローバルクロックではなく信号の到着に基づいて発生する。これはハンドシェイクプロトコルや割り込み処理で一般的である。

- 柔軟性: データの到着のみを待つため、特定のタスクではより高速になることがある。

- タイミング図: 不規則。信号は固定された時間枠ではなく、前のイベントに依存する。

- リスク: 注意深く設計しないと、ラス条件やハザードに陥りやすい。

6. 一般的な落とし穴と誤り ❌

経験豊富なエンジニアですら、タイミング図の解釈や作成において誤りを犯すことがある。これらの一般的な誤りに気づいておくことで、大幅なデバッグ時間の節約になる。

1. 伝播遅延を無視する

信号は即座に変化しない。ゲートには伝播遅延がある。即座の変化を前提に図を描くと、シミュレーション結果は現実と一致しなくなる。

- 修正: 図の論理遷移の間に、常に遅延値を含める。

2. アクティブロー信号を誤解する

ラベルが付いた信号/CS はアクティブ時にローになる。高と仮定すると、論理が反転してしまう。

- 修正:アクティブ状態についてはデータシートまたは回路図を確認してください。論理ゲートにボイル(丸)があるか確認してください。

3. ギャップの見過ごし

ギャップは短い、意図しないパルスです。信号が遅延の異なる異なる経路を通過する際に発生することがあります。

- 修正:ハザードフリーな論理回路を使用するか、設計にフィルタ段を追加する。

4. エッジとレベルの混同

一部の回路は立ち上がりエッジでトリガーされ、他の回路は立ち下がりエッジで、また他の回路はレベルそのものでトリガーされます。

- 修正:コンポーネント仕様書のトリガー条件を確認する。

7. 専門的な図面の読み方と作成方法 📝

明確なコミュニケーションは工学において不可欠です。丁寧に描かれたタイミング図は、一目で複雑な情報を伝えることができます。以下は、それらを作成する際のベストプラクティスです。

レイアウトのベストプラクティス

- エッジを揃える:関連する信号が一定の間隔で変化するようにする。

- 明確にラベルを付ける:一般的な線だけではなく、信号名を使用する。

- 時間を明示する:サイクルの期間や特定の遅延を示す。

- 信号をグループ化する:関連する信号(データバスラインなど)をまとめて配置する。

ステップバイステップの作成プロセス

- クロックを特定する:まずクロック線を描く。これらはタイミングの基盤となる。

- 制御信号を追加する:Enable、Reset、チップセレクト線を配置する。

- データをプロットする:論理フローに基づいてデータ線を追加する。

- 注記する:セットアップ/ホールド時間や特定の遅延についての注記を追加する。

- レビュー:違反や論理的一貫性を確認してください。

8. 実世界のシナリオの分析 🔍

メモリ読み取り操作を含むシナリオを検討しましょう。これはマイコンを扱うエンジニアにとって一般的な作業です。

メモリ読み取りサイクル

メモリ読み取りでは、プロセッサがアドレスを送信し、読み取りコマンドをアサートしてデータを待機します。

- アドレスバス:クロックエッジの前に有効。

- チップセレクト:ローにすることでメモリをアクティブ化する。

- 読み取りコマンド:ローにすることで転送を開始する。

- データバス:メモリが駆動するまでハイ・Zの状態を維持する。

- タイミング: プロセッサがデータをサンプリングする前に、データは安定している必要がある。

信号整合性の考慮事項

周波数が増加するにつれて、信号整合性が大きな要因になります。反射、クロストーク、ノイズは波形を歪める可能性があります。高速設計におけるタイミング図は、これらの物理層の問題を考慮しなければなりません。

- スルーレート: シグナルの遷移速度。速すぎるとノイズが発生し、遅すぎるとタイミングエラーが生じる。

- 電圧レベル: 温度や電圧の変動にわたって論理閾値を満たすことを確認する。

9. 高度なタイミングコンセプト 🧠

専門知識を深めたい人向けに、いくつかの高度な概念が基本的なタイミング解析を拡張します。

メタスタビリティ

メタスタビリティは、フリップフロップが所定の時間内に安定した0または1の状態に到達できないときに発生します。これは通常、データがクロックエッジに非常に近いタイミングで変化した場合に起こります。

- 確率: これは決定論的ではなく、確率的なイベントである。

- 緩和策: 同期チェーン(複数のフリップフロップを直列に配置)を使用して、確率をほぼゼロに低下させる。

クロックスキュー

クロックスキューとは、回路内の異なる部分におけるクロック信号の到着時間の差を指す。正のスキー(遅れて到着)はセットアップ時間には有利だがホールド時間には不利である。負のスキーは逆の効果をもたらす。

- 設計への影響: スキューはタイミング予算に考慮しなければならない。

- 測定: スキューを測定するにはオシロスコープまたはシミュレーションツールを使用する。

ジッター

ジッターとは、クロックエッジが理想位置からずれる度合いを指す。これにより、実効的なセットアップ時間およびホールド時間の余裕が減少する。

- 種類:周期ジッター、サイクル対サイクルジッター、ランダムジッター。

- 影響: 高いジッターはシステムの最大動作周波数を制限する。

10. ツールと手法 🛠️

手動解析は教育的価値があるが、現代のエンジニアリングはツールに依存している。しかし、これらのツールを効果的に使うためには、背後にある理論を理解することが不可欠である。

シミュレーションソフトウェア

ハードウェア記述言語(HDL)を用いることでシミュレーションが可能になる。これらのツールはコードから自動的にタイミング図を生成する。コードの正しさを検証するためには、出力の理解が必須である。

静的タイミング解析(STA)

STAツールはシミュレーションを用いずに、すべての経路がタイミング要件を満たしているかを数学的に検証する。温度や電圧のすべての条件(コーナー)においてセットアップおよびホールド違反を確認する。

ロジックアナライザを用いたデバッグ

ハードウェアデバッグツールはボードからの実際の信号をキャプチャする。実際の状況に一致するタイミング図を表示することで、シミュレーションでは見逃されがちな物理層の問題を特定するのに役立つ。

結論 🏁

タイミング図はデジタル信号の挙動を表現する言語である。抽象的な論理と物理的な現実の間をつなぐ橋である。学部生のエンジニアにとって、これらの技術を習得するための時間投資は、キャリアを通じて大きなリターンをもたらす。シンプルなカウンタの設計から複雑なプロセッサの設計まで、タイミング制約を読み解き分析する能力は必須である。

セットアップ時間およびホールド時間に注目し、クロックドメインを理解し、一般的な落とし穴を避けることで、堅固な基盤を築くことができる。常にアクティブ状態を確認し、伝播遅延を考慮することを忘れないでください。進歩するにつれてより複雑な状況に直面するだろうが、基本原則は変わらない。図の分析を継続的に練習し、設計の信頼性と効率を高めていこう。

データシートを学び、実世界の回路波形を検討することで、スキルをさらに磨き続けよう。デジタルエンジニアリングの分野は急速に進化しているが、タイミング解析の基礎は常に変わらない。