タイミング図はデジタルシステム設計の基盤です。エンジニアが信号の時間的変化を説明するために使用する視覚的な言語を提供します。マイコンインターフェースの設計から通信プロトコルのデバッグまで、これらの図を理解することは必須です。このガイドでは、不要な複雑さを避けながら、図の作成と解釈のプロセスを段階的に説明します。

始める段階は難しく感じられるかもしれませんが、適切なフレームワークがあれば、効果的な図を素早く描くことができます。中心となる構成要素、信号遷移の背後にある論理、そしてシステムの信頼性を定義する重要なパラメータについて説明します。信号タイミングのメカニズムに深く入り込みましょう。

コアの目的を理解する 🧠

タイミング図は、システム内のイベントの順序をグラフィカルに表現したものです。信号の状態を共通の時間軸に対してマッピングします。物理的な接続を示すスケーマティック図とは異なり、タイミング図は時間的な関係に注目します。この違いは、静的回路解析では現れない論理エラーのデバッグにおいて極めて重要です。

これらの図を描くとき、あなたはデータ信号および制御信号の動作を記録しているのです。その目的は、ある信号が別の信号がそれに作用する前に準備ができていることを保証することです。この同期により、データの破損を防ぎ、安定した動作を確保します。

-

視覚的明確性: 抽象的な時間依存関係を具体的なものにします。

-

デバッグ支援: レースコンディションやセットアップ違反を強調します。

-

ドキュメント化: ハードウェアチームとソフトウェアチームの参考資料として機能します。

-

検証: 論理が仕様と一致しているかを検証するのに役立ちます。

明確な図がないと、特定の条件下でのみ発生する微細なタイミング問題を見逃しやすくなります。図の描き方を標準化することで、プロジェクトに関わるすべての人の曖昧さを軽減できます。

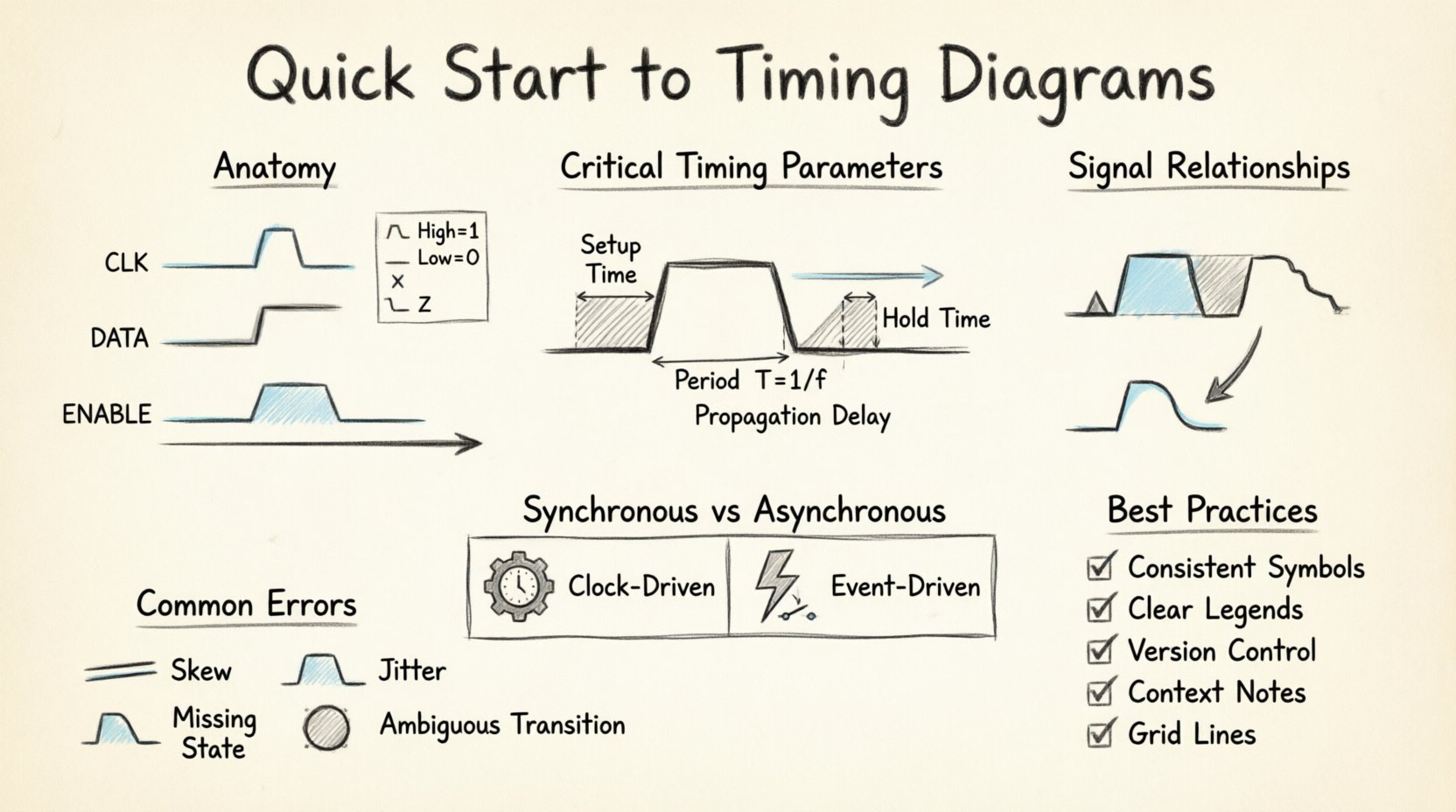

タイミング図の構造 📐

すべてのタイミング図には共通の構造があります。この構造を習得することで、複雑な波形を簡単に読み取ることができます。このレイアウトは、組み込みシステムから高速ネットワーキングに至るまで、さまざまな工学分野で一貫しています。

1. 時間軸 ⏰

水平軸は時間を表します。左から右へと流れます。すべての文脈で時間は線形であるとは限りませんが、ほとんどの標準的な図では、等しい距離が等しい時間間隔を表します。毎ミリ秒をラベル付けする必要はありませんが、重要な時間間隔をマークすることで、情報のスケーリングが容易になります。

-

方向:常に左から右へ。

-

スケール:信号の周波数に応じて、線形または対数スケールにすることができます。

-

マーカー:クロックエッジのような特定のイベントを示すために、垂直線を使用します。

2. 信号線 📊

信号は垂直に積み重ねられた水平線で表されます。各線は回路内の特定のワイヤーやネットに対応します。信号の名前は通常、線の左側または右側に表示されます。

-

グループ化:アドレス線やデータ線など、関連する信号はしばしば一緒にグループ化されます。

-

ラベル付け:類似した名前間の混乱を避けるために、信号には明確にラベルを付けるようにしてください。

-

順序:慣習に応じて、最も重要な信号を上部または下部に配置してください。

3. ロジックレベル 🔋

信号は定義された状態の間を切り替わります。デジタル論理では、これらは通常High(高)とLow(低)、または1と0です。線の垂直位置が状態を示しています。

|

状態 |

一般的な表記 |

物理的意味 |

|---|---|---|

|

High(高) |

1、H、VCC |

正の電圧レール |

|

Low(低) |

0、L、GND |

グランドまたはゼロ電圧 |

|

不明 |

X |

不定状態 |

|

高インピーダンス |

Z |

接続されていない、または浮遊状態 |

これらのレベルを理解することは、図面を読む第一歩です。これらのレベル間の遷移が、動作が起こる場所です。

重要なタイミングパラメータ ⚙️

タイミングは線を引くことだけではなく、制約を定義することです。特定のパラメータが、信号がどれだけ速く変化できるか、そしていつ安定している必要があるかを規定します。これらの制約は、システムが正しく機能することを保証するために不可欠です。

1. セットアップ時間 ⏳

セットアップ時間は、クロックエッジが到着する前にデータ信号が安定している必要がある最小時間です。データがクロックエッジに近すぎるように変化すると、システムが誤った値をキャプチャする可能性があります。これは同期システムにおける重要な制約です。

-

定義:アクティブなクロックエッジの前の時間。

-

違反:メタスタビリティまたは誤ったデータキャプチャを引き起こす。

-

設計ルール: データがクロックのトリガー発生前に十分安定していることを確認する。

2. ホールド時間 ⏳

ホールド時間とは、クロックエッジの後にデータ信号が安定していなければならない最小時間である。信号がトリガーの直後に早すぎるように変化すると、受信要素が値を正しくラッチできない可能性がある。

-

定義:アクティブなクロックエッジ後の時間。

-

違反:セットアップ時間と同様に、データエラーを引き起こす。

-

設計ルール: クロックの直後に信号がトグルしないようにする。

3. 伝播遅延 ⏱️

伝播遅延とは、信号がコンポーネントの入力から出力まで到達するまでの時間である。電子部品はすべて即時ではない。この遅延は複数段にわたって蓄積され、高速設計では考慮しなければならない。

-

原因:内部ゲート遅延と配線長。

-

影響: 最大動作周波数を制限する。

-

測定方法: 入力の50%点から出力の50%点まで測定する。

4. 周期と周波数 🔁

クロック信号の場合、周期とは波形上の連続する同じ点の間の時間(例:立ち上がりエッジから立ち上がりエッジまで)である。周波数は周期の逆数である。

-

周期: T = 1 / f

-

デューティーサイクル: 1周期内において信号がハイ状態である時間の割合。

-

安定性: クロックジッターはタイミングの精度に影響する。

信号関係の読み取りと分析 🔄

コンポーネントを理解したら、次は信号どうしがどのように相互作用するかを分析する段階である。ここが図が診断ツールとして機能する場所である。依存関係や潜在的な衝突を検出する。

1. エッジトリガリング 📉

ほとんどのデジタル回路はクロックの特定のエッジでトリガされる。一部は立ち上がりエッジでトリガされ、他のものは立ち下がりエッジを使用する。システム内の各コンポーネントでどのエッジがアクティブかを特定しなければならない。

-

立ち上がりエッジ:ローからハイへの遷移。

-

下降エッジ:ハイからローへの遷移。

-

両エッジ:一部のシステムは両方の遷移でデータをサンプリングする。

図を描く際は、どのエッジがアクティブかを示すために小さな三角形や溝を使うこと。これにより実装時の混乱を防ぐ。

2. データ有効ウィンドウ 🕒

データは特定のウィンドウ内でのみ有効である。セットアップ時間より前、およびホールド時間より後は、データラインが変化してはならない。このウィンドウ外では、データは有効とみなされる。図にこのウィンドウをマークすることで、期待される動作が明確になる。

-

ウィンドウ:セットアップ時間+ホールド時間+伝播遅延によって定義される。

-

違反:データがこのウィンドウ外で変化すると、エラーが発生する。

-

視覚的サイン:有効なデータ期間を強調するために、陰影付き領域を使う。

3. 非同期信号 📡

すべての信号がクロックに従うわけではない。割り込みやリセットなどの非同期信号は独立して動作する。タイミング図では、それらの優先順位や遅延を明確に示すために注意深く扱う必要がある。

-

優先順位:割り込みは通常、クロックサイクルよりも優先される。

-

遅延:アサーションと応答の間の遅延に注意する。

-

安定性:非同期信号がセットアップ/ホールド要件を満たすために安定していることを確認する。

同期系と非同期系のシステム 📡

同期設計と非同期設計の違いは、図の作成方法に影響を与える。それぞれのアプローチには特定のルールと慣習がある。

|

特徴 |

同期 |

非同期 |

|---|---|---|

|

制御 |

クロックによって駆動される |

イベントによって駆動される |

|

予測 |

タイミングの予測が容易 |

タイミングの予測が難しい |

|

複雑さ |

標準化された論理 |

ハンドシェイクプロトコル |

|

電力 |

クロックによる高電力 |

しばしば低い |

同期図では、すべての他の信号を同期させる主要なクロック線が見える。非同期図では、ハンドシェイクや待機状態が見える。両方とも正確なタイミングドキュメントが必要である。

一般的な誤りとその回避方法 ⚠️

タイミング図の誤りは、高コストなハードウェアの再設計を招くことがある。一般的な落とし穴を認識することで、より明確で正確な表現が可能になる。

1. スキューの無視 📏

スキューとは、信号が異なる点に到着する時間の差を指す。すべての信号が同時に到着すると仮定すると、タイミング違反を見逃す可能性がある。常に配線長や負荷の違いを考慮する必要がある。

-

確認点:異なる受信点での到着時間を比較する。

-

修正:遅延バッファを追加するか、トレース長を調整する。

-

視覚的表現:スキューが顕著な場合は、平行線にわずかなオフセットを表示する。

2. ジッターの見過ごし ⚡

ジッターとは、信号のタイミングのばらつきを指す。クロックが完全に周期的でない場合がある。高速設計では、ジッターがタイミングマージンを削る原因となる。ジッターはクロックエッジの周囲に陰影をつけて表現する。

-

原因:電源ノイズまたは外部干渉。

-

影響:有効なセットアップ時間およびホールド時間の短縮を引き起こす。

-

視覚的表現:不確実性を示すために、ぼやけた線や帯を使う。

3. 明確でない遷移 🔄

直線のように見える遷移は、実際には傾斜している可能性がある。実際の信号は瞬時に変化しない。完全な垂直線を描くことは、無限の速度を意味し、物理的に不可能である。

-

ベストプラクティス:正確性が求められる場合は、遷移をわずかに傾斜させて描く。

-

慣例:垂直線は論理的な表現として許容される。

-

明確さ:傾斜に関係なく、意図が明確になるようにする。

4. 状態遷移の欠落 🚦

複雑な状態機械には、明らかでない中間状態がしばしば存在する。開始状態と終了状態だけを描くと、遷移の順序に関する重要な情報を失う。

-

詳細:関連するすべての状態変化を表示する。

-

ラベル:状態に名前または値を注釈する。

-

論理:図が実際の論理フローを反映していることを確認する。

ドキュメント作成のベストプラクティス 📝

図が何年経っても有用であることを確実にするため、一貫したスタイルを守る。これにより、保守や他のエンジニアとの共有が容易になる。

-

一貫した記号:全体を通して同じ矢印の先端と線のスタイルを使用する。

-

明確な凡例:使用したカスタム記号や省略記号を定義する。

-

バージョン管理:図にバージョン番号と日付をラベルする。

-

文脈:図示しているシステムの簡単な説明を含める。

-

グリッド線:グリッドを使用して信号を整列させ、時間間隔をマークする。

一貫性があることで、あなたの作業を読む人の認知負荷が軽減される。また、後で図を確認する際に異常を発見しやすくなる。

タイミング解析によるトラブルシューティング 🛠️

システムが故障した際、タイミング図はまず確認すべき場所であることが多い。これにより、問題が論理的か時間的かを特定しやすくなる。

1. レースコンディションの特定 🏁

競合状態とは、出力がイベントの順序に依存する場合に発生する。2つの信号が同時にゲートに到達すると、結果は予測不能になる可能性がある。タイミング図はこうした重複を明らかにする。

-

以下の点を確認する: 同時に交差する信号。

-

解決策: バッファを追加するか、論理の順序を再調整する。

-

防止策: 同時遷移を避けるために余裕を持った設計を行う。

2. ギャップの検出 ⚡

ギャップは、伝播遅延によって生じる短いパルスである。意図しないタイミングでフリップフロップをトリガーする可能性がある。図では、安定したレベルの間に細長いスパイクとして現れる。

-

視覚的特徴: クロック周期と一致しない細いパルス。

-

修正法: フィルタリングを行うか、安定したエッジで信号をラッチする。

-

解析: パルス幅がホールド時間以上かどうかを確認する。

3. バスプロトコルの検証 📡

I2CやSPIなどのバスは厳密なタイミング要件を持つ。開始・停止条件、クロックストレッチ、データシフトは完全に整合している必要がある。タイミング図は、こうしたプロトコルを検証する標準的な方法である。

-

開始/停止: クロックに対してデータライン上の正しい遷移を確認する。

-

ストレッチ: スレーブが必要な期間、クロックをローに保持できることを確認する。

-

データ: クロックのハイ期間中にデータが安定していることを確認する。

信号整合性に関する最終的な考察 🎯

正確なタイミング図を作成することは、練習を重ねるほど向上するスキルである。電子回路が時間とともにどのように振る舞うかを深く理解する必要がある。上記のガイドラインに従うことで、情報豊かで信頼性の高い図を描くことができる。

これらの図はコミュニケーションツールであることを忘れないでください。理論と実装の間のギャップを埋める役割を果たす。タイミング図を描くということは、システムの振る舞いについて物語を語っていることである。その物語を明確で正確かつ一貫性を持たせよう。

必須のパラメータに注目する:セットアップ、ホールド、遅延、スケュー。レイアウトは簡潔に、ラベルは曖昧でないようにする。こうした習慣を身につけることで、タイミング図を描くことが設計プロセスの自然な一部になる。数時間ではなく、数分で完成できるようになるだろう。