デジタルシステム内の信号の流れを理解することは、ハードウェア、ファームウェア、または組み込みソフトウェアに従事するエンジニアにとって不可欠です。タイミング図は、特定の期間における異なる信号の相互作用を可視化する主な視覚的ツールです。この視覚的表現により、チームはデータが正しくキャプチャされているか、クロックが安定しているか、論理遷移が衝突なく発生しているかを確認できます。これらの図の正確な理解がなければ、システムの信頼性は著しく低下します。本ガイドでは、タイミング図を構成する基本的な要素について解説し、正確な設計と分析を確保します。

タイミング図とは何か? 📊

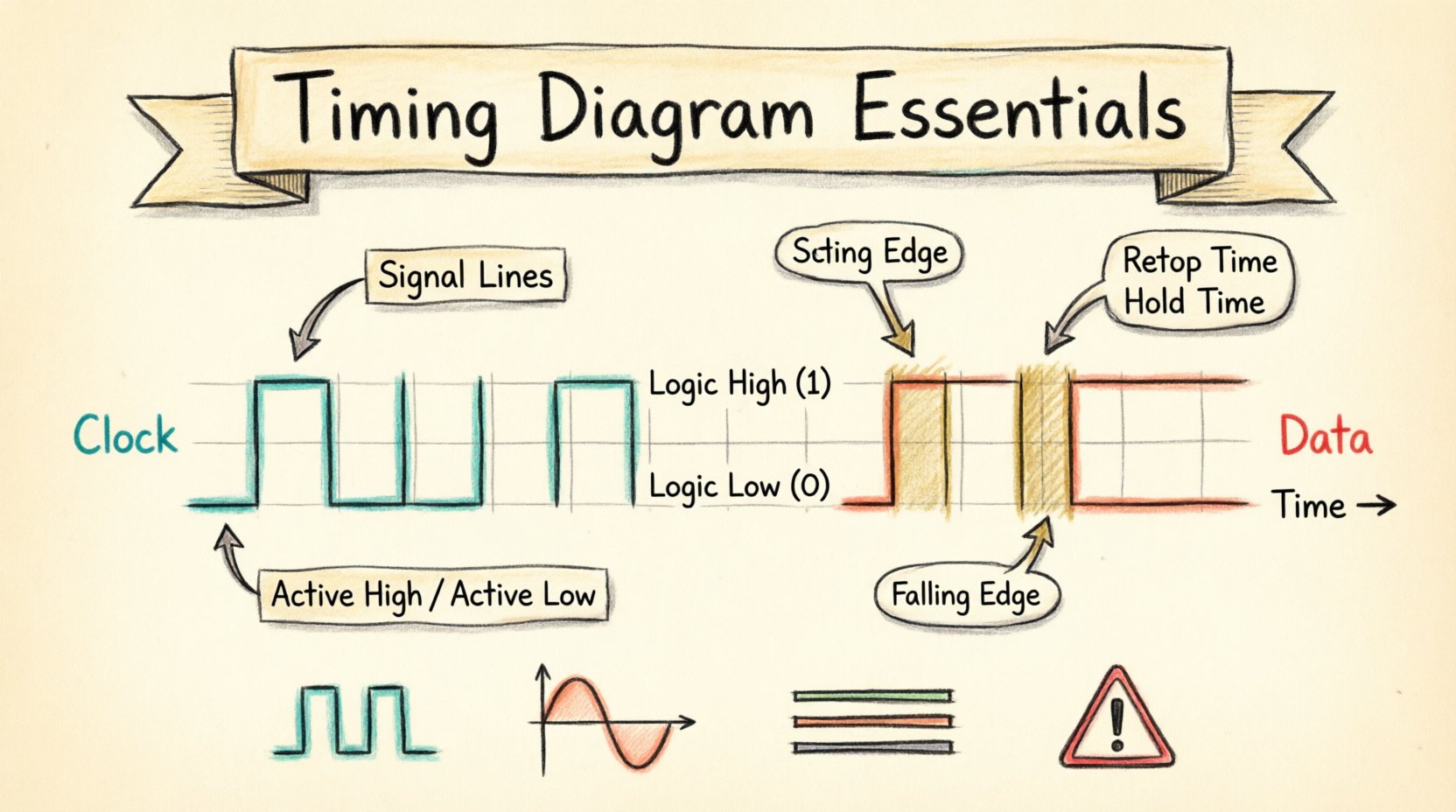

タイミング図は、時間の経過とともに2つ以上の信号の挙動を図示したグラフィカルな表現です。イベントの順序をマッピングし、信号が状態を変化するタイミング、その状態がどのくらい続くか、またクロック源との関係を示します。ハードウェア設計では、これらの図はコンポーネント間の通信が正しく行われているかを検証するために不可欠です。ソフトウェアでは、並行処理、レースコンディション、同期ポイントを可視化するのに役立ちます。

これらの図では、通常、時間軸を横軸(x軸)に、信号レベルまたは状態を縦軸(y軸)にプロットします。垂直線は特定の時刻を表し、水平線は信号の安定状態を示します。これらの状態間の遷移は、システム内で実際に発生しているデータ転送や制御動作を示すため、非常に重要です。

タイミング図の核心的な構成要素 🔧

効果的なタイミング図を読み取る、または作成するには、基本的な構成要素を理解する必要があります。複雑さに関係なく、すべての図は正確な情報を伝えるために一貫した要素のセットに依存しています。

- 時間軸:時間の進行を表す水平基準線です。通常、左から右へと流れ、過去から未来を示します。

- 信号線:特定のワイヤ、バス、または変数に割り当てられた水平なトラックです。各線は特定の信号の論理レベルを表します。

- 論理レベル:信号線上の垂直位置です。通常、高(1、Vcc、True)と低(0、Gnd、False)の状態が表示されます。

- 遷移:論理レベルをつなぐ垂直線です。リジングエッジは低から高へ、フェリングエッジは高から低へ移動します。

- 注記:特定のイベント、遅延、または状態を明確にするためのテキストラベルやマーカーです。

時間軸:正確さが重要です ⏳

時間軸は図の基盤です。必ずしも現実の秒を表すわけではなく、設計速度に応じてクロックサイクルやナノ秒を表すことが多いです。スケーリングの一貫性が非常に重要です。図の一部で1グリッドセルあたり10ナノ秒を示している場合、別の部分もそのスケールを維持する必要があります。詳細を明示的に拡大表示する場合を除きます。

システム性能を分析する際、時間軸はボトルネックを特定するのに役立ちます。たとえば、データ信号が安定するのに50ナノ秒かかるのに、クロックエッジが40ナノ秒後に発生する場合、違反が発生します。この軸により、エンジニアはこれらの間隔を直接測定できます。

信号線と論理レベル 🔄

各信号線は物理的なワイヤまたは論理変数に対応します。複雑なシステムでは、バスは複数の信号がグループ化された太い線で表される場合や、各ビットごとに個別の線で表される場合があります。論理レベルは信号の状態を定義します:

- アクティブハイ:電圧が高くなったときに、信号は「オン」または「真」であるとみなされます。

- アクティブロー:電圧が低くなったときに、信号は「オン」または「真」であるとみなされます。これは、シンボルにボブルを付けるか、特定の命名規則で示されることがよくあります。

アクティブ状態を理解することは、「チップセレクト」や「ライト有効」などの制御信号を解釈する上で不可欠です。アクティブローの信号をアクティブハイと誤解すると、デバッグが困難な設計失敗を引き起こす可能性があります。

遷移とエッジ ⚡

信号が一つの論理レベルから別の論理レベルに変化するときに遷移が発生します。物理世界ではこれらの変化はほとんど瞬時に起こらないものの、タイミング図では理想の変化瞬間を表すためにしばしば垂直線として描かれます。

- リジングエッジ: 低から高への遷移。これはしばしば同期論理のトリガーポイントとなる。

- 下降エッジ: 高から低への遷移。一部のシステムでは、このエッジをデータキャプチャに使用する。

- エッジトリガー: 遷移の瞬間にのみ反応する論理。

- レベルトリガー: シグナルが特定の状態に保たれている間、常に反応する論理。

現実の信号には立ち上がり時間と立ち下がり時間が存在する。完全な垂直線は抽象的な表現である。高速設計では、遷移の傾きが重要であり、それは電磁干渉や信号整合性に影響を与える。

タイミングパラメータと制約 📐

視覚的な線を超えて、タイミング図の重要な価値は、信号と共に定義された定量的パラメータにある。これらのパラメータが、ハードウェアが動作しなければならない物理的限界を規定する。

セットアップ時間とホールド時間 ⚙️

これらは、データがクロックエッジでフリップフロップによってキャプチャされる場合に特に重要な、順序論理設計における最も一般的な制約の2つである。

- セットアップ時間: データ信号が安定している必要がある最小時間クロックエッジの前。データがクロックエッジに近すぎるように変化すると、フリップフロップが正しい値をキャプチャできなくなる可能性がある。

- ホールド時間: データ信号が安定を保つ必要がある最小時間クロックエッジの後。データがエッジの直後に早すぎるように変化すると、キャプチャが破損する可能性がある。

| パラメータ | 定義 | 違反時の結果 |

|---|---|---|

| セットアップ時間 | データがクロックエッジの前に安定している時間 | メタスタビリティまたは誤ったデータキャプチャ |

| ホールド時間 | データがクロックエッジの後に安定している時間 | メタスタビリティまたは誤ったデータキャプチャ |

| プロパゲーション遅延 | ゲートを通過する信号にかかる時間 | タイミングスラックの減少、最大周波数の低下 |

| クロックスキュー | クロック信号の到着時間の差 | 有効タイミングウィンドウの縮小 |

伝播遅延 ⏱️

伝播遅延とは、入力の変化が出力に影響を与えるまでにかかる時間です。タイミング図では、クロックエッジとそれに伴うデータ変化の間のギャップとして確認できます。この遅延は、配線の静電容量やトランジスタのスイッチング速度といった物理的制限によって引き起こされます。

システムを設計する際、経路に沿った伝播遅延の合計は、クロック周期からセットアップ時間分を引いた値よりも小さくなければなりません。遅延が長すぎると、システムは希望するクロック速度で動作できなくなります。

クロックスキーとジッター 📉

クロックスキーとは、クロック信号が回路の異なる部分に到着する時間の差を指します。理想的な図では、クロックラインは垂直であり、すべての部品で同時に到着します。実際には、配線の違いがスキーを引き起こします。ポジティブスキーとは、クロックが目的地に遅れて到着することを意味し、セットアップ時間には有利ですが、ホールド時間には悪影響を与えます。

ジッターとは、信号エッジのタイミングのばらつきを指します。これはノイズであり、エッジが予想よりも早くまたは遅く発生する原因になります。高いジッターは有効なタイミングマージンを低下させ、安定性を維持するためにシステムを遅く動作させる必要が生じます。

信号およびバスの種類 📡

異なるシステムでは、異なる信号方式が使用されます。タイミング図が正確であるためには、これらの違いを反映しなければなりません。

デジタル信号

ほとんどのタイミング図はデジタル論理に注目しています。これらの信号は2値であり、0と1の間を切り替わります。図の明確さは、論理閾値を明確にマークすることに依存します。一部の信号は中間状態や「気にしない」状態を持つことがあり、通常はXで示されます。

アナログ信号

純粋なデジタルタイミング図ではあまり見られないものの、電圧レールやセンサ出力などのアナログ信号が時折含まれることがあります。これらは急な段差ではなく、傾斜または曲線で表現され、離散的な状態変化ではなく連続的な変化を示します。

バスと並列データ

複数のビットが同時に伝送される場合、しばしばグループ化されます。バスタイミング図は、すべてのビットの状態を一度に表示します。バス幅(例:8ビット、32ビット)を明確にラベル付けし、すべてのビットが同時に安定している有効データウィンドウを示すことが不可欠です。

タイミング図の読み方:ステップバイステップガイド 🔍

これらの図を解釈するには、重要な詳細を見逃さないために体系的なアプローチが必要です。

- クロックを特定する:主なタイミングリファレンスを特定する。他のすべてのイベントは、このラインを基準に測定されるべきである。

- エッジ感度を確認する:システムがクロックの立ち上がりエッジまたは立ち下がりエッジでトリガされるかどうかを確認する。

- データ有効性を追跡する:データラインが安定している期間を探す。これが「有効ウィンドウ」である。

- 制御信号を確認する:データ転送を制御する有効、リセット、またはチップ選択ラインを特定する。

- インターバルを測定する: 時間軸を用いて遅延、セットアップ時間、パルス幅を測定する。

一般的なタイミング違反とエラー ⚠️

慎重な計画を立てても、タイミング違反は発生する。図から兆候を認識することは、それらを修正する第一歩である。

- セットアップ違反: データが次のクロックエッジに対して遅れて到着する。この問題の解決策は、クロックを遅くするか、遅延を減らすために論理パスを最適化することが多い。

- ホールド違反: データがクロックエッジの直後に早すぎることに変化する。これは、データパスまたはクロックパスに遅延を追加する必要があるため、修正が難しいことが多い。

- メタスタビリティ: フリップフロップの出力が、定義されない期間、0でも1でもない状態にあること。これは通常、セットアップ時間またはホールド時間が違反されたときに発生する。

- グリッチ: 組み合わせ論理におけるライス条件によって引き起こされる短い、意図しないパルス。フィルタリングされない場合、誤った状態変化を引き起こす可能性がある。

非同期設計と同期設計 🔄

タイミング図は、設計手法によって異なる見た目になる。

同期設計

イベントはグローバルクロックによって調整される。タイミング図では明確で周期的なクロック線が表示される。データの変化はクロックエッジでのみ発生する。このアプローチは、タイミングウィンドウが固定されているため、解析を簡素化する。

非同期設計

イベントはハンドシェイク信号(リクエストやアックノリッジなど)によって調整される。タイミング図では、イベント間の間隔が不規則に表示される。より柔軟ではあるが、固定された時間基準がないため、解析が難しい。

プロトコルにおける応用 📡

通信プロトコルは正確なタイミングに大きく依存している。図を理解することが、これらの標準を実装する鍵となる。

シリアル通信

シリアルインターフェースは、1ビットずつデータを送信する。タイミング図にはビット期間が表示される。クロックとデータラインの関係(例:立ち上がりエッジでデータが有効)が、プロトコルのルールを定義する。

並列通信

並列インターフェースは、複数のビットを一度に送信する。タイミング図には、バス全体のセットアップ時間を示す必要がある。すべてのビットはラッチエッジが発生する前に安定している必要がある。

ドキュメント作成のベストプラクティス 📝

明確なドキュメントを作成することで、他のエンジニアが曖昧さなくシステムを理解できることが保証される。

- 一貫したラベルを使用する: シグナルの名前は、コードや回路図に表示されている通りに正確に付ける。

- 単位を含める: 軸上には常に時間単位(ns、µs、サイクル)を明記する。

- 重要なパスを強調する: 最もタイミングに敏感な信号を強調するために太線または色を使用する。

- 違反を注記する: 違反がわかっている場合は、隠すのではなく明確にマークする。

- 常に最新の状態を保つ: デザインが変更されたら、図を常に更新する。古くなった図はバグの主要な原因となる。

高度な考慮事項:マルチクロックドメイン 🌐

現代のシステムはしばしば、異なる速度で動作する複数のクロックドメインで動作する。これらのシステムのタイミング図は、クロック間の関係を明確に示さなければならない。

- クロック間遷移: 高速ドメインから低速ドメインへデータが移動する場合、データ損失を避けるために慎重な同期が必要である。

- 位相関係: 2つのクロックが同じソースを持つが位相が異なる場合、図には位相差を示さなければならない。

- ハンドシェイク論理: ドメイン間の非同期ブリッジはハンドシェイク信号に依存する。タイミング図は、リクエストから承認までの完全なサイクルを示さなければならない。

シミュレーションのタイミング解析における役割 💻

ハードウェアが構築される前に、シミュレーションでタイミング図の検証が行われる。エンジニアは波形ビューアを使用して、期待される動作とシミュレーション結果を比較する。

- 静的タイミング解析: 実際の波形をシミュレートせずに、最悪ケースの遅延を計算する。

- 動的タイミングシミュレーション: 回路の仮想版を実行して、実際の波形を生成する。

- レイアウト後シミュレーション: チップ設計後に、物理的な配線長や静電容量を考慮する。

これらのツールにより、エンジニアはタイミング図を物理的な現実と照合できる。シミュレーションでセットアップ違反が示された場合、製造前に設計を修正しなければならない。

タイミング精度に関する結論 ✅

タイミング図の作成と解釈を習得することは、技術職にとって基本的なスキルである。これらの図は、抽象的な論理と物理的な現実の間の橋渡しを行う。信号が必要なときに、正しい状態で、システムが機能するのに十分な安定性を持って到着することを保証する。このガイドで提示された要素と制約に従うことで、チームはエラーを減らし、システムの信頼性を向上させることができる。これらの視覚的表現における細部への注意は、最終製品の安定性と性能において大きな成果をもたらす。

高速メモリインターフェース、低消費電力マイコン、あるいは複雑なデータバスの開発に携わろうとも、原則は同じである。時間は定数であり、信号は変数である。それらの関係を理解することが、成功するエンジニアリングの鍵となる。