デジタル電子工学およびコンピュータ工学の世界では、信号は真空の中に存在するわけではない。信号はトレースを通り、ゲートを通り、プロセッサに特定の時間的制約を伴って到達する。システムの動作を理解するためには、エンジニアはこれらの信号が時間とともにどのように変化するかを可視化しなければならない。この可視化はタイミング図によって実現される。初心者にとっては、これらの図は複雑な象形文字のように見えるかもしれないが、実際にはデジタル論理のデバッグや設計において最も基本的なツールなのである。

このガイドでは、タイミング図の詳細な解説を行う。信号の構造、信頼性を定義する重要なパラメータ、そしてシステム障害を引き起こすよくある落とし穴について探求する。試験勉強中であろうと、初めてマイコン回路を設計しようとしているであろうと、これらの図を理解することは必須である。

🧠 タイミング図とは何か?

タイミング図は、時間の経過とともにデジタル信号の状態をグラフィカルに表現したものです。回路図とは異なり、回路図は「何にと何にが接続されているかを示すのに対し、タイミング図は「いつことが起こるかを示す。電圧レベルを時間軸に対してプロットすることで、エンジニアはイベントの順序を把握できる。

これらの図は、いくつかの理由から不可欠である:

- デバッグ:信号が順序通りに到着しないレースコンディションを明らかにする。

- 検証:回路が要求される速度仕様を満たしていることを確認する。

- ドキュメント化:異なるチップ間の通信方法を参照するための基準となる。

- 設計:システムがサポートできる最大クロック周波数を決定するのを助ける。

タイミング図を見ることで、システム内を移動する電子の物理的挙動のスナップショットを見ていることになる。遅延、伝搬、同期の現実を捉えているのだ。

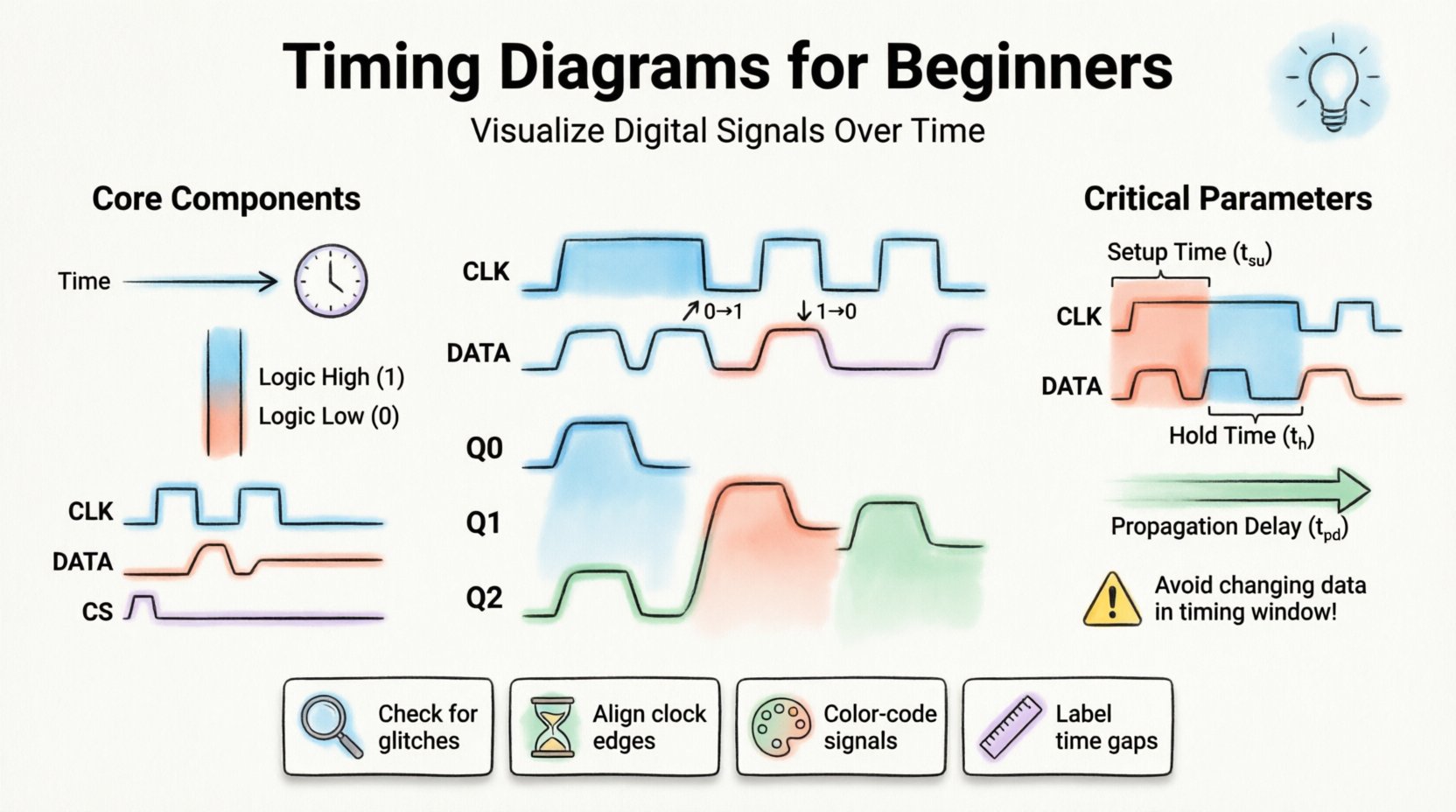

📊 タイミング図の核心的な構成要素

複雑な波形を分析する前に、基本構成要素を理解しなければならない。すべてのタイミング図は、いくつかの基本的な要素で構成されている。

1. 時間軸

水平軸は時間を表す。左から右へと流れている。デジタル設計では、この軸は通常、垂直のグリッド線で区切られたクロックサイクルに分割される。スケールは高速プロセッサではナノ秒(ns)から、遅い制御論理ではミリ秒(ms)まで変化する。

2. 電圧レベル軸

垂直軸は信号の論理状態を表す。標準的な論理ファミリーでは、通常は2値である:

- 論理高(1):通常はVCCまたは5Vとして表される。

- 論理低(0): よく接地または0Vとして表される。

- High-Z(高インピーダンス): ピンが実質的に切断された状態で、バスシステムで一般的である。

3. シグナルライン

各水平線は特定のワイヤーまたはシグナル名を表す。これらのラインは明確にラベル付けされている(例:CLK、DATA_IN、CS)ことで、回路のどの部分をモニタリングしているかを識別できる。

🔄 シグナル遷移の読み取り

シグナルラインの上下の動きがデータが存在する場所である。これらの動きの方向を理解することは非常に重要である。

⬆️ ライジングエッジ

シグナルがローからハイに遷移するときにライジングエッジが発生する。2進論理では、多くの操作のトリガーポイントとしてよく使われる。0から1への変化を表す。

⬇️ フェリングエッジ

シグナルがハイからローに遷移するときにフェリングエッジが発生する。1から0への変化を表す。

⚡ エッジトリガリング

多くのデジタルコンポーネント、例えばフリップフロップは、安定状態ではなくこれらのエッジにのみ反応する。フリップフロップはクロック信号のライジングエッジでデータをキャプチャする場合がある。エッジを逃すと、データは失われる。

| 遷移 | 方向 | 2進変化 | 一般的なトリガータイプ |

|---|---|---|---|

| ライジングエッジ | ロー ➔ ハイ | 0 ➔ 1 | ポジティブエッジトリガード |

| フェリングエッジ | ハイ ➔ ロー | 1 ➔ 0 | ネガティブエッジトリガード |

| レベルハイ | 安定したハイ | 安定した1 | レベル感応 |

| レベル低 | 安定低 | 安定0 | レベル感応 |

⏳ 重要なタイミングパラメータ

タイミング図は単なる図面ではなく、測定値を含んでいます。信号の変化の間隔が信頼性が決まる場所です。デジタルタイミング解析を支配する3つの特定のパラメータがあります。

1. 伝播遅延(tpd)

信号は即座に伝わるわけではありません。入力が変化したとき、出力がその変化を反映するまで有限の時間がかかります。これが伝播遅延です。これは材料の物理的抵抗と静電容量によって引き起こされます。

- 定義: 入力の変化と出力の変化との時間差。

- 影響: 論理ゲートの連鎖では遅延が蓄積されます。遅延が長すぎると、信号が次のクロックサイクルが始まった後に到着する可能性があり、エラーを引き起こします。

2. ライズ時間(tsu)

セットアップ時間は、データ信号が安定している必要がある時間ですクロックエッジが到着する 前に。データがクロックエッジに近すぎるように変化すると、受信回路は正しくそれをキャプチャできなくなります。

- ルール: データはクロックがトリガーする前に特定の期間、有効でなければならない。

- 図示: 図では、データラインが安定してからクロックエッジまでの間隔を指します。

3. ホールド時間(th)

ホールド時間は、データ信号が安定したまま維持される必要がある時間ですクロックエッジの後 クロックエッジが到着する。データがクロックエッジの直後に変化すると、回路が正しい値をラッチできない可能性がある。

- ルール: データはクロックがトリガーされた後、特定の期間にわたり変化してはならない。

- 視覚的表現: 図では、クロックエッジと次のデータ遷移の間の隙間を指す。

⚠️ 時刻ウィンドウ

セットアップ時間とホールド時間の組み合わせにより、データを正しくキャプチャするための有効なウィンドウが生じる。タイミング図でデータがこのウィンドウ内で変化している場合、システムは障害のリスクにさらされている。

⚡ 同期型と非同期型システム

タイミング図は、システムのアーキテクチャによって大きく異なる。

同期型システム

同期設計では、すべての操作がグローバルなクロック信号によって調整される。すべての状態変化はこのクロックのエッジで発生する。これらのシステムのタイミング図は非常に規則的である。

- 特徴: 予測可能で設計が容易だが、クロック速度に制限される。

- 図の見た目: 垂直のグリッド線がすべての信号変化と完全に一致する。

非同期型システム

非同期設計ではグローバルクロックがない。入力が変化するたびに信号が変化する。これにより高い速度の可能性があるが、タイミング解析がはるかに難しくなる。

- 特徴: 入力への応答が速いが、ハザード解析が複雑になる。

- 図の見た目: 信号の遷移は不規則な間隔で発生する。イベント間の正確な時間差を測定しなければならない。

📝 タイミング図の描き方

タイミング図を作成することは体系的なプロセスである。回路を文書化するか、設計を検証するには、以下の手順に従う。

- 信号を特定する: すべての入力、出力、内部制御線をリストアップする。明確にラベルを付ける。

- 時間基準を設定する: 時間スケールを決定する。論理回路では、クロックサイクルが通常の単位となる。

- クロックをプロットする: 常にクロック信号を最初に描く。他のすべてのイベントの基準となる。

- 入力をマッピングする 論理演算またはテストシーケンスに基づいて、入力波形を描画する。

- 遅延を計算する: 関与するゲートの伝播遅延に基づいて、出力信号を右にシフトする。

- 制約を確認する: すべてのフリップフロップについて、セットアップ時間およびホールド時間の要件を満たしているか確認する。

- 遷移を確認する: グリッチがないことを確認する。グリッチとは、誤って論理をトリガーする可能性のある一時的な意図しないパルスである。

🔄 実際の例:シンプルなカウンタ

これらの概念がどのように連携するかを視覚化するために、シンプルな3ビットバイナリカウンタを検討する。この回路は、クロック信号がパルスするたびに値を1増加させる。

Q0、Q1、Q2の3つの出力ラインを想像する。Q0はクロックサイクルごとにトグルする。Q1はQ0が1サイクルを完了するたびにトグルする。Q2はQ1が1サイクルを完了するたびにトグルする。

ステップバイステップの解析

- クロック (CLK):50%のデューティサイクルを持つ方形波。

- Q0 (最下位ビット):クロックの毎回の立ち上がりエッジで状態を変更する。周波数はクロックの半分である。

- Q1:Q0の毎回の立ち上がりエッジで状態を変更する。周波数はQ0の半分である。

- Q2 (最上位ビット):Q1の毎回の立ち上がりエッジで状態を変更する。周波数はQ1の半分である。

これを描画すると、リップル効果に気づくだろう。Q0が最初に変化する。Q1はQ0が安定するのを待ってから変化する。Q2はQ1を待つ。この遅延の蓄積こそがリップルカウンタの本質である。

| クロックサイクル | Q2 | Q1 | Q0 | 10進数値 |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ 避けたい一般的な誤り

経験豊富なエンジニアでさえ、タイミング図を読む際に誤りを犯すことがあります。これらの一般的な誤りに注意してください。

- ギャリッチの無視:時間スケールが大きすぎると、短いパルスは見えないことがあります。しかし、ラッチをトリガーする可能性があります。常に狭いパルスの有無を確認してください。

- デューティーサイクルの誤解:実際にはスケューしているにもかかわらず、クロックが50%であると仮定してしまう。これによりタイミングウィンドウに影響が出ます。

- ハイZ状態の見落とし:バスシステムでは、ラインが浮遊状態になります。タイミング図は、ラインが駆動されているときと浮遊しているときを明確に示す必要があります。

- セットアップとホールドの混同:セットアップはエッジの前、ホールドはエッジの後です。これらを混同すると、誤った回路設計につながります。

- グランド参照の無視:すべての電圧レベルは、同じグランドに対して測定しなければなりません。グランドが異なる場合、論理レベルは無効になります。

🛠 ドキュメント作成のベストプラクティス

ドキュメント作成やデバッグ用にタイミング図を作成する際は、明確さを確保するために以下のガイドラインに従ってください。

- 一貫したスケーリングを使用する:時間軸が線形であることを確認してください。明示的にマークされていない限り、一部の区間を圧縮して別の区間を伸ばしてはいけません。

- 重要なエッジを揃える:クロックエッジがデータサンプリングポイントと完全に一致していることを確認してください。

- ギャップにラベルを付ける: 遅延がある場合は、具体的な時間値(例:tpd = 5ns)でラベル付けしてください。

- 色分け:異なる信号タイプには明確な色を使用してください(例:クロックは青、データは赤、制御は緑)。

- アクティブ状態を明示する:信号がアクティブハイかアクティブローかを明確に示してください(例:/CSのように名前にバーを付ける)。

🧩 メタスタビリティとタイミングハザード

高度なタイミング図は、しばしばメタスタビリティと呼ばれる現象を明らかにします。これは、信号がフリップフロップのセットアップ/ホールドウィンドウちょうどタイミングで変化するときに発生します。出力は0または1にすぐに安定せず、中間の電圧レベルに留まります。

稀ではありますが、メタスタビリティはシステムクラッシュを引き起こすことがあります。タイミング図は、非同期入力と同期クロックの関係を示すことで、これを予測するのに役立ちます。外部信号がクロックエッジに近すぎるように変化すると、図ではデータが誤ったタイミングでしきい値を越える様子が示されます。

🔍 実データの分析

ロジックアナライザによって生成されたタイミング図を見ると、線はほとんど完璧な矩形ではありません。現実の信号には以下のような特徴があります:

- リズタイム:ローからハイに移行するのにかかる時間です。ほとんど瞬時に起こることはありません。

- フォールタイム:ハイからローに移行するのにかかる時間です。

- オーバーシュート/アンダーシュート:電源レールを超える電圧スパイクです。

- ジッター:信号エッジのタイミングのばらつきです。

これらの不完全さを理解することは、高速設計において極めて重要です。完璧な矩形波は理論的な理想であり、実際の信号はデジタル論理を表すアナログ波形です。

📚 主なポイントの要約

タイミング図はデジタルタイミングの言語です。抽象的な論理を物理的な現実に変換します。これらを習得することで、次の能力が得られます:

- システム内のデータの流れを可視化する。

- 信号が衝突する可能性のある場所を特定する。

- データが信頼性を持ってキャプチャされることを保証する。

- 回路の最大動作速度を計算する。

まずはシンプルな論理ゲートで練習を始めましょう。入力を描き、遅延を計算し、出力をプロットします。進んでいくにつれて、複雑なバスやクロックドメインへと移行してください。忍耐と練習を重ねれば、これらの図の読み取りは自然な感覚になります。

🚀 今後のステップ

信号整合性やクロック配布ネットワークの微細な点をさらに探求し続けてください。システムが高速化するにつれて、タイミングマージンは小さくなります。正確にタイミング図を読む能力は、デジタルハードウェアを扱うすべてのエンジニアにとって、今後も中心的なスキルとして残り続けます。