デジタル回路の挙動を理解するには、論理ゲートを知っているだけでは不十分です。信号が時間とともにどのように変化するかを把握する必要があります。タイミング図は、この時間的分析のための視覚的言語を提供します。これらは、クロックや特定のイベントに対して、さまざまな信号の状態をマッピングします。コンピュータサイエンスの学生にとって、この概念を習得することは、信頼性の高いシステムを設計するために不可欠です。

このガイドでは、タイミング図に関わるメカニズム、読み取り技術、および重要なパラメータについて解説します。基本的な信号遷移から、複雑なセットアップ時間およびホールド時間の違反まで、すべてをカバーします。この概要を終える頃には、デジタル相互作用を分析するためのしっかりとした基礎が身につくでしょう。

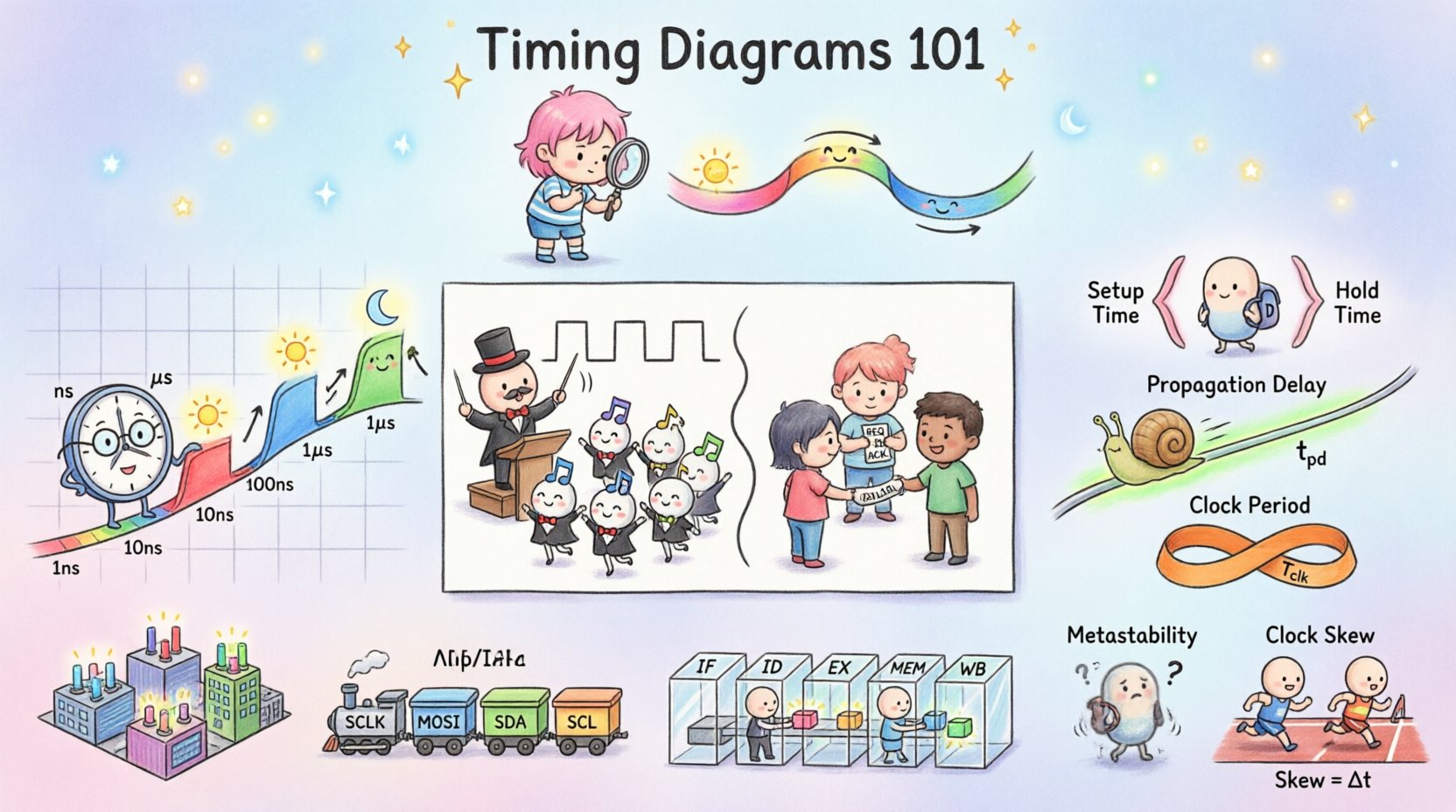

タイミング図とは何か? ⏱️

タイミング図は、時間の経過とともに2つ以上の信号の関係を図式化したものです。これはデジタルイベントのタイムラインとして機能します。各信号は水平線としてプロットされます。縦方向の位置は論理レベルまたは状態を示します。横軸は時間の経過を表します。

これらの図は、デジタルシステムが正しく動作しているかを検証するために不可欠です。エンジニアがデータがレジスタ、バス、メモリをどのように通過するかを予測するのを助けます。それらがなければ、ハードウェアの問題をデバッグすることはほぼ不可能になります。これらは、抽象的な論理と物理的な現実の間の橋渡しを行います。

デジタル信号の核心的な要素 📡

図の解説に入る前に、信号そのものについて理解しておく必要があります。デジタルシステムは、電圧レベルを使って2進データを表現します。これらのレベルは常に静的であるとは限りません。状態の間を遷移します。

- 論理高 (1):通常、電源レールに近い電圧を表します。

- 論理低 (0):通常、グラウンドに近い電圧を表します。

- エッジ:高と低の間の遷移点です。リジングエッジは低から高へ、フェイリングエッジは高から低へと移行します。

- 安定状態:信号が一定の状態を保つ期間です。

- ノイズマージン:信号が誤解される前に許容できる余裕です。

タイミング図はこれらの遷移を可視化します。信号がいつ変化するか、そしてその状態にどれだけの期間滞在するかを正確に示します。この正確さは、データの整合性を確保するために不可欠です。

時間軸の理解 ⏳

横軸は、あらゆるタイミング図の骨格です。時間の進行を表します。デジタル設計では、この軸がしばしばクロック信号と同期されます。クロックはシステムの鼓動のような役割を果たします。

時間軸上の単位は、回路の速度に応じて異なります。一般的な単位には以下があります:

- 秒 (s):非常に遅いシステムに使用されます。

- ミリ秒 (ms):10^-3秒。

- マイクロ秒 (µs):10^-6秒。

- ナノ秒 (ns):10^-9秒。現代のプロセッサの標準です。

- ピコ秒(ps):10^-12秒。高速インターフェースに必須。

図を読む際にはスケール目盛りを探してください。これらは各サイクルの持続時間を示しています。これにより、伝播遅延の計算や、信号が必要な時間枠内に到達することを確認できます。

同期型と非同期型システム 🔄

デジタルシステムは、タイミングの扱い方によって一般的に2つのカテゴリに分かれます。正確な図を描くためには、この違いを理解することが鍵となります。

1. 同期型システム

同期型設計では、すべての状態変化がグローバルなクロック信号に対して発生します。タイミング図には周期的なクロック波形が表示されます。すべてのフリップフロップがこのクロックのアクティブエッジで更新されます。

- 利点:予測可能な動作。検証が容易。

- 課題:クロックスキーが、信号が異なるタイミングで到着する場合に問題を引き起こす可能性がある。

- 図の特徴:垂直線はしばしばクロックエッジと一致し、キャプチャの瞬間を示す。

2. 非同期型システム

非同期型設計はグローバルクロックに依存しません。代わりに、ハンドシェイキングプロトコルやローカル信号を使って動作をトリガーします。ここでのタイミング図はより不規則です。

- 利点:場合によっては消費電力が低い。平均応答時間が速い。

- 課題:検証が複雑。ラス条件に陥りやすい。

- 図の特徴:信号が固定されたリズムなしに互いにトリガーし合う。

重要なタイミングパラメータ 📏

特定の測定値がタイミング図の信頼性を定義します。これらのパラメータが、回路がすべての条件下で正しく動作するかどうかを決定します。

| パラメータ | 説明 | 重要性 |

|---|---|---|

| 伝播遅延 | 信号が入力から出力まで伝わるまでの時間。 | 最大動作周波数を制限する。 |

| セットアップ時間 | データの時間はクロックエッジの前に安定している必要があります。 | ラッチが正しい値をキャプチャすることを保証します。 |

| ホールド時間 | データの時間はクロックエッジの後に安定したまま維持される必要があります。 | ラッチが変化する値を読み取るのを防ぎます。 |

| クロック周期 | クロック信号の1つの完全なサイクルの期間。 | システムの速度を定義します。 |

| デューティーサイクル | 信号がハイ状態になる期間の割合。 | 消費電力とタイミングマージンに影響します。 |

詳細解説:セットアップ時間とホールド時間

セットアップ時間とホールド時間は順序回路における最も重要な制約です。違反すると、出力が定義されないメタスタビリティ状態に入ることがあります。

セットアップ時間の違反: データがクロックエッジに非常に近いタイミングで変化したときに発生します。回路がキャプチャの準備に十分な時間を確保できず、結果として論理エラーが生じることが多いです。

ホールド時間の違反: データがクロックエッジの直後にあまりにも早く変化したときに発生します。回路はまだ前の値をキャプチャしようとしています。これは物理的なレイアウトに依存するため、修正が難しいことがよくあります。

図の読み方と解析 🔍

タイミング図の解析には体系的なアプローチが必要です。視覚的なデータを正確に解釈するには、以下のステップに従ってください。

- クロックを特定する:周期的な信号を見つけます。これがあなたの基準点です。

- アクティブエッジを特定する:システムが立ち上がりエッジまたは立ち下がりエッジでトリガーするかを確認します。

- 信号の依存関係を追跡する:1つの信号の変化が他の信号にどのように影響するかを確認します。

- ギャップの有無を確認する:ノイズや意図しない遷移である可能性のある短いパルスを探します。

- 制約の確認:すべてのレジスタに対してセットアップ時間とホールド時間が守られていることを確認します。

簡単なデータ転送のシナリオを検討してください。CPUがデータをメモリに送信します。タイミング図では、アドレスラインが最初に安定し、その後データラインが安定し、最後に書き込み信号が表示されます。各ステップは特定の時間窓内に発生しなければなりません。

一般的な違反とその影響 ⚠️

経験豊富なエンジニアですらタイミングの問題に直面することがあります。一般的な違反を理解することで、トラブルシューティングが容易になります。

1. メタスタビリティ

信号がセットアップ時間またはホールド時間の制約を違反すると、フリップフロップの出力は安定する前に振動する可能性があります。この状態をメタスタビリティと呼びます。この状態はシステム内を伝播し、予測不能な動作を引き起こすことがあります。このリスクを軽減するために、同期回路がしばしば使用されます。

2. スキュー

クロック信号が異なる部品に異なるタイミングで到着する場合、クロックスキューが発生します。これにより、実効的なタイミングマージンが減少します。ポジティブスキューはセットアップ時間は長くなりますが、ホールド時間は短くなります。ネガティブスキューは逆の効果があります。

3. レースコンディション

出力がイベントの順序に依存する場合、レースコンディションが発生します。2つの信号が同時に変化する場合、処理の順序が最終状態を決定します。タイミング図はこれらの順序を可視化し、レースを防ぐのに役立ちます。

コンピュータアーキテクチャにおける応用 🖥️

タイミング図は理論的なツールにとどまらず、実際のアーキテクチャ設計で広く使用されています。

メモリインターフェース

DRAMとSRAMには厳格なタイミング要件があります。メモリコントローラーは読み取りや書き込みを行う前に特定の遅延を待たなければなりません。タイミング図はコマンドバスのシーケンスを定義します。これにより、データにアクセスする前にメモリバンクが準備完了していることを保証します。

バスプロトコル

I2C、SPI、UARTなどのプロトコルは通信にタイミングに依存しています。SPIのクロック線はデータ転送を同期します。UARTではタイミングはボーレートに基づいています。受信側はビット期間の正確な中央でデータ線をサンプリングする必要があります。タイミング図はスタートビット、データビット、ストップビットの整合性を示します。

パイプラインステージ

現代のCPUはパイプライン化により、複数の命令を同時に実行します。各ステージは1クロックサイクル以内に完了しなければなりません。タイミング図はフェッチ、デコード、実行、書き戻しの各ステージを通過するデータの流れをマッピングします。これにより、あるステージが他のステージを待つスタールを特定するのに役立ちます。

ドキュメント作成のベストプラクティス 📝

明確なタイミング図を作成することで、他のエンジニアが設計を理解できるようになります。効果的なドキュメント作成のためには以下のガイドラインに従いましょう。

- 一貫したスケールを使用する:ドキュメント全体にわたって時間軸が均一になるようにしてください。

- 明確にラベルを付ける:すべての信号に名前を付けてください。「シグナル1」のような汎用的なラベルは避けてください。

- 制約を強調する:セットアップ時間とホールド時間のウィンドウを示すために、カッコや陰影領域を使用してください。

- 関連する信号をグループ化する:制御信号はまとめて、データ信号もまとめて配置してください。

- 注釈を含める:複雑な遷移や特殊な動作を説明する注釈を追加してください。

高度な考慮事項 🔬

システムが高速化するにつれて、タイミング解析はより複雑になります。いくつかの要因が難易度をさらに高めます。

1. 電源ノイズ

電圧の変動は論理ゲートのしきい値レベルをずらす可能性があります。これにより伝播遅延が実質的に変化します。タイミング図は最悪の電圧状況を考慮しなければなりません。

2. 温度変化

電子部品は異なる温度で異なる挙動を示します。高温では抵抗と遅延が増加します。低温は静電容量に影響を与える可能性があります。設計者は、動作温度範囲全体にわたってタイミングを検証しなければなりません。

3. シグナルインテグリティ

基板上の長いトレースは送信線として機能します。反射やクロストークにより信号が歪む可能性があります。高速リンクに対しては、タイミング図にアイダイアグラムや信号品質指標を含めるべきです。

タイミング解析に関する結論 🎯

タイミング図はデジタル論理をナビゲートするための地図です。抽象的な2進状態を物理的な時間イベントに変換します。コンピュータサイエンスの学生にとって、これらの図を読み書きする能力は基本的な専門能力です。

クロックサイクル、伝播遅延、セットアップ制約を理解することで、堅牢で効率的なシステムを設計できます。信号の流れを視覚化する能力は、ハードウェア設計における高コストな誤りを防ぎます。技術が進化しても、原則は同じです。時間は変化しない変数です。

基本に注目してください。既存の図を読み込む練習をしましょう。新しい回路を構築するたびに自分自身で図を描いてください。この訓練はあなたの技術的キャリアにおいて大きな助けになります。