デジタルシステムは、正しく動作するためには正確な同期に依存しています。正確なタイミングがなければ、データの破損、システムのクラッシュ、安全上の失敗は避けられません。タイミング図は、信号が時間とともにどのように変化するかを視覚的に表現したもので、クロックサイクル、データの有効性、制御信号の関係を明確に示します。このガイドでは、さまざまな分野におけるタイミング図の重要な役割を検討し、一般的な課題に対する実用的な事例と技術的解決策を詳述します。

🔍 基本の理解

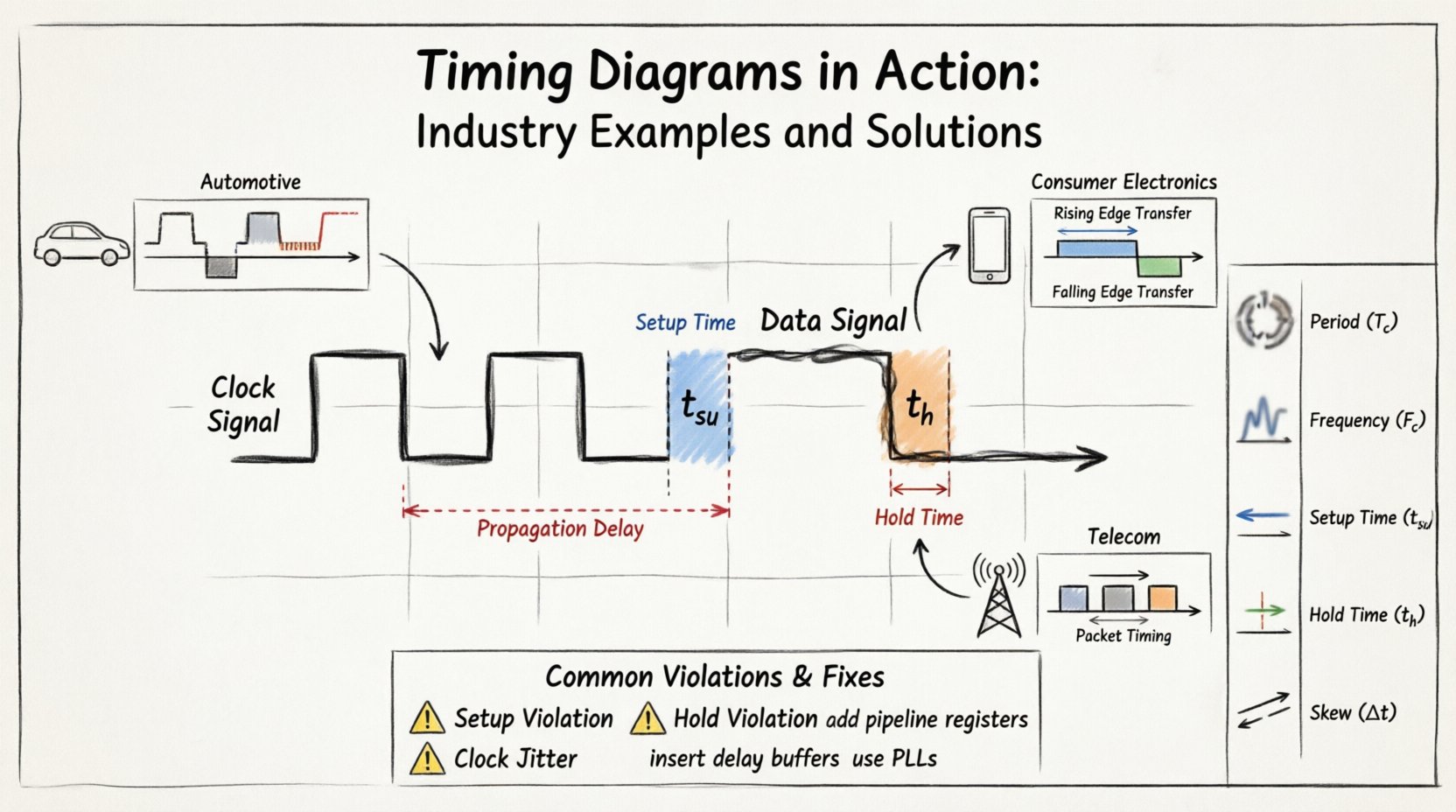

特定の応用に取り組む前に、タイミング図の核心的な構成要素を理解することが不可欠です。これらの図は、基準クロックに対して信号の挙動をマッピングしています。それらは単なる図面ではなく、ハードウェアの挙動を規定する数学的制約です。

- 信号エッジ: 低から高への遷移(リジングエッジ)または高から低への遷移(フェルージングエッジ)が、順序論理における状態変化を引き起こします。

- クロック周期: 同じ極性の連続するエッジ間の期間は、論理回路が安定するための可用時間として定義されます。

- 伝播遅延: シグナルが論理ゲートを経由して入力ピンから出力ピンまで到達するまでの時間。

- セットアップ時間とホールド時間: クロックエッジの前後でデータが安定していることを保証する重要な制約。

これらのパラメータが違反されると、回路はメタスタビリティ状態に入り、予測不能な挙動を示す可能性があります。エンジニアはタイミング図を用いて、設計の物理的実装がこれらの論理的要件を満たしているかを検証します。

🚗 自動車電子機器:安全に重要なタイミング

自動車産業は、最高レベルの信頼性を要求します。車両には、CAN(コントローラー・エリア・ネットワーク)、LIN(ローカル・インターコネクト・ネットワーク)、FlexRayなどのバスを介して通信する数十個の電子制御ユニット(ECU)が搭載されています。ここでのタイミング解析は、単なる速度の問題ではなく、決定論的かつ安全な動作を意味します。

1. CANバスの仲裁

CANバスは、単一の線路上で複数のノードが通信できるようにします。CAN仲裁のタイミング図は、バス競合時に優先順位がどのように決定されるかを明らかにします。

- ドミナント vs. レセッシブ: ロジックレベルは電圧状態で表現されます。ドミナントビット(0)はレセッシブビット(1)を上書きします。

- 同期: ノードは同期セグメントを用いてフレームビットの開始に同期します。

- サンプリングポイント: データはビット時間の特定のパーセンテージでサンプリングされ、ノイズを避けるために用いられます。

サンプリングポイントがエッジに近すぎると、ノイズがビットエラーを引き起こす可能性があります。逆に遅すぎると、データが安定していない可能性があります。タイミング図はエンジニアがサンプリングポイントを適切に設定するのを助け、通常はビット時間の約80%の位置に設定されます。

2. センサ統合におけるADCのサンプリング

現代の車両は、レーダー、ライダー、カメラなどの複数のセンサーを使用して環境を認識します。アナログ・デジタル変換器(ADC)は、アリアシングを避けるために、正確な間隔で信号をサンプリングしなければなりません。

- クロックジッター: クロックエッジのタイミングの変動が、デジタル化された信号にノイズを導入します。

- レイテンシ: センサー入力から処理済みデータの出力までの時間は、リアルタイム制御のために最小限に抑える必要があります。

- インタリーブ:複数のADCはしばしば並列で動作する。タイミング図により、それらの位相が一致していることを保証し、データのギャップを防ぐ。

📱 消費電子機器:高速インターフェース

消費系デバイスは性能と電力効率を最優先する。DDRメモリやディスプレイリンクなどのインターフェースは、電力消費を増やさずに高い帯域幅を達成するために、厳密なタイミングウィンドウを必要とする。

1. DDRメモリインターフェース

ダブルデータレート(DDR)メモリは、クロックの立ち上がりエッジと立ち下がりエッジの両方でデータを転送する。これにより、有効データレートは2倍になるが、データ安定性のための時間ウィンドウは半分になる。

| パラメータ | 定義 | 違反時の影響 |

|---|---|---|

| セットアップ時間 | クロックエッジの前にデータが安定している必要がある時間 | データ転送の損失、システムの停止 |

| ホールド時間 | クロックエッジの後にデータが安定したまま維持される必要がある時間 | データの破損、ビット反転 |

| クロックスキュー | クロックが異なるチップに到着する時間の差 | タイミングマージンの低下、不安定性 |

| デューティーサイクル | 高電位時間と全体の周期との比率 | 性能の不均衡、ジッターの増加 |

DDR4およびDDR5では、コマンドバスおよびアドレスバスがデータバスよりも低い周波数で動作することが多い。タイミング図は、データと共に送信されるソース同期ストローブ信号(DQS)を考慮し、有効なウィンドウを示す必要がある。

2. ディスプレイインターフェース(MIPI DSI)

モバイルデバイスは、プロセッサと画面を接続するためにMIPIディスプレイシリアルインターフェース(DSI)を使用する。このインターフェースは高速差動ランを用いる。

- LPコマンドモード:コマンド送信のための低消費電力モード。ウェイクアップシーケンスに厳密なタイミングに依存する。

- HSデータモード:クロック回復がデータストリーム上で行われる高速伝送。

- ターンアラウンドタイム:同じランで送信モードから受信モードに切り替えるために必要な時間。

これらのタイミング図の不整合は、画面のアーティファクトやちらつき、あるいは映像出力の完全な喪失を引き起こす。

📡 通信技術:レイテンシと帯域幅

通信技術において、タイミングはレイテンシと同義である。パケットの配送時間や分散ネットワーク間の同期は、5Gや高頻度取引などのサービスにとって不可欠である。

1. PCIeシグナリング

パーサル・コンポーネント・インターコネクト・エクスプレス(PCIe)規格は、高速なコンポーネントを接続するために広く使用されている。これは埋め込みクロックまたはソース同期クロックを備えたシリアルチャネルを使用する。

- イコライゼーション:信号の整合性は距離とともに低下する。タイミング図は、イコライゼーションフィルタが損失を補償する方法を示している。

- リンクトレーニング:リンク速度とチャネル幅を確立するための、時刻を指定した状態の連続。

- フロー制御:クレジットベースのフロー制御のためのタイミングウィンドウは、バッファオーバーフローを防ぐ。

2. イーサネットPHY

標準的なイーサネットは共有クロックまたはクロック回復に依存している。ギガビットイーサネット以降は、クロック回復に十分な遷移を確保するために8b/10b符号化を使用する。

- アイドル期間:同期を維持するためにデータが送信されない、定義されたタイミングウィンドウ。

- フレーム開始区切り:パケットの開始を示す特定のビットパターンであり、正確な検出タイミングが求められる。

- パケット間隔:ハードウェアがリセットできるように、パケット間に必須の遅延を設ける。

⚠️ 一般的なタイミング違反とその解決策

慎重な設計を行っても、タイミング違反は発生する。根本原因を特定するには、信号が期待と異なる点を把握するためにタイミング図を分析する必要がある。

1. ライズ時間違反

データがクロックエッジによってキャプチャされるのに遅れて到着したときに発生する。

- 原因:論理の深さが過剰、長い配線遅延、またはクロックスキー。

- 解決策:

- パイプラインレジスタを挿入して、長いパスを分割する。

- ゲート数を減らすために論理合成を最適化する。

- クロック周波数を調整して、より多くの時間を確保する。

2. ホールド時間違反

クロックエッジの後にデータが速く変化する場合に発生し、キャプチャされた値を上書きする。

- 原因:短いパス遅延、キャプチャクロックが遅れて到着するクロックスキー。

- 解決策:

- データパスに遅延バッファを挿入する。

- パスのバランスを取るためにリタイム技術を使用する。

- クロック配布ネットワークのスキーが最小限になるようにする。

3. クロックスキーとジッター

スキーは、異なるレジスタにおけるクロック信号の到着時間の差を指す。ジッターは、クロックエッジの短期的な変動を指す。

- 影響:データに利用可能な有効なタイミングマージンを減少させる。

- 解決策:

- 低ジッタークロックジェネレータを使用する。

- 等長のトレースを備えたバランスの取れたクロックツリーを設計する。

- クロック信号をクリーニングするために位相ロックループ(PLL)を実装する。

✅ 実装のためのベストプラクティス

堅牢なタイミングを達成するには、設計ライフサイクル全体にわたって体系的なアプローチが必要である。ドキュメント化と検証は、回路そのものと同じくらい重要である。

1. 時間制約を早期に定義する

実装フェーズまでタイミング要件を定義するのを待ってはならない。設計仕様書にクロック周波数、入力遅延、出力遅延を記録する。これにより、すべての関係者がシステムの境界を理解できるようになる。

2. 静的タイミング解析を使用する

静的タイミング解析(STA)ツールは、すべての入力組み合わせをシミュレートせずに、最悪ケースの遅延パスを計算する。この方法は効率的で、すべての可能な状態をカバーし、タイミング違反が見逃されることがないことを保証する。

3. シミュレーションで検証する

STAは強力であるが、動的シミュレーションは特定の条件下での信号動作を可視化できる。特に非同期論理や複雑なステートマシンを含む重要なパスを検証するために、シミュレーションを使用する。

4. 物理設計の考慮事項

チップまたは基板の物理的レイアウトは、タイミングに直接影響を与える。

- 配線長:長い配線は、より多くの静電容量と抵抗を導入し、遅延を増加させる。

- クロストーク:隣接する信号がノイズを誘発し、誤った遷移を引き起こす可能性がある。

- 電源ノイズ: 電圧の低下はゲートのスイッチング速度を遅くする可能性があります。

🛠️ 実際の状況におけるトラブルシューティング

システムがタイミングを満たさない場合、構造化されたデバッグプロセスが必要です。以下のステップは、タイミング問題を解決する論理的なアプローチを示しています。

- ステップ1:パスを特定する。障害を引き起こしている特定のレジスタ間パスを特定してください。最も負のスラックを持つタイミングレポートを確認してください。

- ステップ2:波形を分析する。タイミング図ビューアを使用して、実際の信号遷移を確認してください。期待される値と比較してください。

- ステップ3:クロックを確認する。クロック信号の品質を確認してください。ジッター、ドットサイクル歪み、またはギャップがないか確認してください。

- ステップ4:制約を確認する。設計ファイル内の制約が、ハードウェアの物理的現実と一致していることを確認してください。

- ステップ5:反復する。論理回路またはレイアウトに変更を加え、その後タイミング解析を再実行してください。

📊 タイミングパラメータの概要

迅速な参照を支援するために、業界で使用される主要なタイミングパラメータの概要を以下に示します。

| パラメータ | 記号 | 通常の単位 | 説明 |

|---|---|---|---|

| 周期 | Tc | ns | 連続するクロックエッジ間の時間 |

| 周波数 | Fc | Hz | 周期の逆数 |

| セットアップ時間 | tsu | ns | クロックエッジの前にデータの安定性が必要 |

| ホールド時間 | th | ns | クロックエッジの後にデータの安定性が必要 |

| プロパゲーション遅延 | tpd | ns | 信号が論理を通過するまでの時間 |

| スキュー | Δt | ps | クロック到着時間の差 |

🔄 非同期設計の管理

すべてのシステムが単一のクロックで動作するわけではない。非同期設計では、データが異なるクロックドメイン間を渡る。これにより、フリップフロップが定義されない状態に入ってしまうメタスタビリティのリスクが生じる。

- 同期チェーン:信号が使用される前に安定するように、マルチステージ同期器(通常は2つのフリップフロップ)を使用する。

- ハンドシェイクプロトコル:データを送信する前に受信側が準備できていることを保証するために、リクエスト・アックノリッジメカニズムを実装する。

- FIFOバッファ:生産者と消費者の速度を分離するために、先入れ先出しのメモリ構造を使用する。

非同期設計のタイミング図は、2つの独立したクロックの関係を示す。重要なのは、受信クロックがデータをサンプリングする前に、データパスに安定する十分な時間が確保されていることである。

🌟 最後の考察

タイミング図はデジタルシステム検証の基盤である。抽象的な論理と物理的な現実の間のギャップを埋める。セットアップ時間、ホールド時間、クロックスキュー、ジッターの微細な点を理解することで、エンジニアは堅牢で、効率的かつ信頼性の高いシステムを設計できる。

自動車の安全システム、消費者向け機器、通信インフラのいずれにおいても、原則は同じである。タイミングの正確さが性能の正確さにつながる。継続的なモニタリングとベストプラクティスの遵守により、設計がライフサイクル全体にわたり機能し続けることが保証される。技術の進歩と速度の向上に伴い、詳細なタイミング解析の重要性はさらに高まるだろう。

設計品質を向上させたいチームにとって、正確なタイミング図と検証フローに時間を投資することは不可欠です。これによりリスクが低減され、デバッグコストが低下し、最終製品が仕様を満たしていることを確実にします。適切なツールと手法があれば、タイミングの課題は障害ではなく、管理可能な制約となります。