デジタルシステムは正確な同期に依存して正しく動作します。信号が間違ったタイミングで到着すると、論理的な障害が発生し、予測不能な動作を引き起こします。これらの問題を分析し修正する方法を理解することは、デジタル論理、コンピュータ工学、または電子工学を学ぶすべての人にとって不可欠です。このガイドでは、順序回路およびデータ伝送で遭遇するタイミング問題を特定し解決するための基本的な概念と実践的なステップをカバーしています。

クロック信号とエッジの理解 ⏱️

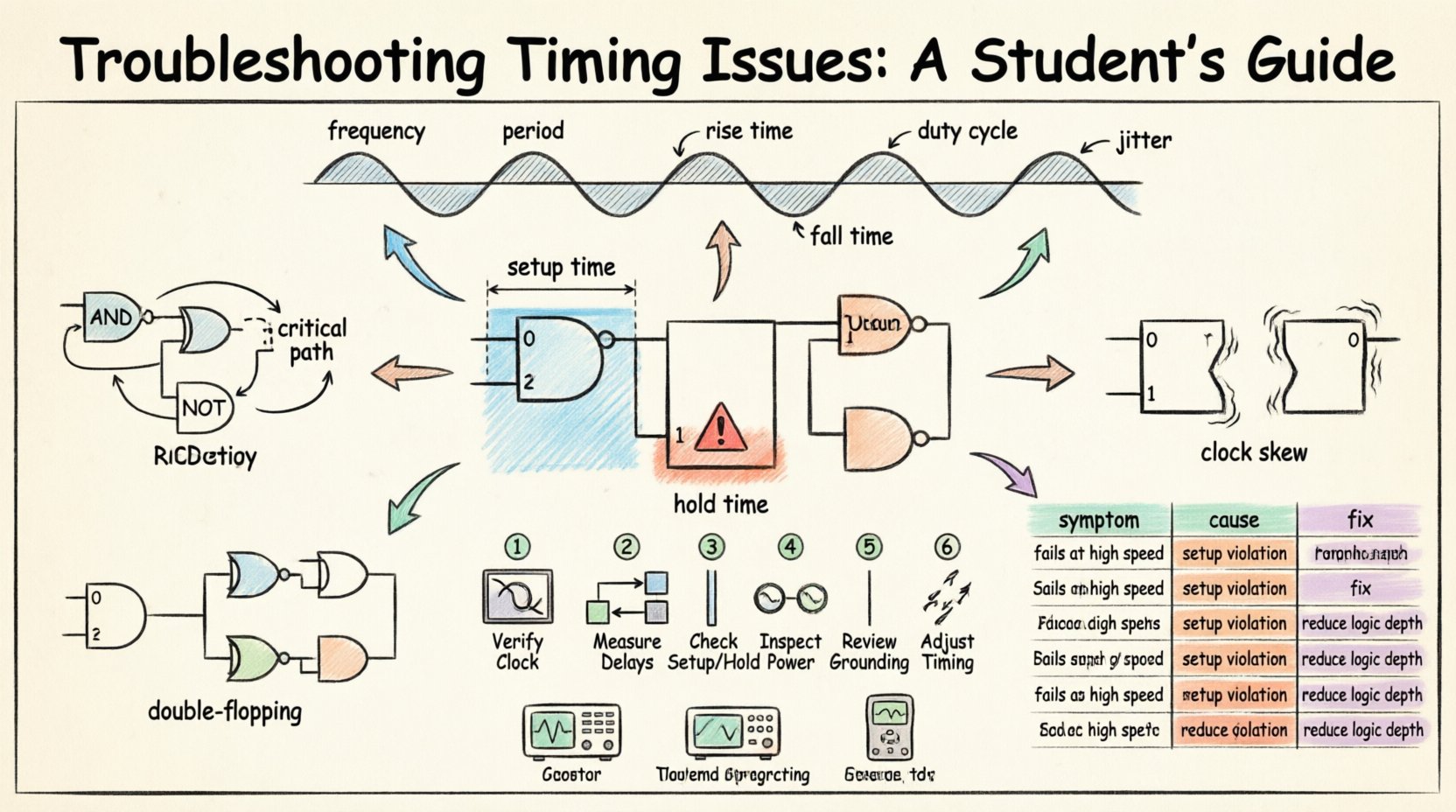

ほとんどのデジタル設計の中心にはクロック信号があります。この周期的な波形が、データがサンプリングされるタイミングと状態変化が発生するタイミングを決定します。トラブルシューティングは、この基本的な信号の整合性を確認することから始まることが多いです。

- 周波数と周期: クロック周波数は動作速度を決定します。周期は1サイクルの時間長です。回路が100 MHzのクロックを必要とする場合、周期は10ナノ秒です。ここでの偏差は、すべての下流論理回路に影響を与えます。

- 立ち上がり時間と立ち下がり時間: 完全なサイクリック波は理論上のものである。実際の信号には有限の立ち上がり時間と立ち下がり時間が存在する。遷移が遅すぎると、信号が定義されていない電圧領域に長く滞在し、複数回のトグルや論理エラーを引き起こす可能性がある。

- デューティーサイクル: これは信号がハイ状態にある時間と全体の周期との比率である。50%のデューティーサイクルが標準であるが、一部の設計では非対称なサイクルが必要となる。偏差は、セットアップやホールド要件のタイミングマージンを歪める可能性がある。

回路を検査する際は、オシロスコープまたはロジックアナライザを使用してクロック波形を確認する。ノイズスパイク、リング、または過度のジッターがないか確認する。ジッターとは、クロックエッジが時間的に理想的な位置からどれだけずれているかを指す。高いジッターは、データが安定するための有効なタイミングマージンを減少させる。

セットアップ時間およびホールド時間の違反 ⚠️

これらは順序論理設計で最も一般的に遭遇するタイミング違反である。フリップフロップやラッチは、データがクロックエッジに対して安定している必要があるタイミングについて、特定の要件を持っている。

セットアップ時間

セットアップ時間とは、クロックエッジの前にデータが安定している必要がある最小時間である。データがクロックエッジに近すぎるように変化すると、フリップフロップが正しい値をキャプチャできなくなる可能性がある。

- 制約: フリップフロップに供給する組み合わせ論理の伝播遅延は、クロック周期からセットアップ時間を引いた値よりも小さくなければならない。

- 症状: システムは低周波数では動作するが、速度が上がると失敗する可能性がある。出力ではランダムなビットエラーが頻繁に発生する。

- 修正方法: レジスタ間の論理深さを減らす、クロック周期を延長する、またはより高速な部品を使用する。

ホールド時間

ホールド時間とは、クロックエッジの後にデータが安定したまま維持される必要がある最小時間である。データがクロックエッジの後に早すぎるように変化すると、フリップフロップがキャプチャした値を失う可能性がある。

- 制約: 組み合わせ論理の伝播遅延は、宛先のフリップフロップのホールド時間よりも大きくなければならない。

- 症状: ホールド違反は周波数にかかわらず頻繁に発生する。これは遅延が周期に対して相対的なものではなく、絶対的なものであるためである。

- 修正方法: データパスに遅延バッファを追加して信号を遅くする、または論理を再設計して遅延を短くする。

これら2つの違いを明確にすることは非常に重要である。セットアップ違反は周波数に依存するが、ホールド違反はパスに依存する。ホールド違反をクロックを遅くすることで修正しようとするという一般的な誤りがあるが、これは効果がなく、むしろ状況を悪化させる可能性がある。

伝播遅延とパス解析 📉

信号は瞬時に伝播しない。すべての配線、ゲート、コンポーネントに遅延が生じる。データが適切なタイミングで到着することを保証するためには、これらの遅延を分析することが不可欠である。

- 組み合わせ論理遅延: これは、AND、OR、NOTなどのゲートを通過する信号にかかる時間である。長いゲートチェーンは顕著なレイテンシを生じる。

- インターコネクト遅延: 実際の基板上では、配線に静電容量と抵抗がある。長いトレースはより大きな遅延をもたらす。これはしばしばRCネットワークとしてモデル化される。

- ピン対ピン遅延: コンポーネント内のクロック入力からデータ出力までの時間。これは通常、データシートに記載されている。

故障診断の際は、クリティカルパスを明確にせよ。これは2つの順序要素の間で最も遅延の大きいパスである。もしクリティカルパスがクロック周期を超えると、設計は失敗する。これを特定するには、すべての可能なパスの遅延の合計を計算し、最大値を特定すればよい。

クロックスケイブとジッター 📶

クロック源が完璧であっても、信号は異なるコンポーネントに異なるタイミングで到達する可能性がある。この現象はスケイブと呼ばれる。

- クロックスケイブ: クロック信号が異なるフリップフロップに到達するまでの距離が異なる場合に発生する。ポジティブスケイブはキャプチャクロックを遅らせるため、セットアップ時間は緩和されるがホールド時間は厳しくなる。ネガティブスケイブはセットアップ時間を厳しくするが、ホールド時間を緩和する。

- クロックジッター: クロックエッジタイミングの短期的な変動。ジッターはデータセットアップに利用可能なタイミング予算を減少させる。

- ドリフト: 温度や電源の変動によって、時間とともにクロック周波数がゆっくりと変化すること。

スケイブは、複雑な設計ではクロックツリー合成によって管理されることが多い。学生のプロジェクトでは、通常、クロックトレースを均等に配線し、短くすることで最小限に抑える。スケイブが疑われる場合は、回路内の複数のポイントで同時にクロックを測定せよ。

メタスタビリティと非同期入力 🌀

データがクロックエッジと同時に変化する場合、フリップフロップはメタスタビリティ状態に入る。すぐに0または1に安定せず、中間の電圧レベルに留まる。

- リスク: メタスタビリティはシステム内を伝播し、再現が難しい論理エラーを引き起こす可能性がある。

- 非同期信号: 外部スイッチや通信ポートからの入力は、内部クロックと一致しないことが多い。これらは同期化されなければならない。

- ダブルフロッピング: メタスタビリティを解消するための一般的な手法は、信号を直列に2つのフリップフロップに通すことである。最初のフリップフロップがメタスタビリティ状態をキャプチャし、次のサイクル中に2番目のフリップフロップがそれを解消する。

常に非同期入力を潜在的なメタスタビリティ源として扱え。厳密なタイミングを要する論理回路に直接接続してはならない。異なるクロックドメイン間での安全なデータ転送を確保するために、同期回路を使用せよ。

ステップバイステップのトラブルシューティングワークフロー 🛠️

タイミング問題が発生した際は、原因を特定するために構造的なアプローチをとれ。ランダムな変更では結果は得にくい。

- クロックを確認する: 周波数、ドット率、振幅を確認してください。信号が安定しており、クリーンであることを確認してください。

- 遅延を測定する:ロジックアナライザを使用して入力および出力波形をキャプチャしてください。パスの実際の伝播遅延を測定します。

- セットアップおよびホールドを確認する: 測定された遅延に基づいて、パスがセットアップおよびホールド制約を満たしているかどうかを計算します。

- 電源を点検する: 電圧降下はゲートの動作を遅くする可能性があります。電源が安定しており、十分な電流を供給していることを確認してください。

- グランドを確認する: 不適切なグランド接続は、タイミングエラーを模倣するノイズを引き起こす可能性があります。グランドループや共有リターンパスがないか確認してください。

- タイミングを調整する: デザインが柔軟な場合、クロック周波数を調整するか、バッファを追加してパスをバランスさせる。

このプロセス中、ドキュメント作成が重要です。波形と測定値を記録してください。このデータは、期待される動作と実際の性能を比較するのに役立ちます。

一般的なエラー参照表 📊

この表を、特定の症状を診断するための迅速な参照としてご利用ください。

| 観察された症状 | 可能性のある原因 | 推奨される対処法 |

|---|---|---|

| システムが高速で動作時に失敗する | セットアップ時間違反 | 論理の深さを減らすか、クロック周期を延長する |

| システムが低速で動作時に失敗する | ホールド時間違反 | データパスに遅延バッファを追加する |

| ランダムなビット反転 | 信号ノイズまたはジッター | シールドと電源安定性を確認する |

| 出力が停止またはリセットされる | メタスタビリティ | 同期器チェーンを実装する |

| 一貫性のない動作 | クロックスキュー | クロックトレースの長さをバランスさせる |

| まったく出力がない | クロックが有効になっていない | クロック配布と有効信号を確認する |

ツールと計測機器 📏

シミュレーションツールは有用ですが、実物の検証には特定のハードウェアが必要な場合が多いです。これらの機器を正しく使う方法を理解することは、トラブルシューティングのスキルセットの一部です。

- オシロスコープ:電圧レベルや信号の形状を確認するのに不可欠です。回路に負荷をかけないために高インピーダンスプローブを使用してください。

- ロジックアナライザー:デジタル信号に適しています。時間経過に伴う論理状態(0または1)を記録できます。特定のパターンでトリガをかけ、エラーを特定できます。

- 周波数カウンター:オシロスコープが利用できない場合、クロック源の正確な周波数を確認するために使用します。

プローブが適切に補償されていることを確認してください。補償されていないプローブは信号の形状を歪め、立ち上がり時間や遅延に関する誤った結論を導くことがあります。

信号整合性に関する最終的な考慮事項 🔒

タイミングの問題は、しばしば広範な信号整合性の問題の兆候です。回路が高速化するにつれて、基板の物理的特性がより重要になります。

- クロストーク:隣接する配線上の信号は互いに干渉する可能性があります。高速ラインを感度の高いラインから分離してください。

- インピーダンス整合:トレースのインピーダンスがドライバーやレシーバーと一致しない場合、反射が発生します。これらの反射はタイミング遅延のように見えることがあります。

- 熱的影響:部品が加熱すると、その電気的特性が変化します。これにより伝播遅延が変化し、負荷下でのタイミングの失敗を引き起こすことがあります。

タイミング設計には包括的な視点が必要です。論理ゲートだけの話ではなく、信号が伝わる物理的な媒体についても考える必要があります。これらの原則に従うことで、学生はさまざまな条件下でも信頼性の高い堅牢なシステムを構築できます。

実機を使った定期的な練習は、これらの概念を内面化するのに役立ちます。理論は枠組みを提供しますが、実践的なデバッグによって、複雑なタイミング問題を効率的に解決するための直感が育ちます。