Systemy cyfrowe opierają się na dokładnej synchronizacji, aby poprawnie działać. Gdy sygnały przychodzą w złym momencie, występują błędy logiki, co prowadzi do niestabilnego działania. Zrozumienie, jak analizować i naprawiać te problemy, jest niezbędne dla każdego, kto uczy się logiki cyfrowej, inżynierii komputerowej lub elektroniki. Ten przewodnik obejmuje podstawowe koncepcje i praktyczne kroki umożliwiające wykrywanie i rozwiązywanie problemów z czasem występujących w obwodach sekwencyjnych i transmisji danych.

Zrozumienie sygnałów zegarowych i ich krawędzi ⏱️

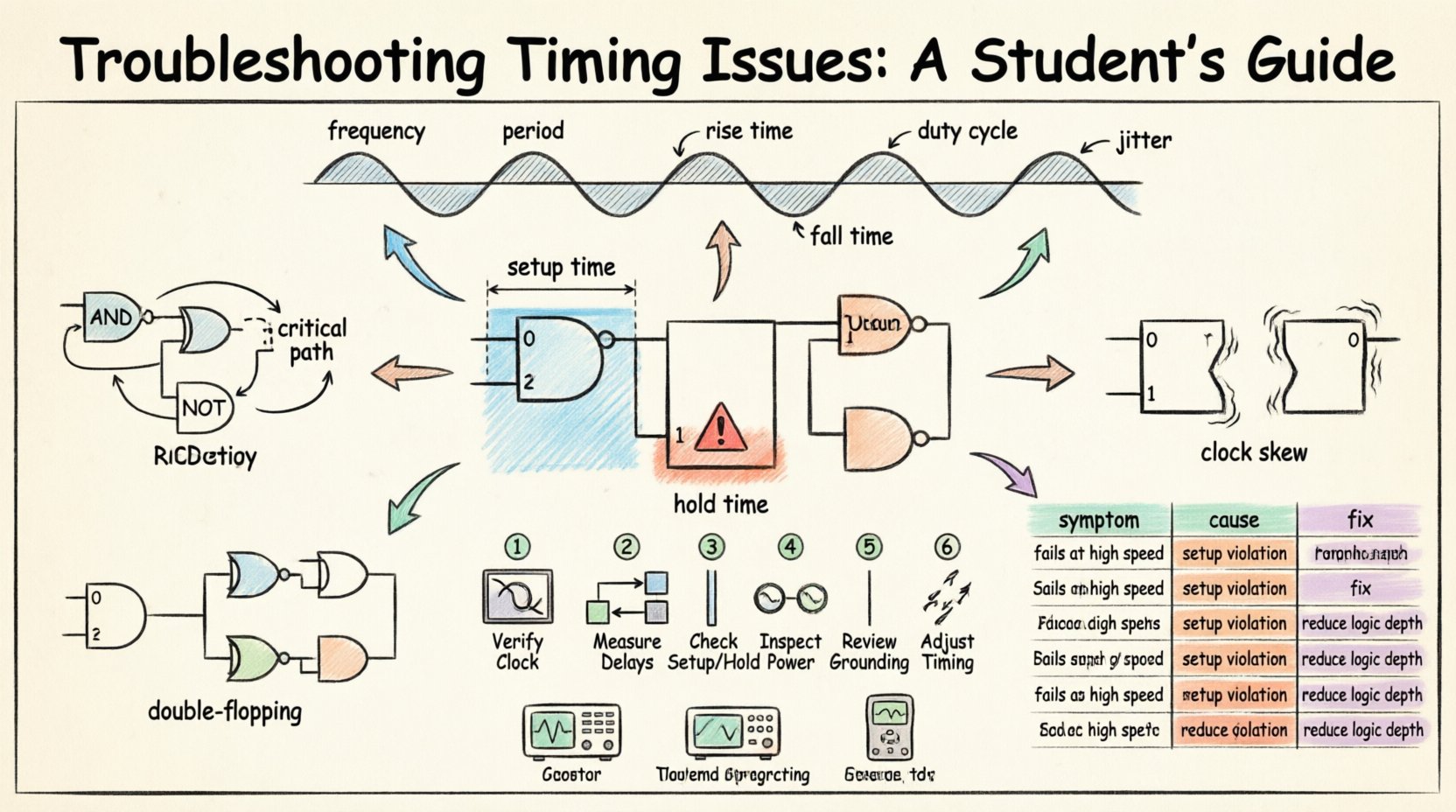

W centrum większości projektów cyfrowych znajduje się sygnał zegarowy. Ten sygnał okresowy określa, kiedy dane są próbkowane, a kiedy zachodzą zmiany stanu. Rozwiązywanie problemów często zaczyna się od weryfikacji integralności tego podstawowego sygnału.

- Częstotliwość i okres: Częstotliwość zegara określa szybkość działania. Okres to czas trwania jednego pełnego cyklu. Jeśli obwód wymaga zegara 100 MHz, okres wynosi 10 nanosekund. Każda odchyłka tutaj wpływa na całą logikę znajdującą się poniżej.

- Czas narastania i spadania: Idealny sygnał prostokątny jest teoretyczny. Sygnały rzeczywiste mają skończone czasy narastania i spadania. Jeśli przejście jest zbyt powolne, sygnał może długo przebywać w nieokreślonej strefie napięcia, co prowadzi do wielokrotnych przełączeń lub błędów logiki.

- Współczynnik wypełnienia: Jest to stosunek czasu, przez który sygnał jest wysoki, do całkowitego okresu. Standardowy współczynnik wypełnienia to 50%, ale niektóre projekty wymagają cykli niesymetrycznych. Odchylenia mogą zakłócić marginesy czasowe wymagane dla ustawienia lub utrzymania danych.

Podczas inspekcji obwodu użyj oscyloskopu lub analizatora logicznego, aby zobaczyć kształt sygnału zegarowego. Szukaj szumów, drgań lub nadmiernego drgań czasowych (jitter). Jitter oznacza odchylenie krawędzi zegara od jej idealnego położenia w czasie. Duży jitter zmniejsza efektywny margines czasowy dostępny do ustabilizowania danych.

Naruszenia czasu ustawienia i utrzymania ⚠️

To najbardziej typowe naruszenia czasowe pojawiające się w projektowaniu logiki sekwencyjnej. Flip-flopy i latch-e mają określone wymagania dotyczące tego, kiedy dane muszą być stabilne względem krawędzi zegara.

Czas ustawienia

Czas ustawienia to minimalny czas przed krawędzią zegara, przez który dane muszą być stabilne. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, flip-flop może nie przechwycić poprawnej wartości.

- Ograniczenie: Opóźnienie propagacji logiki kombinacyjnej zasilającej flip-flop musi być mniejsze niż okres zegara pomniejszony o czas ustawienia.

- Objaw: System może działać przy niższych częstotliwościach, ale zawodzić przy zwiększaniu prędkości. Na wyjściu często pojawiają się przypadkowe błędy bitów.

- Rozwiązanie: Zmniejsz głębię logiki pomiędzy rejestratorami, zwiększ okres zegara lub użyj szybszych komponentów.

Czas utrzymania

Czas utrzymania to minimalny czas po krawędzi zegara, przez który dane muszą pozostać stabilne. Jeśli dane zmieniają się zbyt szybko po krawędzi zegara, flip-flop może stracić przechwyconą wartość.

- Ograniczenie: Opóźnienie propagacji logiki kombinacyjnej musi być większe niż czas utrzymania docelowego flip-flopu.

- Objaw: Naruszenia czasu utrzymania często występują niezależnie od częstotliwości. Wynika to z faktu, że opóźnienie jest bezwzględne, a nie względne do okresu.

- Rozwiązanie: Dodaj buforzy opóźniające do ścieżki danych, aby spowolnić sygnał, lub przeprojektuj logikę w celu zmniejszenia opóźnienia.

Kluczowe jest rozróżnienie między tymi dwoma. Naruszenia ustawienia są zależne od częstotliwości, a naruszenia utrzymania są zależne od ścieżki. Powszechnym błędem jest próba naprawy naruszenia utrzymania przez spowolnienie zegara; nie zadziała to i może pogorszyć sytuację.

Opóźnienia propagacji i analiza ścieżek 📉

Sygnały nie poruszają się natychmiastowo. Każdy przewód, bramka i element wprowadza opóźnienie. Analiza tych opóźnień jest kluczowa, aby zapewnić, że dane przyjdą w odpowiednim czasie.

- Opóźnienie logiki kombinacyjnej: Jest to czas potrzebny na przejście sygnału przez bramki takie jak AND, OR i NOT. Długie łańcuchy bramek powodują istotne opóźnienia.

- Opóźnienie połączeń: Na fizycznej płycie przewody mają pojemność i opór. Dłuższe ścieżki wprowadzają większe opóźnienia. Często modeluje się je jako sieć RC.

- Opóźnienie pin do pin: Czas od wejścia zegara do wyjścia danych w elemencie. Zazwyczaj jest on podany w dokumentacji technicznej.

Podczas rozwiązywania problemów zaznacz krytyczną ścieżkę. Jest to najdłuższa ścieżka opóźnień między dwoma elementami sekwencyjnymi. Jeśli krytyczna ścieżka przekracza okres zegara, projekt nie zadziała. Aby ją znaleźć, oblicz sumę opóźnień dla wszystkich możliwych ścieżek i zidentyfikuj maksimum.

Zesunięcie zegara i drgania zegara 📶

Nawet jeśli źródło zegara jest idealne, sygnał może dotrzeć do różnych elementów w różnych momentach. Ten zjawisko nazywa się zesunięciem zegara.

- Zesunięcie zegara: Zdarza się, gdy sygnał zegara pokonuje różne odległości, aby dotrzeć do różnych przerzutników. Zesunięcie dodatnie opóźnia zegar przechwytywania, łagodząc czas ustawienia, ale ściślej ograniczając czas utrzymania. Zesunięcie ujemne ściślej ogranicza czas ustawienia, ale łagodząc czas utrzymania.

- Drgania zegara: Krótkoterminowe zmiany w czasie krawędzi zegara. Drgania zmniejszają czas dostępny do ustawienia danych.

- Zmiany: Powolne zmiany częstotliwości zegara w czasie spowodowane zmianami temperatury lub fluktuacjami napięcia zasilania.

Zesunięcie często zarządzane jest przez syntezę drzewa zegara w złożonych projektach. W projektach studenckich zwykle minimalizuje się je poprzez równomierne routowanie ścieżek zegara i ich skracanie. Jeśli podejrzewa się zesunięcie, należy zmierzyć zegar w wielu punktach obwodu jednocześnie.

Metastabilność i wejścia asynchroniczne 🌀

Gdy dane zmieniają się w tym samym czasie co krawędź zegara, przerzutnik wchodzi w stan metastabilności. Nie ustala się natychmiast na 0 ani 1, lecz wisi na poziomie napięcia pośrednim.

- Ryzyko:Metastabilność może się rozprzestrzeniać przez system, powodując błędy logiczne, które trudno odtworzyć.

- Sygnały asynchroniczne: Wejścia z zewnętrznych przycisków lub portów komunikacyjnych często nie są zsynchronizowane z wewnętrznym zegarem. Muszą one zostać zsynchronizowane.

- Podwójne przerzucanie: Powszechną techniką rozwiązywania metastabilności jest przepuszczenie sygnału przez dwa przerzutniki połączone szeregowo. Pierwszy zapisuje stan metastabilny, a drugi rozwiązuje go w kolejnym cyklu.

Zawsze traktuj wejścia asynchroniczne jako potencjalne źródła metastabilności. Nie podłączaj ich bezpośrednio do logiki wymagającej ścisłego czasu. Używaj obwodów synchronizujących, aby zapewnić bezpieczny przepływ danych między różnymi domenami zegarowymi.

Krok po kroku proces rozwiązywania problemów 🛠️

Gdy pojawia się problem z czasem, postępuj zgodnie z zaznaczonym podejściem, aby wyizolować przyczynę. Losowe zmiany raczej nie dadzą rezultatu.

- Sprawdź zegar: Sprawdź częstotliwość, cykl roboczy i amplitudę. Upewnij się, że sygnał jest stabilny i czysty.

- Pomiar opóźnień:Użyj analizatora logicznego do zapisania przebiegów wejściowych i wyjściowych. Zmierz rzeczywiste opóźnienie propagacji drogi.

- Sprawdź czas ustalania i czas utrzymania:Oblicz, czy droga spełnia ograniczenia czasu ustalania i czasu utrzymania na podstawie zmierzonych opóźnień.

- Sprawdź zasilanie:Spadki napięcia mogą spowolnić bramki. Upewnij się, że zasilacz jest stabilny i dostarcza wystarczający prąd.

- Przejrzyj uziemienie:Złe uziemienie może wprowadzać szum, który przypomina błędy czasowe. Sprawdź obecność pętli uziemienia i wspólnych ścieżek powrotu.

- Dostosuj czas:Jeśli projekt jest elastyczny, dostosuj częstotliwość zegara lub dodaj bufor do wyrównania drogi.

Dokumentacja jest kluczowa w tym procesie. Zapisz przebiegi i pomiary. Dane te pomagają porównać oczekiwane zachowanie z rzeczywistą wydajnością.

Tabela odniesienia błędów najczęściej występujących 📊

Użyj tej tabeli jako szybki punkt odniesienia do diagnozowania konkretnych objawów.

| Obserwowany objaw | Prawdopodobna przyczyna | Zalecana czynność |

|---|---|---|

| System zawodzi przy wysokiej prędkości | Naruszenie czasu ustalania | Zmniejsz głębię logiki lub zwiększ okres zegara |

| System zawodzi przy niskiej prędkości | Naruszenie czasu utrzymania | Dodaj bufor opóźniający do ścieżki danych |

| Losowe zmiany bitów | Szum sygnału lub drgania | Sprawdź ekranowanie i stabilność zasilania |

| Wyjście zawiesza się lub resetuje | Metastabilność | Zaimplementuj łańcuchy synchronizujące |

| Niespójne zachowanie | Zachwianie zegara | Zrównoważ długości ścieżek zegarowych |

| Zaden wyjście wcale | Zegar nie jest włączony | Sprawdź dystrybucję zegara i sygnały włączające |

Narzędzia i przyrządy pomiarowe 📏

Choć narzędzia symulacyjne są przydatne, weryfikacja fizyczna często wymaga specjalistycznego sprzętu. Zrozumienie sposobu poprawnego używania tych przyrządów stanowi część zestawu umiejętności rozwiązywania problemów.

- Oscyloskop:Niezbędny do obserwacji poziomów napięcia i kształtu sygnału. Używaj sond wysokiego oporu, aby uniknąć obciążenia obwodu.

- Analizator logiczny:Lepszy do sygnałów cyfrowych. Zapisuje stan logiczny (0 lub 1) w czasie. Może być ustawiony na wykrywanie określonych wzorców w celu izolacji błędów.

- Licznik częstotliwości: Używany do weryfikacji dokładnej częstotliwości źródła zegara, gdy oscyloskop jest niedostępny.

Upewnij się, że sondy są odpowiednio skompensowane. Nieskompensowana sonda może zniekształcać kształt sygnału, co prowadzi do błędnych wniosków dotyczących czasów narastania i opóźnień.

Ostateczne rozważania dotyczące integralności sygnału 🔒

Problemy z czasem są często objawami szerszych problemów z integralnością sygnału. Im szybsze stają się obwody, tym większe znaczenie mają właściwości fizyczne płytki.

- Zjawisko zakłóceń wzajemnych:Sygnały na sąsiednich przewodach mogą wzajemnie się zakłócać. Zachowaj odstępy między liniami wysokiej prędkości a liniami wrażliwymi.

- Dopasowanie impedancji: Jeśli impedancja ścieżki nie odpowiada impedancji źródła lub odbiornika, powstają odbicia. Te odbicia mogą wyglądać jak opóźnienia czasowe.

- Wpływ temperatury: W miarę nagrzewania się elementów ich charakterystyki elektryczne ulegają zmianie. Może to zmienić opóźnienia propagacji i prowadzić do awarii czasowych pod obciążeniem.

Projektowanie z uwzględnieniem czasu wymaga kompleksowego podejścia. Nie chodzi tylko o bramki logiczne, ale o fizyczny medium, przez które przechodzą sygnały. Przestrzeganie tych zasad pozwala studentom budować wytrzymałe systemy działające niezawodnie w różnych warunkach.

Regularna praktyka z rzeczywistym sprzętem pomaga internalizować te koncepcje. Teoria dostarcza ramy, ale praktyczne debugowanie buduje intuicję potrzebną do skutecznego rozwiązywania skomplikowanych problemów czasowych.