W nowoczesnym projektowaniu cyfrowym zrozumienie przepływu sygnałów w czasie jest kluczowe dla zapewnienia niezawodności systemu. Systemy asynchroniczne, w których operacje nie są sterowane jednym globalnym zegarem, stawiają przed nami unikalne wyzwania w porównaniu do systemów synchronicznych. Głównym narzędziem służącym do wizualizacji i debugowania tych skomplikowanych interakcji jest diagram czasowy. Niniejszy przewodnik zapewnia szczegółowe omówienie sposobu tworzenia, odczytywania i analizowania diagramów czasowych w środowiskach asynchronicznych.

Charakter projektowania asynchronicznego 🌐

Systemy asynchroniczne działają bez centralnego sygnału zegarowego sterującego każdym przejściem stanu. Zamiast tego zdarzenia są wyzwalane zakończeniem poprzednich operacji lub przyjściem danych. Ten podejście oferuje korzyści takie jak zmniejszone zużycie energii i wyższy potencjalny poziom wydajności w określonych kontekstach. Jednak wprowadza złożoność w zakresie synchronizacji sygnałów i weryfikacji czasu.

Gdy inżynierowie analizują te systemy, muszą uwzględnić zmienne opóźnienia, czasy propagacji oraz brak uniwersalnego punktu odniesienia. Diagramy czasowe pełnią rolę języka wizualnego do mapowania tych zdarzeń. Pozwalają zespołom zobaczyć dokładną relację między przejściami sygnałów w czasie.

Anatomia diagramu czasowego 📐

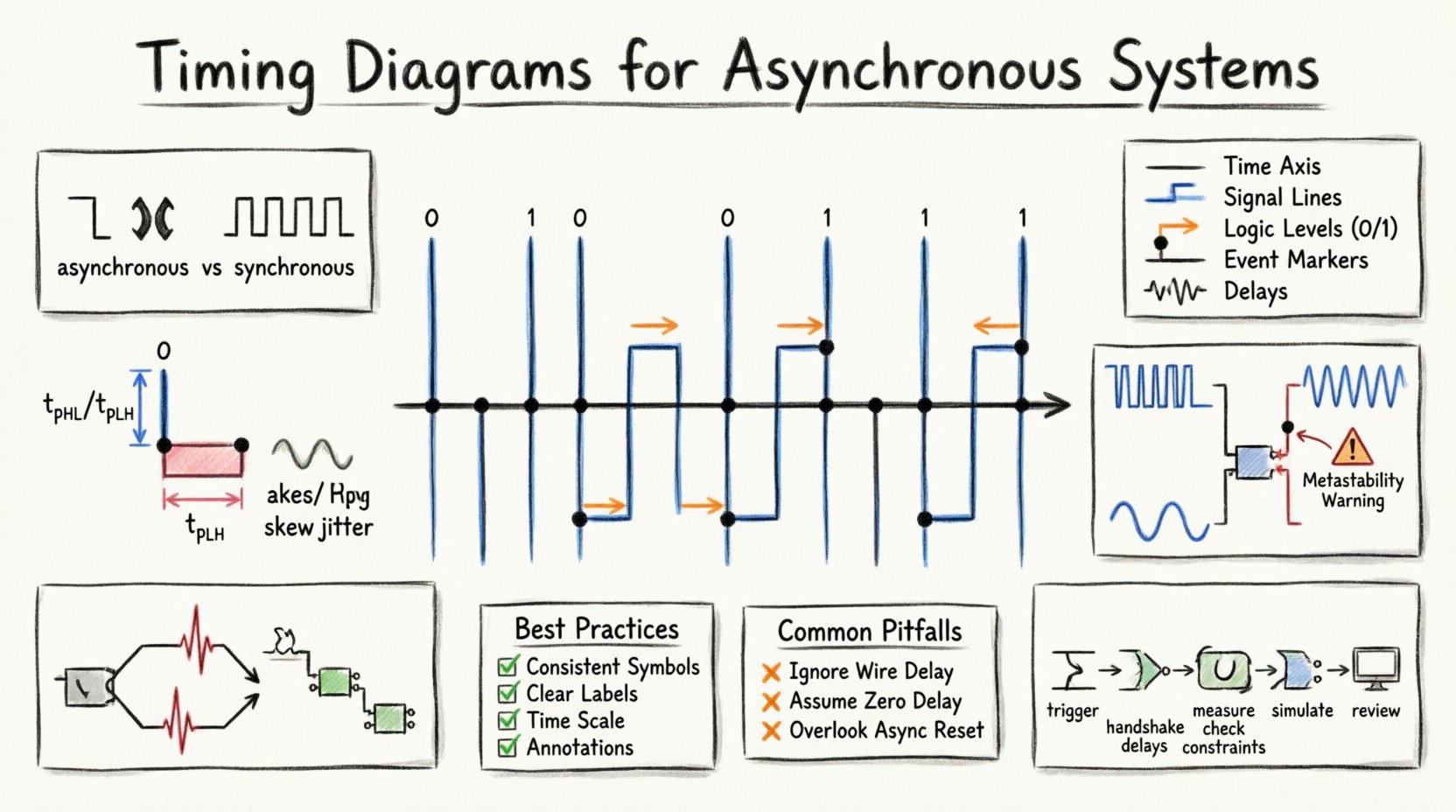

Diagram czasowy to graficzne przedstawienie zachowania sygnałów. Na osi poziomej odkłada się czas, a na osi pionowej stany sygnałów. Aby skutecznie analizować system asynchroniczny, należy zrozumieć podstawowe elementy, z których się te diagramy składają.

- Oś czasu: Reprezentuje postęp czasu. W analizie asynchronicznej często odnosi się on do konkretnego wyzwalacza zdarzenia, a nie do cyklu zegara.

- Linie sygnałów: Poziome linie reprezentujące poszczególne przewody lub sieci. Każda linia śledzi poziom logiczny (Wysoki, Niski lub Nieznany) konkretnego sygnału.

- Poziomy logiczne: Zazwyczaj oznaczane jako “0” (Niski/Ziemia) i “1” (Wysoki/Napięcie zasilania). Przejścia między tymi stanami są centrum analizy.

0Zazwyczaj oznaczane jako “0” (Niski/Ziemia) i “1” (Wysoki/Napięcie zasilania). Przejścia między tymi stanami są centrum analizy.1Zazwyczaj oznaczane jako “0” (Niski/Ziemia) i “1” (Wysoki/Napięcie zasilania). Przejścia między tymi stanami są centrum analizy. - Znaczniki zdarzeń: Pionowe linie lub adnotacje wskazujące konkretne zdarzenia, takie jak zmiana stanu sygnału wymiany danych.

- Opóźnienia: Wizualne przerwy między zmianą wejścia a odpowiadającą zmianą wyjścia, reprezentujące opóźnienie propagacji.

W przeciwieństwie do diagramów synchronicznych, które opierają się na linii siatki reprezentującej krawędzie zegara, diagramy asynchroniczne opierają się na granicach zdarzeń. Wymaga to bardziej dokładnej interpretacji odstępów między przejściami.

Krytyczne parametry czasowe ⚙️

Aby przeanalizować integralność systemu asynchronicznego, należy zmierzyć konkretne parametry czasowe i porównać je z wymaganiami projektowymi. Te parametry definiują okno, w którym sygnał musi być stabilny, aby został poprawnie zinterpretowany przez odbiorcę.

Opóźnienie propagacji

Opóźnienie propagacji to czas potrzebny sygnałowi na przejście od wejścia komponentu do jego wyjścia. W logice asynchronicznej to opóźnienie jest głównym źródłem niepewności. Odchylenia w produkcji, temperaturze i napięciu mogą zmieniać to opóźnienie.

- tpHL: Czas potrzebny sygnałowi na przejście z wysokiego na niski poziom.

- tpLH: Czas potrzebny sygnałowi na przejście z niskiego na wysoki poziom.

- tpd: Ogólny opóźnienie propagacji, często obliczane jako średnia tpHL i tpLH.

Podczas analizy diagramu czasowego szukaj poziomego odstępu między krawędzią wejściową a odpowiadającą krawędzią wyjściową. Ten odstęp to opóźnienie propagacji.

Czas ustawienia i czas utrzymania

Nawet w systemach asynchronicznych, przerzutniki i blokady często wymagają określonych okien stabilności. Czas ustawienia to czas przed zdarzeniem wyzwalającym, przez który dane muszą być stabilne. Czas utrzymania to czas po zdarzeniu wyzwalającym, przez który dane muszą pozostać stabilne.

Jeśli te okna są naruszone, system może wejść w stan metastabilności, w którym wyjście nie jest ani wysokie, ani niskie, ale poziom niewykazany napięcia. Diagramy czasowe pomagają wizualizować te naruszenia, pokazując, czy dane zmieniają się zbyt blisko krawędzi sterującej.

Zeskok i drgania

- S zeskok: Różnica w czasie przybycia tej samej sygnału w dwóch różnych punktach obwodu.

- Drgania: Krótkoterminowe zmiany w czasie sygnału. W systemach asynchronicznych drgania mogą być spowodowane szumem zasilania lub sprzężeniem.

Obsługa przekroczeń domen zegarowych 🔄

Jednym z najczęściej występujących źródeł błędów w systemach mieszanych jest przekroczenie między różnymi domenami zegarowymi. Nawet jeśli system jest głównie asynchroniczny, często zawiera bloki synchroniczne działające z różnymi częstotliwościami. Diagramy czasowe są niezbędne do weryfikacji tych przekroczeń.

Gdy sygnał przechodzi z jednej domeny zegarowej do drugiej, odbiorca może próbować odczytać sygnał w chwili, gdy sygnał się zmienia. Może to prowadzić do metastabilności. Standardowym sposobem na zmniejszenie tego ryzyka jest użycie synchronizatora, zazwyczaj łańcucha przerzutników.

| Parametr | Opis | Wpływ na diagram czasowy |

|---|---|---|

| Czas rozwiązywania metastabilności | Czas potrzebny do zakończenia rozwiązywania przez synchronizator na poprawny poziom logiczny | Pokazuje przedłużony okres stanu nieokreślonego przed ustabilizowaniem sygnału |

| Opóźnienie między domenami | Dodatkowe opóźnienie wprowadzone przez synchronizator | Zwiększa odstęp czasowy między zdarzeniem źródłowym a zdarzeniem docelowym |

| Opóźnienie wymiany potwierdzeń | Czas potrzebny na sygnały potwierdzenia w protokołach asynchronicznych | Tworzy wzorzec tam i z powrotem w czasie sygnału |

Analitycy muszą zapewnić, że diagram czasowy uwzględnia czas rozwiązywania. Jeśli blok poniżej próbuję odczytać sygnał przed rozwiązaniem synchronizatora, występuje uszkodzenie danych.

Identyfikacja i rozwiązywanie warunków wyścigu ⚠️

Warunek wyścigu występuje, gdy zachowanie systemu zależy od względnego czasu zdarzeń, które nie powinny na siebie wpływać. W logice asynchronicznej jest to częsty problem. Diagramy czasowe są głównym narzędziem do wykrywania tych warunków.

Zagrożenia statyczne

Zjawisko zakłócenia statycznego występuje, gdy sygnał powinien pozostawać na stałym poziomie, ale chwilowo zmienia się z powodu opóźnień w ścieżkach. Na przykład, jeśli sygnał logicznie powinien pozostawać na poziomie wysokim, ale zmiana wejścia powoduje krótkie spadnięcie do poziomu niskiego, jest to zakłócenie statyczne-1.

- Wskaźnik wizualny:Cienki szczyt lub impuls na linii sygnału, która powinna być płaska.

- Pierwotna przyczyna:Różne opóźnienia propagacji przez różne bramki logiczne.

Zakłócenia dynamiczne

Zakłócenia dynamiczne dotyczą wielu przejść, gdy oczekiwane jest tylko jedno. Zdarza się to często w złożonych ścieżkach logicznych, gdzie sygnały przechodzą przez różne liczby bramek.

Kroki analizy warunków wyścigu

- Śledź ścieżki:Zidentyfikuj wszystkie ścieżki, które sygnał przebywa od źródła do miejsca docelowego.

- Mierz opóźnienia:Oblicz opóźnienie dla każdej ścieżki przy użyciu diagramu czasowego.

- Porównaj krawędzie:Sprawdź, czy czasy przybycia sygnałów konkurencyjnych nakładają się w sposób powodujący niepewność.

- Zweryfikuj stabilność:Upewnij się, że sygnały sterujące pozostają stabilne w krytycznym oknie przybycia danych.

Jeśli zostanie wykryty warunek wyścigu, projekt może wymagać ponownej strukturyzacji. Powszechne rozwiązania obejmują dodanie buforów w celu wyrównania opóźnień, wstawienie protokołów wymiany zdań lub użycie struktur FIFO asynchronicznych.

Zagadnienia integralności sygnału i szumów 🔌

Diagramy czasowe nie istnieją w próżni. Warstwa fizyczna wprowadza szum, który wpływa na jakość sygnału. Przy analizie systemów asynchronicznych inżynierowie muszą rozróżniać błędy czasowe logiczne od degradacji sygnału fizycznego.

Zakłócenia sygnału

Zakłócenia to krótkotrwałe impulsy, które mogą się rozprzestrzeniać przez obwód. W systemach asynchronicznych zakłócenie może nieprawidłowo wywołać zapis lub przerzutnik. Diagramy czasowe często przedstawiają je jako cienkie szczyty.

- Filtrowanie:Upewnij się, że logika w dalszej części ma wystarczające opóźnienie, aby filtrować te impulsy.

- Szybkość zmiany krawędzi:Pochyłe krawędzie (szybsze czasu narastania/spadania) są bardziej podatne na sprzężenie szumów.

Zjawisko sprzężenia

Zjawisko sprzężenia występuje, gdy sygnał na jednym przewodzie indukuje napięcie na sąsiednim przewodzie. Może to przesunąć czas przybycia sygnału, powodując jego przyjazd wcześniej lub później niż oczekiwano.

W diagramie czasowym zjawisko sprzężenia może się objawiać przesunięciem położenia krawędzi lub dodatkowym szczytem szumu. Aby temu zapobiec, odstępy między sygnałami muszą być uwzględnione w fazie projektowania fizycznego.

Najlepsze praktyki dokumentowania 📝

Jasna dokumentacja zapewnia, że analiza czasowa może zostać odtworzona i zrozumiana przez inżynierów. Dobrze skonstruowany diagram czasowy zawiera określone metadane i adnotacje.

Standardyzacja

- Używaj spójnych symboli dla poziomów logicznych.

- Jasno oznacz wszystkie sygnały ich funkcją.

- Jasno wskaż skalę czasu (np. nanosekundy na działkę).

Adnotacje

Adnotacje tekstowe są kluczowe do wyjaśnienia określonych zachowań. Używaj strzałek, aby wskazać krytyczne przejścia lub potencjalne obszary problemów. Oznacz wartości opóźnień propagacji bezpośrednio na schemacie.

Kontrola wersji

Diagramy czasowe ewoluują wraz z zmianami projektu. Zachowuj numery wersji dla wszystkich schematów, aby upewnić się, że analiza odpowiada aktualnemu stanowi sprzętu. Nie polegaj na pamięci podczas analizy szczegółów czasowych.

Krok po kroku proces analizy 🛠️

Aby skutecznie przeanalizować system asynchroniczny, postępuj zgodnie z zasadą strukturalną. Zapewnia to, że żaden krytyczny parametr czasowy nie zostanie pominięty.

- Zdefiniuj wyzwalacz: Zidentyfikuj zdarzenie, które inicjuje sekwencję. Jest to zazwyczaj punkt początkowy osi czasu.

- Zmapuj wymianę sygnałów: Prześledź sygnały żądania i potwierdzenia. Upewnij się, że następują poprawnemu protokole (np. wymiana czterofazowa lub dwufazowa).

- Mierz opóźnienia: Oblicz całkowite opóźnienie od wyzwalacza do końcowego wyjścia. Podziel je na opóźnienia poszczególnych elementów.

- Sprawdź ograniczenia: Upewnij się, że czas ustalania i czas utrzymania są spełnione dla wszystkich elementów pamięciowych.

- Symuluj zmiany: Przeanalizuj schemat w warunkach najgorszych przypadków, takich jak maksymalna temperatura lub minimalne napięcie.

- Przejrzyj metastabilność: Upewnij się, że prawdopodobieństwo wystąpienia metastabilności zostało zmniejszone do akceptowalnego poziomu za pomocą synchronizatorów.

Powszechne pułapki w analizie czasowej ⚡

Nawet doświadczeni inżynierowie mogą pominąć subtelne problemy. Znajomość powszechnych pułapek pomaga uniknąć kosztownych ponownych projektów.

- Ignorowanie opóźnienia przewodów: Poleganie wyłącznie na opóźnieniu bramki, pomijając rezystancję i pojemność połączeń międzyelementowych.

- Zakładanie zerowego opóźnienia: Traktowanie pętli zwrotnych jako natychmiastowych, co jest fizycznie niemożliwe.

- Pomijanie asynchronicznego zasilania: Nie uwzględnianie czasu sygnałów resetujących w stosunku do sygnałów danych.

- Pomylenie krawędzi i poziomu: Pomylenie zachowań wyzwalanych krawędzią i poziomem podczas interpretacji schematu.

Wnioski dotyczące weryfikacji ✅

Diagramy czasowe są niezastąpione przy weryfikacji systemów asynchronicznych. Dają one konkretną wizualizację abstrakcyjnych zależności czasowych. Przez szczegółową analizę tych diagramów inżynierowie mogą identyfikować warunki wyścigu, weryfikować protokoły wymiany sygnałów i zapewniać integralność sygnałów.

Złożoność projektowania asynchronicznego wymaga precyzji. Każda nanosekunda ma znaczenie. Pełne zrozumienie opóźnień propagacji, czasów ustalania i czasów utrzymania pozwala na tworzenie odpornych systemów. Choć brak globalnego zegara dodaje trudności, wgląd uzyskany dzięki szczegółowej analizie czasowej prowadzi do bardziej efektywnych i niezawodnych projektów.

Kontynuowanie doskonalenia tych umiejętności analizy zapewnia, że systemy będą działać poprawnie w różnych warunkach środowiskowych. Celem jest stabilność i przewidywalność, osiągane poprzez dokładne dokumentowanie i pomiary.

Zaawansowane rozważania 🔬

W aplikacjach o wysokiej wydajności pojawiają się dodatkowe czynniki. Do nich należą gradienty temperatury na芯片ie oraz spadki napięcia podczas zdarzeń przełączania.

- Gradienty temperatury:Sygnały przemieszczające się od gorącego centrum chipa do chłodniejszego krawędzi będą miały różne prędkości. Ta różnica musi zostać odzwierciedlona w analizie czasowej.

- Szum sieci zasilającej:Szum spowodowany jednoczesnym przełączaniem może przesunąć progi logiczne. Diagramy czasowe powinny idealnie zawierać reprezentację stabilności szyn zasilających.

- Zmienne opóźnienie: Niektóre protokoły asynchroniczne pozwalają na zmienne opóźnienie. Diagram czasowy musi pokazywać zakres akceptowalnych opóźnień, a nie tylko jedną wartość.

Za pomocą uwzględnienia tych zaawansowanych rozważań analiza czasowa staje się kompleksowym narzędziem walidacji systemu. Przechodzi ona poza prostą weryfikację do prawdziwej optymalizacji wydajności.

Pamiętaj, że czas nie dotyczy tylko prędkości; chodzi o poprawność. Szybki system, który zawodzi z powodu błędów czasowych, jest mniej przydatny niż wolniejszy system działający niezawodnie. Diagram czasowy to mapa prowadząca do tej niezawodności.