W złożonym świecie inżynierii systemów wbudowanych czas ma znaczenie. Mikrokontroler może działać idealnie w symulacji, ale katastrofalnie zawieść na sprzęcie z powodu kilku nanosekund opóźnienia. To właśnie w tym miejscu diagram czasowy staje się niezastąpionym narzędziem. Te reprezentacje wizualne pokazują zachowanie sygnałów w czasie, dając jasny obraz, jak komponenty oddziałują na siebie w systemie cyfrowym. Niezależnie od tego, czy debugujesz awarię komunikacji, czy projektujesz nowy interfejs peripheralny, zrozumienie, jak czytać i tworzyć diagramy czasowe, jest podstawą.

Ten przewodnik obejmuje podstawowe zasady czasowania sygnałów, od podstawowych definicji po złożone interakcje protokołów. Przeanalizujemy, jak interpretować przebiegi sygnałów, tworzyć dokładne diagramy na podstawie danych pomiarowych oraz identyfikować typowe pułapki prowadzące do niestabilności systemu. Opanowanie tych narzędzi wizualnych pozwala przewidywać zachowanie systemu i weryfikować projekty jeszcze przed ich wyjściem z stołu pomiarowego.

🔍 Zrozumienie podstaw czasowania sygnałów

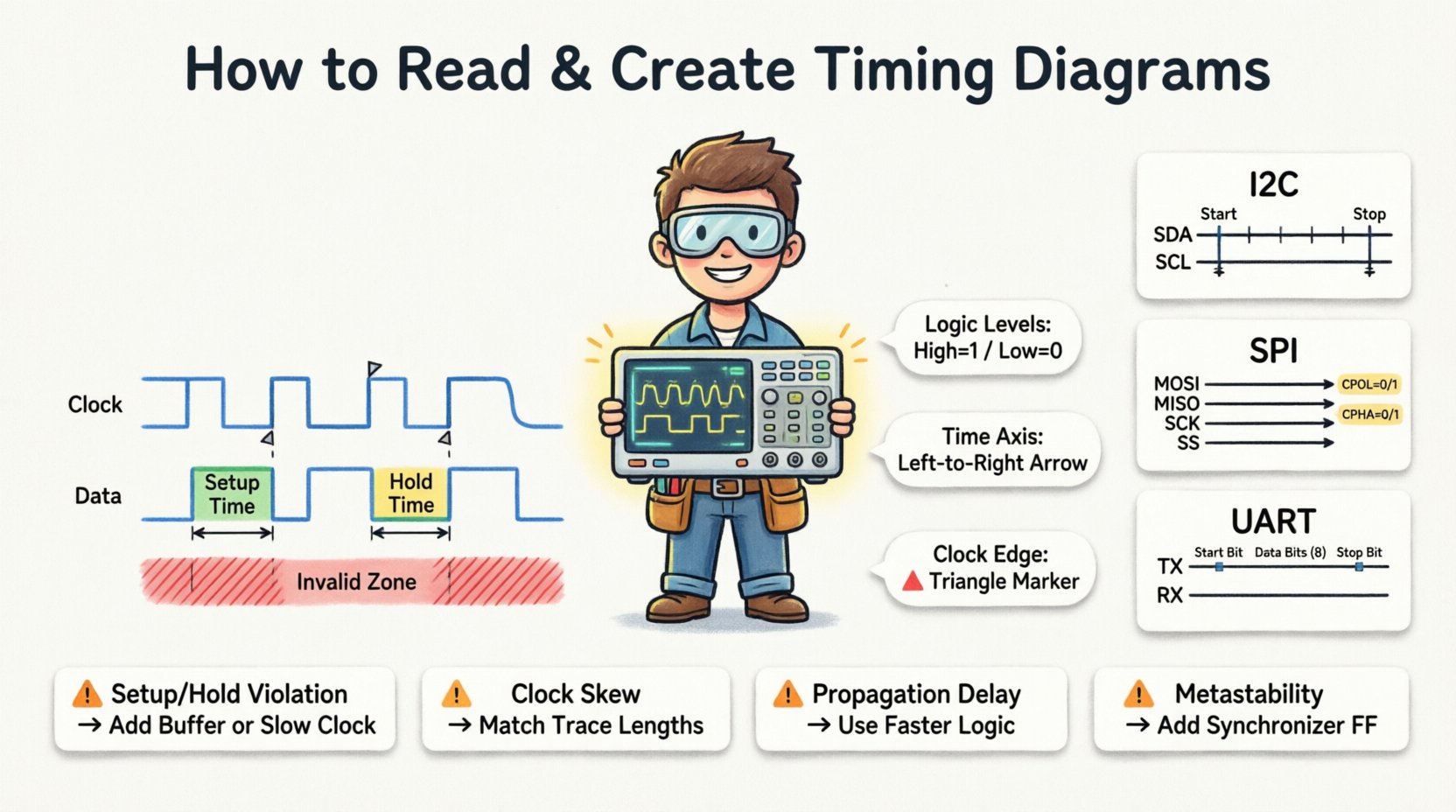

Diagram czasowy to nie tylko rysunek; to reprezentacja matematyczna stanów logicznych względem osi czasu. W systemach wbudowanych zajmujemy się przede wszystkim poziomami logiki cyfrowej, które są dwustanowe: wysoki (1) i niski (0). Złożoność tkwi jednak w przejściach między tymi poziomami.

- Poziomy logiczne:Większość systemów wbudowanych działa na określonych progach napięciowych. Na przykład system 3,3 V definiuje stan wysoki jako wszystko powyżej 2,0 V, a stan niski jako wszystko poniżej 0,8 V.

- Oś czasu:Czas płynie od lewej do prawej. Odstępy poziome reprezentują czas trwania określonych stanów lub opóźnienie między zdarzeniami.

- Ślady sygnałów: Każdy poziomy odcinek reprezentuje konkretny przewód lub sieć. Wiele linii ułożonych pionowo umożliwia porównanie relacji między sygnałami.

Podczas analizy systemu szukasz przyczynowości. Czy sygnał zegara wywołuje zmianę danych? Czy sygnał aktywacji musi być aktywny przed tym, jak dane stają się ważne? Diagramy czasowe odpowiedzają na te pytania wizualnie.

🛠️ Kluczowe elementy diagramu czasowego

Aby poprawnie zinterpretować diagram, musisz rozpoznać standardowe elementy używane do oznaczania zachowania sygnałów. Te komponenty definiują zasady działania sprzętu.

| Element | Opis | Wizualny wskaźnik |

|---|---|---|

| Nazwa sygnału | Identyfikuje konkretny przewód lub sieć | Etykieta tekstowa po lewej stronie |

| Poziom logiczny | Stan wysoki (1) lub niski (0) | Płaska pozioma linia na górze lub dole |

| Krawędź przejścia | Zmiana od wysokiego do niskiego lub odwrotnie | Pionowa linia łącząca poziomy |

| Krawędź zegara | Punkt wyzwalający logikę synchroniczną | Punktowana linia lub znacznik trójkątny |

| Strefa nieprawidłowa | Obszar, w którym nie można odczytać danych | Zacieniony lub kreskowany obszar |

Zrozumienie tych elementów pozwala na rozkładanie złożonych interakcji. Na przykład zacieniony obszar często wskazuje na wymóg czasu ustawienia lub utrzymania, w którym odbiorca nie może wiarygodnie przechwycić danych.

👁️ Jak czytać wykres czasowy krok po kroku

Czytanie wykresu czasowego wymaga systematycznego podejścia. W istocie przekształcasz wzór wizualny w sekwencję zdarzeń. Postępuj zgodnie z tym procesem, aby zapewnić dokładność.

1. Zidentyfikuj źródło zegara

Większość systemów wbudowanych jest synchroniczna, co oznacza, że sygnał zegara określa tempo operacji. Znajdź ślad zegara. Zazwyczaj ma regularną, okresową falę prostokątną.

- Sprawdź częstotliwość. Czy wynosi 1 MHz czy 100 MHz? To decyduje o prędkości całego systemu.

- Zidentyfikuj typ krawędzi. Czy urządzenie aktywuje się na zboczu narastającym (od niskiego do wysokiego) czy spadającym (od wysokiego do niskiego)?

2. Zmapuj okna ważności danych

Dane są ważne tylko w określonych oknach względem zegara. Zwróć uwagę na zależność między krawędzią zegara a linią danych.

- Czas ustawienia: Dane muszą być stabilne przez określony okres przed krawędzią zegara.

- Czas utrzymania: Dane muszą pozostawać stabilne przez określony okres po krawędzią zegara.

Jeśli dane zmieniają się w tych oknach, występuje naruszenie czasowe, co prowadzi do metastabilności lub nieprawidłowego przechwytywania danych.

3. Analizuj sygnały sterujące

Sygnały sterujące takie jak wybór chipa (CS), aktywacja (EN) lub reset (RST) określają, kiedy może nastąpić komunikacja.

- Czy wybór chipa jest aktywny na niskim poziomie czy wysokim?

- Czy sygnał Enable musi być aktywowany przed rozpoczęciem przełączania zegara?

- Czy istnieją jakieś zdarzenia asynchroniczne, które nadpisują logikę zegara?

4. Zweryfikuj mechanizmy wymiany sygnałów potwierdzających

Wiele protokołów używa wymiany sygnałów potwierdzających do zarządzania przepływem danych. Szukaj sygnałów potwierdzenia (ACK) lub gotowości (RDY).

- Czy nadawca czeka na sygnał przed przesłaniem kolejnego bajtu?

- Czy na wykresie przedstawione są warunki przekroczenia czasu oczekiwania?

📐 Jak tworzyć dokładne wykresy czasowe

Tworzenie diagramu czasowego jest równie ważne, jak jego odczytywanie. Służy jako specyfikacja dla inżynierów sprzętu i przewodnik weryfikacyjny dla programistów oprogramowania. Można je generować na podstawie wymagań, narzędzi pomiarowych lub danych symulacji.

Krok 1: Zdefiniuj wymagania protokołu

Zanim narysujesz, zebrz specyfikacje. Zazwyczaj pochodzą one z dokumentacji technicznej komponentu, z którym się łączysz.

- Wyciągnij minimalną i maksymalną częstotliwość zegara.

- Zanotuj poziomy napięć dla stanu logicznego wysokiego i niskiego.

- Zapisz ograniczenia czasu przygotowania (setup) i czasu utrzymania (hold).

Krok 2: Zbierz dane sygnałów

Użyj narzędzi sprzętowych do zapisania rzeczywistego zachowania sygnałów. Zapewnia to, że Twój diagram odzwierciedla rzeczywistość, a nie teoretyczne założenia.

- Oscyloskopy: Najlepsze do analizy integralności sygnałów analogowych i poziomów napięć.

- Analizatory logiczne: Najlepsze do analizy przejść stanów cyfrowych i synchronizacji wielokanałowej.

- Modele symulacyjne: Dobrze nadają się do weryfikacji logiki przed dostępnością sprzętu.

Krok 3: Narysuj przebiegi sygnałów

Narysuj sygnały w kolejności chronologicznej. Upewnij się, że skala czasu jest spójna we wszystkich kanałach.

- Używaj linii prostych do oznaczania poziomów logicznych.

- Używaj linii pochyłych do przejść, aby oznaczyć czasy narastania i spadania.

- Oznacz kluczowe punkty, takie jak krawędź zegara i zmiana danych.

Krok 4: Oznacz kluczowe ograniczenia

Uwagi dodają kontekst, którego same obrazy nie potrafią przekazać.

- Jasno oznacz okna czasu przygotowania (setup) i czasu utrzymania (hold).

- Wskazuj czas trwania określonych stanów protokołu (np. bit startowy, bit stopowy).

- Wyróżnij wszelkie znane opóźnienia lub opóźnienia w ścieżce sygnału.

🌐 Diagramy czasowe w powszechnych protokołach wbudowanych

Różne protokoły komunikacyjne mają różne cechy czasowe. Zrozumienie tych subtelności jest kluczowe dla integracji.

1. Inter-Integrated Circuit (I2C)

I2C to dwukablowy szeregowy magistrala synchroniczna. Używa SDA (Dane) i SCL (Zegar).

- Warunek startowy: SDA przechodzi z wysokiego na niski poziom, gdy SCL jest wysoki.

- Warunek zatrzymania:SDA przechodzi z niskiego na wysokie poziom, gdy SCL jest wysokie.

- Przesył danych:Dane są ważne, gdy SCL jest wysokie; zmiany zachodzą, gdy SCL jest niskie.

- ACK/NACK:Odbiorca przyciąga SDA na poziom niski podczas dziewiątego impulsu zegarowego, aby potwierdzić odbiór.

2. Interfejs szeregowy przeznaczony dla urządzeń peripheralnych (SPI)

SPI to czteroprzewodowa szyna synchroniczna zapewniająca wyższe prędkości niż I2C.

- Linie:MOSI (wyjście głównego), MISO (wejście głównego), SCK (zegar), SS (wybór podłączonych urządzeń).

- CPOL:Biegunowość zegara określa stan bezczynności (wysoki lub niski).

- CPHA:Faza zegara określa, kiedy dane są próbkowane (pierwszy lub drugi zboczenie).

- Wybór układu: Musi być aktywowane (aktywne) przed rozpoczęciem przełączania zegara.

3. Uniwersalny asynchroniczny odbiornik nadajnik (UART)

UART jest asynchroniczny, co oznacza, że nie ma wspólnego sygnału zegarowego. Czasowanie opiera się na szybkości transmisji (baud rate).

- Bit startowy:Przyciąga linię na poziom niski, aby oznaczyć początek ramki.

- Bity danych:Przesyłane są najpierw bity najmniej znaczące, zazwyczaj 8 bitów.

- Bit stopowy:Przyciąga linię na poziom wysoki, aby oznaczyć koniec ramki.

- Parzystość:Opcjonalny bit do sprawdzania błędów.

| Cecha | I2C | SPI | UART |

|---|---|---|---|

| Zegar | Synchroniczny (udostępniony) | Synchroniczny (udostępniony) | Asynchroniczny (bez zegara) |

| Przewody | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Adresowanie | Tak (adres bajtu) | Nie (oparte na połączeniach) | Nie |

| Maks. prędkość | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Powszechne naruszenia czasowe i debugowanie

Nawet przy starannym projekcie mogą wystąpić naruszenia czasowe. Często są one przyczyną nieregularnych błędów, które trudno odtworzyć.

1. Naruszenia czasu przygotowania i utrzymania

Występują, gdy dane przychodzą zbyt wcześnie lub zbyt późno względem krawędzi zegara.

- Objaw:Zakłócenia danych lub losowe błędy podczas przechwytywania przez analizator logiczny.

- Rozwiązanie:Zmniejsz prędkość zegara lub zoptymalizuj długości ścieżek płytki drukowanej.

2. Zniekształcenie zegara

Zniekształcenie zegara występuje, gdy sygnał zegara dociera do różnych komponentów w różnych momentach.

- Objaw:Warunki wyścigu, w których jeden przerzutnik przechwytuje dane przed tym, gdy inny jest gotowy.

- Rozwiązanie:Dopasuj długości ścieżek lub użyj dedykowanej sieci dystrybucji zegara.

3. Opóźnienie propagacji

Sygnały potrzebują czasu, aby przejść przez przewody i bramki. Długie ścieżki dodają istotne opóźnienie.

- Objaw: Problemy z integralnością sygnału lub odbicia na liniach wysokiej prędkości.

- Rozwiązanie: Użyj rezystorów końcowych i utrzymaj ścieżki jak najkrótsze.

4. Metastabilność

Gdy sygnały asynchroniczne przechodzą przez domeny zegarowe, przechwytywany rejestrowy może wejść w stan metastabilności.

- Objaw: Zawieszenie systemu lub losowe ponowne uruchomienia.

- Rozwiązanie: Użyj łańcuchów synchronizujących (dwa lub więcej rejestrów połączonych szeregowo), aby rozwiązać sygnał.

📝 Najlepsze praktyki dokumentacji

Tworzenie diagramów czasowych w celu dokumentacji zapewnia, że przyszli programiści będą mogli zrozumieć system bez konieczności odwrotnej analizy sprzętu.

- Spójność: Używaj standardowych symboli i stylów linii we wszystkich diagramach projektu.

- Skala: Upewnij się, że oś czasu jest liniowa i jasno oznaczona jednostkami (ns, µs, ms).

- Źródło: Zawsze łączy diagram z konkretną sekcją dokumentacji technicznej lub standardem protokołu.

- Przejrzystość: Unikaj zamieszania. Jeśli sygnał jest stały, przedstaw go jako poziomą linię zamiast zmieniającego się szumu.

- Wersjonowanie: Aktualizuj diagramy, gdy zmienia się sprzęt lub firmware w sposób istotny.

🔗 Ostateczne rozważania na temat integralności sygnału

Diagramy czasowe łączą abstrakcyjną logikę z rzeczywistością fizyczną. Pozwalają inżynierom wizualizować niewidoczne ograniczenia elektroniki cyfrowej. Nauka ich czytania pozwala rozwiązywać skomplikowane problemy sprzętowe. Nauka ich tworzenia pozwala projektować odpornie działające systemy, które funkcjonują niezawodnie w dowolnych warunkach.

Proces wymaga cierpliwości i uwagi do szczegółów. Każda krawędź, każde opóźnienie i każdy poziom napięcia mają znaczenie. W miarę jak systemy wbudowane stają się szybsze i bardziej złożone, zależność od dokładnych diagramów czasowych będzie tylko rosnąć. Traktuj je jako kluczowe specyfikacje, a nie opcjonalną dokumentację.

Zacznij od analizy dokumentacji technicznej używanych komponentów. Szukaj specyfikacji czasowych. Następnie spróbuj narysować diagramy na podstawie tych danych. Porównaj swoje rysunki z rzeczywistymi pomiarami z Twoich narzędzi. Ten cykl przewidywania i weryfikacji buduje intuicję niezbędną do projektowania zaawansowanych systemów wbudowanych.

Pamiętaj, że diagram to narzędzie komunikacji. Powinien przekazywać niezbędną informację inżynierowi z minimalnym niepewnością. Jasne i dokładne diagramy czasowe skracają czas rozwoju i zapobiegają kosztownym zmianom sprzętu. Inwestuj czas w opanowanie tej umiejętności – zwróci się ona zyskiem przez całą karierę inżynierską.