Zrozumienie przepływu sygnałów w czasie jest podstawą elektroniki cyfrowej. Dla inżynierów studiów pierwszego stopnia opanowanie interpretacji diagramów czasowych to nie tylko ćwiczenie akademickie; to kluczowa umiejętność projektowania niezawodnych systemów. Te reprezentacje wizualne pokazują zachowanie sygnałów wzdłuż osi czasu, ujawniając relacje między cyklami zegara, ważnością danych i sygnałami sterującymi. Bez solidnego zrozumienia tych technik nawet proste obwody mogą zawieść w warunkach rzeczywistych.

Ten przewodnik obejmuje podstawowe zasady potrzebne do skutecznego czytania, tworzenia i analizowania diagramów czasowych. Przeanalizujemy mechanizmy projektowania synchronicznego i asynchronicznego, znaczenie czasów ustalania i utrzymywania oraz sposób unikania typowych pułapek prowadzących do awarii obwodów. Na końcu tego artykułu będziesz miał solidne podstawy do rozwiązywania skomplikowanych problemów logiki cyfrowej.

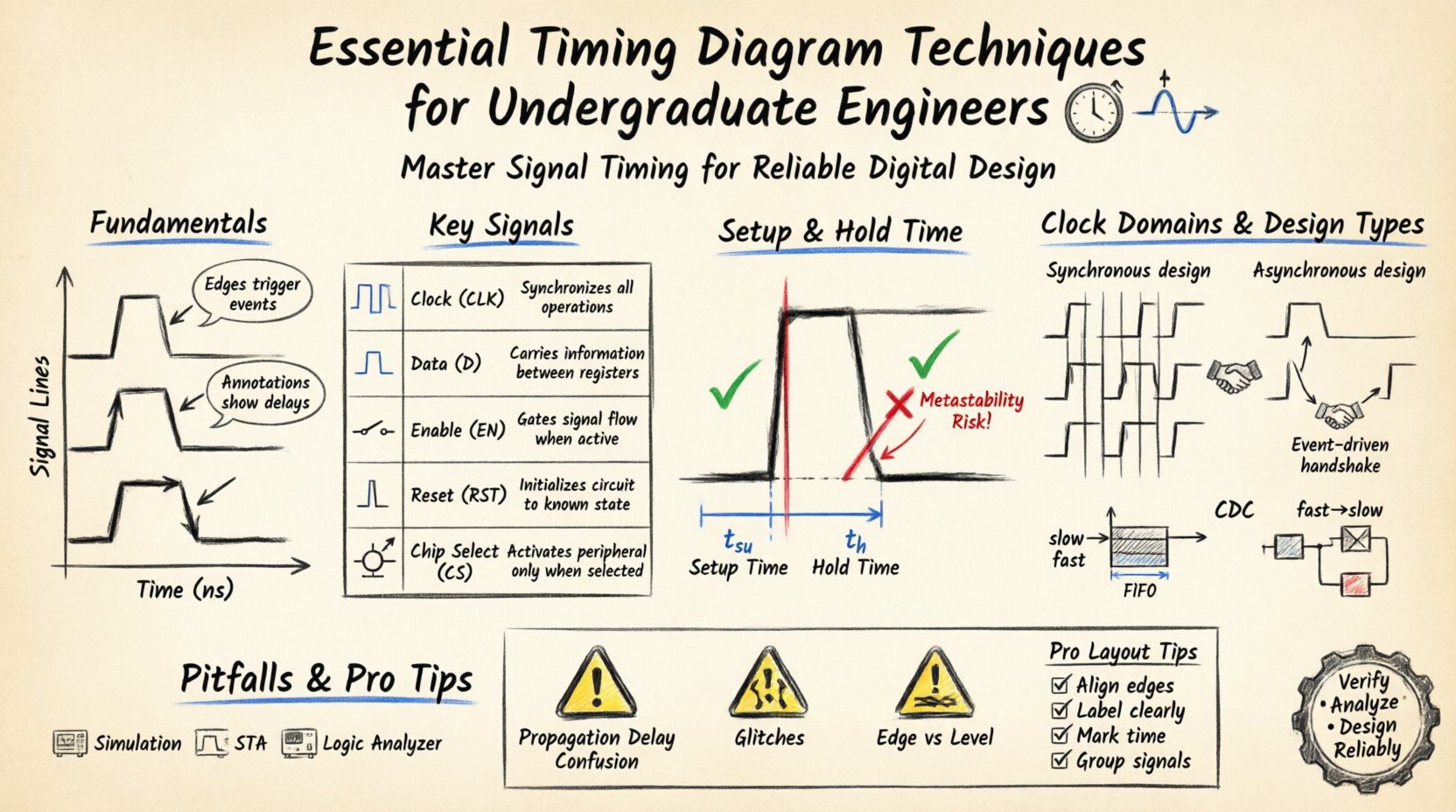

1. Podstawy diagramów czasowych 📐

Diagram czasowy to graficzna reprezentacja sygnałów w czasie. Pozwala inżynierom wizualizować stan różnych linii w obwodzie cyfrowym. W przeciwieństwie do schematów logicznych pokazujących połączenia, diagramy czasowe przedstawiają zachowanie. Są one niezbędne do debugowania, weryfikacji projektów oraz komunikacji interakcji sygnałów między modułami sprzętowymi.

Kluczowe elementy diagramu czasowego

- Oś czasu (oś X): Reprezentuje postęp czasu. Zazwyczaj oznaczona w nanosekundach (ns) lub cyklach zegara.

- Linie sygnałów (oś Y): Poziome linie reprezentujące pojedyncze przewody lub szyny. Każda linia odpowiada konkretnemu nazwie sygnału.

- Poziomy logiczne: Sygnały są zazwyczaj dwustanowe, reprezentowane jako wysoki (1) lub niski (0). Czasem w projektach szyn pojawiają się stany ‘High-Z’ (wysokie impedancje).

- Krawędzie: Pionowe przejścia wskazują zmianę stanu. Krawędzie narastające (od niskiego do wysokiego) i spadające (od wysokiego do niskiego) są kluczowe do wyzwalania zdarzeń.

- Adnotacje: Etykiety tekstowe często wskazują opóźnienia, konkretne chwile czasu lub warunki wpływające na sygnał.

Dlaczego czas jest ważny w logice cyfrowej

Systemy cyfrowe opierają się na dokładnej synchronizacji. Jeśli sygnał przychodzi zbyt wcześnie lub zbyt późno względem krawędzi zegara, system może błędnie zinterpretować dane. Diagramy czasowe czynią te ograniczenia widoczne. Pomagają odpowiedzieć na pytania takie jak:

- Czy dane są stabilne przed krawędzią zegara?

- Jak długo sygnał potrzebuje na rozchodzenie się przez bramkę?

- Czy dwa zegary z różnych domen mogą się wzajemnie zakłócać?

2. Kluczowe sygnały i komponenty ⚡

Zanim przeanalizujesz złożone przebiegi, musisz rozpoznać standardowe sygnały stosowane w inżynierii cyfrowej. Te sygnały określają sposób przemieszczania się danych oraz kiedy są uznawane za ważne.

Typy powszechnych sygnałów

| Nazwa sygnału | Funkcja | Typowe zachowanie |

|---|---|---|

| Zegar (CLK) | Źródło synchronizacji | Pulsowanie regularnie między 0 a 1 |

| Dane (D) | Nośnik informacji | Zmienia stan na podstawie wejścia lub logiki |

| Włącz (EN) | Aktywuje moduł | Wysoki pozwala na działanie, niski wyłącza |

| Reset (RST) | Inicjuje stan | Puls aktywny niski lub aktywny wysoki na początku |

| Wybór chipa (CS) | Wybiera urządzenie | Aktywny niski do adresowania konkretnego komponentu |

Zrozumienie stanu aktywnego sygnałów sterujących jest kluczowe. Niektóre sygnały są aktywne wysokie, co oznacza, że działają, gdy napięcie jest wysokie. Inne są aktywne niskie, co oznacza, że działają, gdy napięcie jest niskie, i jest to oznaczane kreską nad nazwą (np. /RESET lub RST_N), co oznacza, że działają, gdy napięcie jest niskie.

3. Analiza czasów ustalania i trzymania 🕒

Jednym z najważniejszych aspektów analizy czasowej są czasy ustalania i trzymania. Te parametry definiują okno, w którym dane muszą być stabilne względem krawędzi zegara. Naruszenie tych ograniczeń prowadzi do uszkodzenia danych lub metastabilności.

Czas ustalania (tsu)

Czas ustalania to minimalny czas, przez który dane muszą być stabilne przedprzychodu aktywnej krawędzi zegara. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, przerzutnik może nie przechwycić poprawnej wartości.

- Wymóg:Dane muszą być stabilne przez tsuprzed narastającą krawędzią.

- Skutki naruszenia: Rejestr może przechwycić niepoprawne dane lub wejść w stan niezdefiniowany.

Czas utrzymania (th)

Czas utrzymania to minimalny czas, przez który dane muszą pozostawać stabilnepo aktywnym krawędzi zegara. Flip-flop potrzebuje chwili, aby zatrzymać wartość przed przyjściem nowych danych.

- Wymóg:Dane muszą pozostawać stabilne przez th po zboczu narastającym.

- Skutki naruszenia: Podobnie jak naruszenia ustawienia, powoduje błędy danych lub metastabilność.

Wizualizacja czasów ustawienia i utrzymania

Przy odczytywaniu diagramu czasowego, szukaj sygnału danych względem krawędzi zegara. Linia danych powinna być płaska i niezmieniająca się w oknie ustawienia (przed) i oknie utrzymania (po). Jeśli linia danych zmienia się w tych oknach, projekt prawdopodobnie jest błędny.

4. Przejście między domenami zegara ⏱️

W złożonych systemach różne części obwodu mogą działać z różnymi prędkościami lub częstotliwościami zegara. Przenoszenie danych między tymi różnymi domenami zegara nazywa się przejściem między domenami zegara (CDC). Ten proces wprowadza istotne wyzwania czasowe.

Rodzaje domen zegara

- Ta sama częstotliwość, ta sama faza: Projekt synchroniczny. Stosuje się prostą analizę czasową.

- Ta sama częstotliwość, inna faza: Wymaga sprawdzenia wyrównania fazowego.

- Różne częstotliwości: Wymaga technik synchronizacji, takich jak wymiany potwierdzeń lub buforów FIFO.

Obsługa CDC w diagramach czasowych

Przy analizie diagramów z wieloma domenami zegara upewnij się, że jasno rozróżniasz linie zegara. Przenoszenie danych z domeny wolnej do szybkiej może być ryzykowne, jeśli nie jest odpowiednio zarządzane. Z kolei przechodzenie z szybkiej do wolnej domeny może prowadzić do utraty danych, jeśli odbiorca próbuje odczytać dane zbyt szybko.

- Protokoły wymiany potwierdzeń: Użyj sygnałów ważnych/gotowych, aby potwierdzić zakończenie transferu danych.

- Bufory FIFO: Odseparuj szybkości produkcji i zużycia.

- Synchronizatory: Użyj wielostopniowych przerzutników, aby zmniejszyć ryzyko metastabilności.

5. Projektowanie synchroniczne vs asynchroniczne 🔄

Architektura projektu decyduje o wyglądzie diagramów czasowych. Zrozumienie różnicy pomaga przewidywać zachowanie sygnałów.

Projektowanie synchroniczne

Większość logiki cyfrowej jest synchroniczna. Wszystkie zmiany stanu zachodzą na krawędzi centralnego sygnału zegarowego.

- Przewidywalność: Łatwiejsze do analizy, ponieważ czas jest kontrolowany.

- Diagramy czasowe: Regularne, siatko podobne do siatki. Zmiany danych są zgodne z krawędziami zegara.

- Ograniczenia: Zeskok zegara może stać się problemem w dużych projektach.

Projektowanie asynchroniczne

Zmiany stanu zachodzą na podstawie przybycia sygnałów, a nie globalnego zegara. Jest to powszechne w protokołach wymiany sygnałów i obsłudze przerwań.

- Elastyczność: Może być szybsze dla określonych zadań, ponieważ oczekuje tylko na dane.

- Diagramy czasowe: Nieregularne. Sygnały zależą od poprzednich zdarzeń, a nie ustalonych przedziałów czasu.

- Ryzyka: Podatne na warunki wyścigu i zagrożenia, jeśli nie są starannie zaprojektowane.

6. Powszechne pułapki i błędy ❌

Nawet doświadczeni inżynierowie popełniają błędy przy interpretacji lub tworzeniu diagramów czasowych. Znajomość tych powszechnych błędów może zaoszczędzić duży czas debugowania.

1. Ignorowanie opóźnienia propagacji

Sygnały nie zmieniają się natychmiast. Bramki mają opóźnienie propagacji. Jeśli narysujesz diagram zakładając natychmiastowe zmiany, twoja symulacja nie będzie odpowiadać rzeczywistości.

- Rozwiązanie: Zawsze uwzględniaj wartości opóźnień między przejściami logicznymi w diagramach.

2. Nieprawidłowe rozumienie sygnałów aktywnych niskich

Sygnał oznaczony jako/CS jest niski, gdy aktywny. Jeśli założysz, że jest wysoki, twoja logika będzie odwrotna.

- Poprawka: Sprawdź dokumentację lub schemat, aby ustalić stany aktywne. Szukaj kółek na bramkach logicznych.

3. Pomijanie zakłóceń

Zakłócenia to krótkie, niechciane impulsy. Mogą pojawić się, gdy sygnały poruszają się różnymi ścieżkami o różnych opóźnieniach.

- Poprawka: Użyj logiki wolnej od zagrożeń lub dodaj etapy filtracji w projekcie.

4. Pomylenie krawędzi z poziomem

Niektóre obwody są aktywne na zboczu narastającym, inne na zboczu spadającym, a inne na poziomie sygnału.

- Poprawka: Zweryfikuj warunek aktywacji w specyfikacji komponentu.

7. Czytanie i tworzenie profesjonalnych schematów 📝

Jasna komunikacja jest kluczowa w inżynierii. Dobrze narysowany schemat czasowy przekazuje złożone informacje na pierwszy rzut oka. Oto najlepsze praktyki tworzenia ich.

Najlepsze praktyki układu

- Wyrównaj krawędzie: Upewnij się, że powiązane sygnały zmieniają się w stałych odstępach czasu.

- Jasne oznaczenia: Używaj nazw sygnałów, a nie tylko ogólnych linii.

- Zaznacz czas: Zaznacz czas trwania cykli lub określonych opóźnień.

- Grupuj sygnały: Zgrupuj powiązane sygnały (np. linie szyny danych).

Krok po kroku proces tworzenia

- Zidentyfikuj zegary: Najpierw narysuj linie zegarowe. Są one fundamentem synchronizacji.

- Dodaj sygnały sterujące: Umieść linie włączania, resetowania i wybierania chipa.

- Narysuj dane: Dodaj linie danych na podstawie przepływu logiki.

- Dodaj notatki: Dodaj notatki dotyczące czasów ustawienia/zachowania lub określonych opóźnień.

- Przegląd: Sprawdź naruszenia i spójność logiczną.

8. Analiza scenariuszy z rzeczywistego świata 🔍

Rozważmy scenariusz dotyczący operacji odczytu pamięci. Jest to powszechna czynność dla inżynierów pracujących z mikrokontrolerami.

Cykl odczytu pamięci

W odczycie pamięci procesor wysyła adres, aktywuje polecenie odczytu i czeka na dane.

- Szyna adresowa:Poprawny przed krawędzią zegara.

- Wybór układu:Spada do poziomu niskiego, aby aktywować pamięć.

- Polecenie odczytu:Spada do poziomu niskiego, aby rozpocząć przesyłanie.

- Szyna danych:Zostaje w stanie High-Z, dopóki pamięć go nie aktywuje.

- Czasowanie:Dane muszą być stabilne przed tym, jak procesor je pobierze.

Rozważania dotyczące integralności sygnału

Wraz ze wzrostem częstotliwości integralność sygnału staje się istotnym czynnikiem. Odbicia, zakłócenia wzajemne i szum mogą deformować przebiegi. Diagramy czasowe w projektach wysokiej szybkości muszą uwzględniać te problemy warstwy fizycznej.

- Szybkość narastania:Jak szybko sygnał przechodzi z jednego poziomu na drugi. Zbyt szybkie przejście powoduje szum, zbyt wolne – błędy czasowania.

- Poziomy napięcia:Upewnij się, że progi logiczne są spełnione przy zmianach temperatury i napięcia.

9. Zaawansowane koncepcje czasowania 🧠

Dla tych, którzy chcą pogłębić swoje umiejętności, kilka zaawansowanych koncepcji rozszerza podstawową analizę czasowania.

Metastabilność

Metastabilność występuje, gdy przerzutnik nie jest w stanie osiągnąć stabilnego stanu 0 lub 1 w wymaganym czasie. Zazwyczaj dzieje się to, gdy dane zmieniają się zbyt blisko krawędzi zegara.

- Prawdopodobieństwo:Jest zdarzeniem prawdopodobieństwem, a nie deterministycznym.

- Zmniejszanie ryzyka:Użyj łańcuchów synchronizujących (wiele przerzutników połączonych szeregowo), aby zmniejszyć prawdopodobieństwo do poziomu zbliżonego do zera.

Zniekształcenie sygnału zegarowego

Zniekształcenie sygnału zegarowego to różnica w czasie przybycia sygnału zegarowego w różnych częściach obwodu. Zniekształcenie dodatnie (przychodzi później) może pomóc w czasie ustawienia, ale pogarsza czas utrzymania. Zniekształcenie ujemne robi dokładnie odwrotnie.

- Wpływ na projekt: Zniekształcenie musi być uwzględnione w budżetach czasowych.

- Pomiar: Użyj oscyloskopów lub narzędzi symulacyjnych do pomiaru zniekształcenia.

Drganie

Drganie to odchylenie krawędzi sygnału zegarowego od jej idealnego położenia. Zmniejsza ono skuteczne marginesy czasu ustawienia i utrzymania.

- Rodzaje: Drganie okresowe, drganie cyklu do cyklu oraz drganie losowe.

- Wpływ: Wysokie drganie ogranicza maksymalną częstotliwość pracy systemu.

10. Narzędzia i metody 🛠️

Choć analiza ręczna jest edukacyjna, współczesna inżynieria opiera się na narzędziach. Jednak zrozumienie podstawowej teorii pozwala skutecznie korzystać z tych narzędzi.

Oprogramowanie do symulacji

Języki opisu sprzętu (HDL) pozwalają na symulację. Te narzędzia automatycznie generują wykresy czasowe na podstawie kodu. Musisz zrozumieć wynik, aby zweryfikować poprawność kodu.

Statyczna analiza czasowa (STA)

Narzędzia STA matematycznie weryfikują, czy wszystkie ścieżki spełniają wymagania czasowe bez symulacji. Sprawdzają naruszenia czasu ustawienia i utrzymania we wszystkich warunkach (temperatura, napięcie).

Debugowanie za pomocą analizatorów logicznych

Debugger sprzętowe zapisują rzeczywiste sygnały z płytki. Wyświetlają wykresy czasowe odpowiadające rzeczywistości, pomagając wykryć problemy na warstwie fizycznej, które symulacja może pominąć.

Wnioski 🏁

Wykresy czasowe to język zachowania sygnałów cyfrowych. Połączone są z abstrakcyjną logiką a rzeczywistością fizyczną. Dla inżynierów studiujących, inwestowanie czasu w opanowanie tych technik przynosi korzyści przez całe życie zawodowe. Niezależnie od tego, czy projektujesz prosty licznik, czy złożony procesor, umiejętność odczytywania i analizowania ograniczeń czasowych jest niezastąpiona.

Skupiając się na czasach ustawienia i utrzymania, rozumiejąc domeny zegarowe oraz unikając typowych pułapek, budujesz solidną podstawę. Pamiętaj zawsze weryfikować stany aktywne i uwzględniać opóźnienia propagacji. W miarę postępów napotkasz bardziej złożone sytuacje, ale podstawowe zasady pozostają te same. Kontynuuj ćwiczenie analizy wykresów, a Twoje projekty będą coraz bardziej niezawodne i wydajne.

Kontynuuj doskonalenie swoich umiejętności, badając karty katalogowe i analizując rzeczywiste przebiegi sygnałów w obwodach. Obszar inżynierii cyfrowej szybko się rozwija, ale podstawy analizy czasowej pozostają niezmienne.