Zrozumienie przepływu sygnałów w systemie cyfrowym jest kluczowe dla inżynierów pracujących nad sprzętem, firmwarem lub oprogramowaniem wbudowanym. Diagram czasowy pełni rolę podstawowego narzędzia wizualnego do mapowania interakcji między różnymi sygnałami w określonym okresie. Ta reprezentacja wizualna pozwala zespołom sprawdzić, czy dane są poprawnie przechwytywane, czy zegary są stabilne oraz czy przejścia logiczne zachodzą bez konfliktu. Bez dokładnego zrozumienia tych diagramów niebezpieczeństwo utraty niezawodności systemu może być znaczne. Niniejszy przewodnik omawia kluczowe elementy, z których składa się diagram czasowy, zapewniając dokładny projekt i analizę.

Czym jest diagram czasowy? 📊

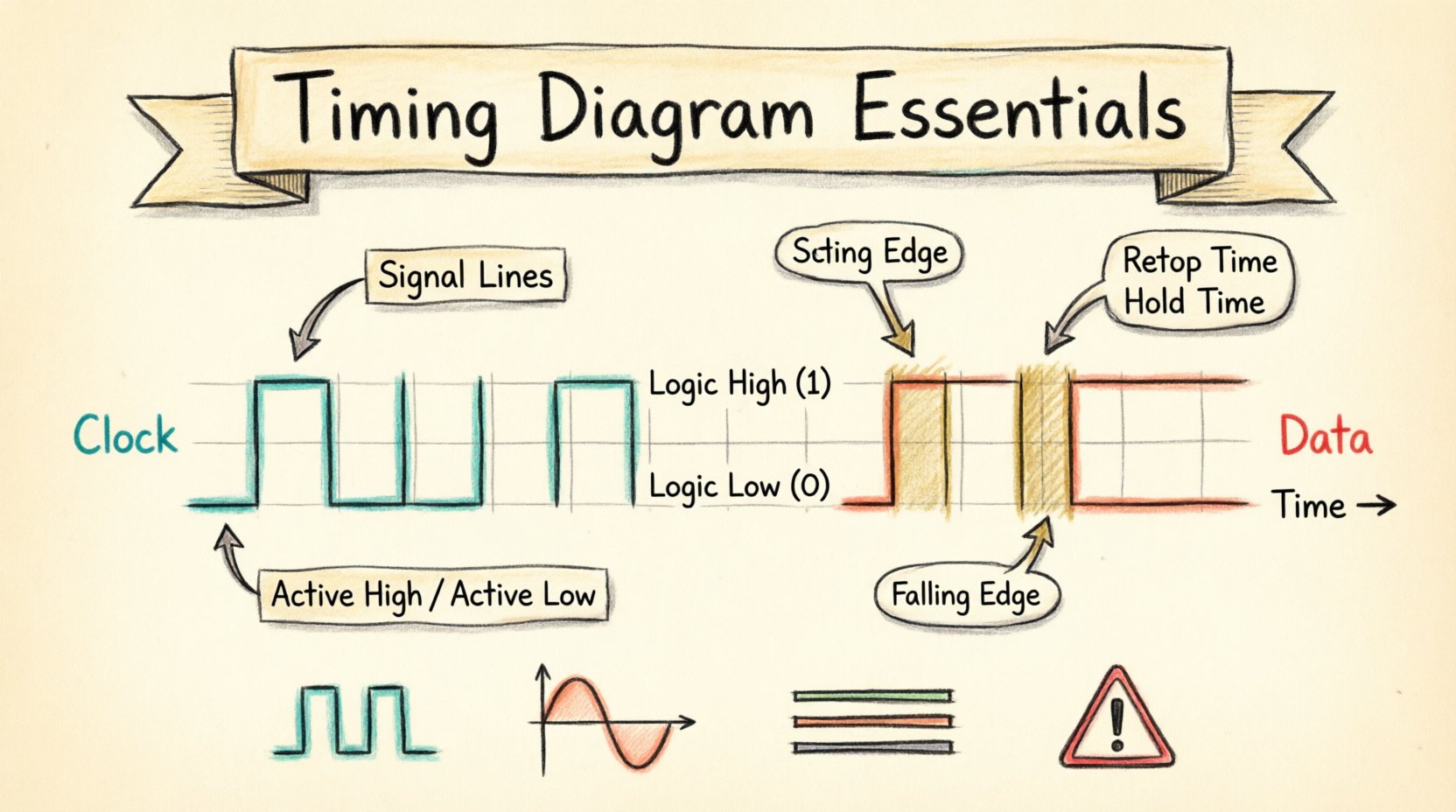

Diagram czasowy to graficzna ilustracja pokazująca zachowanie dwóch lub więcej sygnałów w czasie. Mapuje sekwencję zdarzeń, wskazując, kiedy sygnały zmieniają stan, jak długo pozostają w tym stanie oraz jak są powiązane z źródłem zegara. W projektowaniu sprzętu te diagramy są niezastąpione przy weryfikacji poprawnej komunikacji między komponentami. W oprogramowaniu pomagają wizualizować współbieżność, warunki wyścigu oraz punkty synchronizacji.

Te diagramy zwykle przedstawiają czas na osi poziomej (os x) oraz poziom lub stan sygnału na osi pionowej (os y). Pionowe linie reprezentują konkretne chwile czasu, podczas gdy poziome linie wskazują stan stały sygnału. Przejścia między tymi stanami są kluczowe, ponieważ wskazują rzeczywiste przesyłanie danych lub działania sterujące zachodzące w systemie.

Kluczowe komponenty diagramu czasowego 🔧

Aby odczytać lub stworzyć skuteczny diagram czasowy, należy zrozumieć podstawowe elementy budowlane. Każdy diagram, niezależnie od złożoności, opiera się na spójnym zestawie elementów zapewniających dokładne przekazywanie informacji.

- Oś czasu: Pozioma linia odniesienia reprezentująca upływ czasu. Zazwyczaj przepływa od lewej do prawej, wskazując „przeszłość” do „przyszłości”.

- Linie sygnałów: Poziome ścieżki przypisane do konkretnych przewodów, szyn lub zmiennych. Każda linia reprezentuje poziom logiczny konkretnego sygnału.

- Poziomy logiczne: Pionowe pozycje na linii sygnału. Zazwyczaj pokazywane są stany wysoki (1, Vcc, True) i niski (0, Gnd, False).

- Przejścia: Pionowe linie łączące poziomy logiczne. Krawędź narastająca przechodzi od stanu niskiego do wysokiego, podczas gdy krawędź spadająca przechodzi od wysokiego do niskiego.

- Adnotacje: Etykiety tekstowe lub znaczniki ułatwiające zrozumienie konkretnych zdarzeń, opóźnień lub stanów.

Oś czasu: dokładność ma znaczenie ⏳

Oś czasu jest fundamentem diagramu. Nie zawsze reprezentuje rzeczywiste sekundy; często przedstawia cykle zegara lub nanosekundy w zależności od prędkości projektu. Spójność skali jest kluczowa. Jeśli w jednym obszarze diagramu jedna kratka odpowiada 10 nanosekundom, inny obszar musi zachować tę samą skalę, chyba że został jawnie powiększony dla szczegółów.

Podczas analizy wydajności systemu oś czasu pomaga wykryć węzły zastojne. Na przykład, jeśli sygnał danych wymaga 50 nanosekund na ustabilizowanie się, ale krawędź zegara występuje po 40 nanosekundach, występuje naruszenie. Oś pozwala inżynierom bezpośrednio mierzyć te przedziały czasu.

Linie sygnałów i poziomy logiczne 🔄

Każda linia sygnału odpowiada fizycznemu przewodowi lub zmiennej logicznej. W złożonych systemach szyna może być przedstawiona jako gruba linia z wieloma sygnałami połączonymi razem, albo osobnymi liniami dla każdego bitu. Poziomy logiczne definiują stan sygnału:

- Aktywne wysokie: Sygnał uznawany jest za „włączony” lub „prawdziwy”, gdy napięcie jest wysokie.

- Aktywne niskie: Sygnał uznawany jest za „włączony” lub „prawdziwy”, gdy napięcie jest niskie. Często oznacza się to kropką na symbolu lub specjalną konwencją nazewnictwa.

Zrozumienie stanu aktywnego jest kluczowe przy interpretacji sygnałów sterujących takich jak „Wybór mikrochipu” lub „Włączanie zapisu”. Nieprawidłowe rozumienie sygnału aktywnego niskiego jako aktywnego wysokiego może prowadzić do błędów projektowych, które są trudne do zlokalizowania.

Przejścia i krawędzie ⚡

Przejścia zachodzą, gdy sygnał zmienia się z jednego poziomu logicznego na inny. Te zmiany rzadko są natychmiastowe w świecie fizycznym, ale w diagramie czasowym często są rysowane jako pionowe linie, aby przedstawić idealny moment zmiany.

- Krawędź narastająca: Przejście od niskiego do wysokiego poziomu. Jest to często punkt wyzwalający dla logiki synchronicznej.

- Krawędź spadająca: Przejście od wysokiego do niskiego poziomu. Niektóre systemy wykorzystują tę krawędź do przechwytywania danych.

- Wyzwalane krawędzią: Logika, która reaguje wyłącznie w momencie przejścia.

- Wyzwalane poziomem: Logika, która reaguje tak długo, jak sygnał pozostaje w określonym stanie.

Sygnały z rzeczywistego świata mają czasy narastania i spadania. Doskonała linia pionowa to abstrakcja. W projektach o wysokiej prędkości nachylenie przejścia ma znaczenie, ponieważ wpływa na zakłócenia elektromagnetyczne i integralność sygnału.

Parametry i ograniczenia czasowe 📐

Poza wizualnymi liniami, kluczowa wartość diagramu czasowego polega na parametrach ilościowych zdefiniowanych obok sygnałów. Te parametry określają granice fizyczne, w których musi działać sprzęt.

Czas ustawienia i czas utrzymania ⚙️

Są to dwa najbardziej typowe ograniczenia w projektowaniu logiki sekwencyjnej, szczególnie gdy dane są przechwytywane przez przerzutnik na krawędzi zegara.

- Czas ustawienia: Minimalna ilość czasu, przez którą sygnał danych musi być stabilny przed aktywnej krawędzi zegara. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, przerzutnik może nie przechwycić poprawnej wartości.

- Czas utrzymania: Minimalna ilość czasu, przez którą sygnał danych musi pozostawać stabilny po aktywnej krawędzi zegara. Jeśli dane zmieniają się zbyt szybko po krawędzi, przechwytywanie może zostać zaburzone.

| Parametr | Definicja | Skutki naruszenia |

|---|---|---|

| Czas ustawienia | Czas, przez który dane muszą być stabilne przed krawędzią zegara | Metastabilność lub niepoprawne przechwytywanie danych |

| Czas utrzymania | Czas, przez który dane muszą być stabilne po krawędzi zegara | Metastabilność lub niepoprawne przechwytywanie danych |

| Opóźnienie propagacji | Czas potrzebny sygnałowi na przejście przez bramkę | Zmniejszenie zapasu czasowego, niższa maksymalna częstotliwość |

| Zachwianie zegara | Różnica w czasie przybycia sygnału zegarowego | Zmniejszenie skutecznego okna czasowego |

Opóźnienie propagacji ⏱️

Opóźnienie propagacji to czas potrzebny na zmianę wejścia, aby wpłynąć na wyjście. Na diagramie czasowym jest widoczne jako odstęp między krawędzią zegara a wynikającą zmianą danych. To opóźnienie powstaje z powodu ograniczeń fizycznych, takich jak pojemność w przewodach i szybkość przełączania tranzystorów.

Podczas projektowania systemu suma opóźnień propagacji wzdłuż trasy musi być mniejsza niż okres zegara pomniejszony o czas ustawienia. Jeśli opóźnienie jest zbyt duże, system nie może działać z żądaną częstotliwością zegara.

Zachwianie zegara i drgania 📉

Zachwianie zegara odnosi się do różnicy w czasie przybycia sygnału zegarowego w różnych częściach obwodu. W idealnym diagramie linia zegara jest pionowa i jednocześnie dostępna dla wszystkich elementów. W rzeczywistości różnice w trasowaniu powodują zachwianie. Dodatnie zachwianie oznacza, że zegar przychodzi później w miejscu docelowym, co może pomóc przy czasie ustawienia, ale pogarsza czas utrzymania.

Drgania to zmienność w czasie krawędzi sygnału. To szum, który powoduje, że krawędź występuje wcześniej lub później niż oczekiwano. Duże drgania zmniejszają skuteczny margines czasowy, co wymaga działania systemu wolniej w celu utrzymania stabilności.

Rodzaje sygnałów i szyn 📡

Różne systemy używają różnych metod sygnowania. Diagram czasowy musi odzwierciedlać te różnice, aby być dokładnym.

Sygnały cyfrowe

Większość diagramów czasowych skupia się na logice cyfrowej. Te sygnały są dwustanowe, przełączające się między 0 a 1. Jasność diagramu zależy od jasnego oznaczenia progów logicznych. Niektóre sygnały mogą mieć stany pośrednie lub warunki „nie ważne”, zwykle oznaczone literą X.

Sygnały analogowe

Choć rzadsze w czystych diagramach czasowych cyfrowych, sygnały analogowe takie jak szyny napięciowe lub wyjścia czujników czasem są uwzględniane. Są one przedstawiane za pomocą nachylonych lub krzywych linii zamiast ostrej zmiany, co wskazuje na ciągłą zmianę, a nie na dyskretne przejścia stanów.

Szyny i dane równoległe

Gdy wiele bitów porusza się jednocześnie, często są grupowane. Diagram czasowy szyny pokazuje stan wszystkich bitów naraz. Jest istotne oznaczyć szerokość szyny (np. 8-bitowa, 32-bitowa) oraz pokazać okno danych ważnych, w którym wszystkie bity są stabilne jednocześnie.

Czytanie diagramu czasowego: przewodnik krok po kroku 🔍

Interpretacja tych diagramów wymaga systematycznego podejścia, aby nie pominąć istotnych szczegółów.

- Zidentyfikuj zegar: Znajdź główny punkt odniesienia czasowego. Wszystkie inne zdarzenia powinny być mierzone względem tej linii.

- Określ wrażliwość na krawędź: Sprawdź, czy system aktywuje się na zboczu narastającym czy spadającym zegara.

- Śledź ważność danych: Poszukaj okresu, w którym linie danych są stabilne. Jest to „okno ważne”.

- Sprawdź sygnały sterujące: Zidentyfikuj linie włączania, resetu lub wyboru układu, które sterują przesyłaniem danych.

- Mierz przedziały: Użyj osi czasu do pomiaru opóźnień, czasów ustawienia i szerokości impulsów.

Typowe naruszenia i błędy czasowe ⚠️

Nawet przy dokładnym planowaniu występują naruszenia czasowe. Rozpoznanie objawów na diagramie to pierwszy krok w ich naprawie.

- Naruszenie czasu ustawienia: Dane przychodzą zbyt późno na następny zbocze zegarowe. Rozwiązanie często polega na spowolnieniu zegara lub optymalizacji ścieżki logicznej w celu zmniejszenia opóźnienia.

- Naruszenie czasu utrzymania: Dane zmieniają się zbyt wcześnie po zboczu zegarowym. Jest to często trudniejsze do naprawienia, ponieważ może wymagać dodania opóźnienia na ścieżce danych lub na ścieżce zegarowej.

- Metastabilność: Stan, w którym wyjście przerzutnika nie jest ani 0, ani 1 przez nieokreślony czas. Zazwyczaj występuje, gdy są naruszone czasy ustawienia lub utrzymania.

- Zakłócenia: Krótkie, niechciane impulsy spowodowane warunkami wyścigu w logice kombinacyjnej. Mogą wywołać fałszywe zmiany stanu, jeśli nie zostaną filtrowane.

Projekt asynchroniczny w porównaniu do projektu synchronicznego 🔄

Diagramy czasowe wyglądają inaczej w zależności od metodyki projektowania.

Projekt synchroniczny

Zdarzenia są koordynowane przez globalny zegar. Diagram czasowy pokazuje wyraźne, okresowe linie zegarowe. Dane zmieniają się tylko w zbocza zegarowe. Ten podejście upraszcza analizę, ponieważ okno czasowe jest stałe.

Projekt asynchroniczny

Zdarzenia są koordynowane przez sygnały wymiany zdań (np. żądanie i potwierdzenie). Diagram czasowy pokazuje nieregularne odstępy między zdarzeniami. Choć bardziej elastyczne, takie diagramy są trudniejsze do analizy, ponieważ nie ma stałego odniesienia czasowego.

Zastosowanie w protokołach 📡

Protokoły komunikacyjne bardzo mocno opierają się na dokładnym czasie. Zrozumienie diagramu jest kluczowe do implementacji tych standardów.

Komunikacja szeregowa

Interfejsy szeregowe wysyłają dane bit po bicie. Diagram czasowy pokazuje okres bitu. Zależność między zegarem a linią danych (np. dane ważne na zboczu narastającym) określa zasady protokołu.

Komunikacja równoległa

Interfejsy równoległe wysyłają wiele bitów jednocześnie. Diagram czasowy musi pokazywać czas ustawienia dla całej szyny. Wszystkie bity muszą być stabilne przed wystąpieniem zbocza zapisującego.

Najlepsze praktyki dokumentowania 📝

Tworzenie jasnej dokumentacji zapewnia, że inni inżynierowie mogą zrozumieć system bez niejasności.

- Używaj spójnych etykiet: Nadaj sygnałom nazwy dokładnie takie, jakie pojawiają się w kodzie lub schemacie.

- Dołącz jednostki: Zawsze podaj jednostki czasu (ns, µs, cykle) na osi.

- Wyróżnij krytyczne ścieżki: Użyj pogrubionych linii lub kolorów, aby wskazać sygnały najbardziej wrażliwe na czas.

- Oznacz naruszenia: Jeśli naruszenie jest znane, oznacz je wyraźnie, zamiast ukrywać.

- Zachowaj aktualność: Aktualizuj schematy za każdym razem, gdy zmienia się projekt. Uprzestnione schematy są głównym źródłem błędów.

Zaawansowane rozważania: wiele domen zegarowych 🌐

Nowoczesne systemy często działają z wieloma domenami zegarowymi działającymi z różnymi prędkościami. Schemat czasowy dla tych systemów musi jasno pokazywać relację między zegarami.

- Przejścia między zegarami: Dane przechodzące z szybszej domeny do wolniejszej wymagają dokładnej synchronizacji, aby uniknąć utraty danych.

- Relacje fazowe: Jeśli dwa zegary mają wspólny źródło, ale różne fazy, schemat musi pokazywać przesunięcie fazowe.

- Logika wymiany potwierdzeń: Asynchroniczne mosty między domenami opierają się na sygnałach wymiany potwierdzeń. Schemat czasowy musi pokazywać pełny cykl żądania-potwierdzenia.

Rola symulacji w analizie czasowej 💻

Zanim sprzęt zostanie zbudowany, symulacje weryfikują schematy czasowe. Inżynierowie używają widoków przebiegów, aby porównać oczekiwane zachowanie z wynikami symulacji.

- Statyczna analiza czasowa: Oblicza najgorsze opóźnienia bez symulacji rzeczywistych przebiegów.

- Dynamiczna symulacja czasowa: Uruchamia wersję wirtualną obwodu w celu wygenerowania rzeczywistych przebiegów.

- Symulacja po układzie: Uwzględnia fizyczne długości przewodów i pojemność po zaprojektowaniu układu.

Te narzędzia pozwalają inżynierom weryfikować schemat czasowy pod kątem rzeczywistości fizycznej. Jeśli symulacja pokazuje naruszenie ustawienia, projekt musi zostać zmieniony przed produkcją.

Wnioski dotyczące dokładności czasowej ✅

Opanowanie tworzenia i interpretacji schematów czasowych to podstawowa umiejętność dla specjalistów technicznych. Te schematy łączą przerwę między abstrakcyjną logiką a rzeczywistością fizyczną. Zapewniają, że sygnały docierają w odpowiednim czasie, w odpowiednim stanie i z wystarczającą stabilnością, aby system działał. Przestrzeganie elementów i ograniczeń przedstawionych w tym poradniku pozwala zmniejszyć błędy i poprawić niezawodność systemu. Uwaga na szczegóły w tych przedstawieniach wizualnych przynosi korzyści w stabilności i wydajności końcowego produktu.

Niezależnie od pracy nad szybkimi interfejsami pamięci, mikrokontrolerami o niskim zużyciu energii czy skomplikowanymi szynami danych, zasady pozostają te same. Czas to stała, a sygnały to zmienne. Zrozumienie ich relacji to klucz do sukcesu inżynierskiego.