Zrozumienie zachowania układów cyfrowych wymaga więcej niż tylko znajomości bramek logicznych. Wymaga to zrozumienia, jak sygnały zmieniają się w czasie. Diagramy czasowe dostarczają języka wizualnego do tej analizy czasowej. Wizualizują stan różnych sygnałów względem zegara lub określonego zdarzenia. Dla studentów informatyki opanowanie tego pojęcia jest kluczowe do projektowania niezawodnych systemów.

Ten przewodnik omawia mechanikę, techniki odczytywania oraz kluczowe parametry związane z diagramami czasowymi. Omówimy wszystko – od podstawowych przejść sygnałów po złożone naruszenia czasu ustawienia i utrzymania. Po zakończeniu tego omówienia będziesz miał solidne podstawy do analizy interakcji cyfrowych.

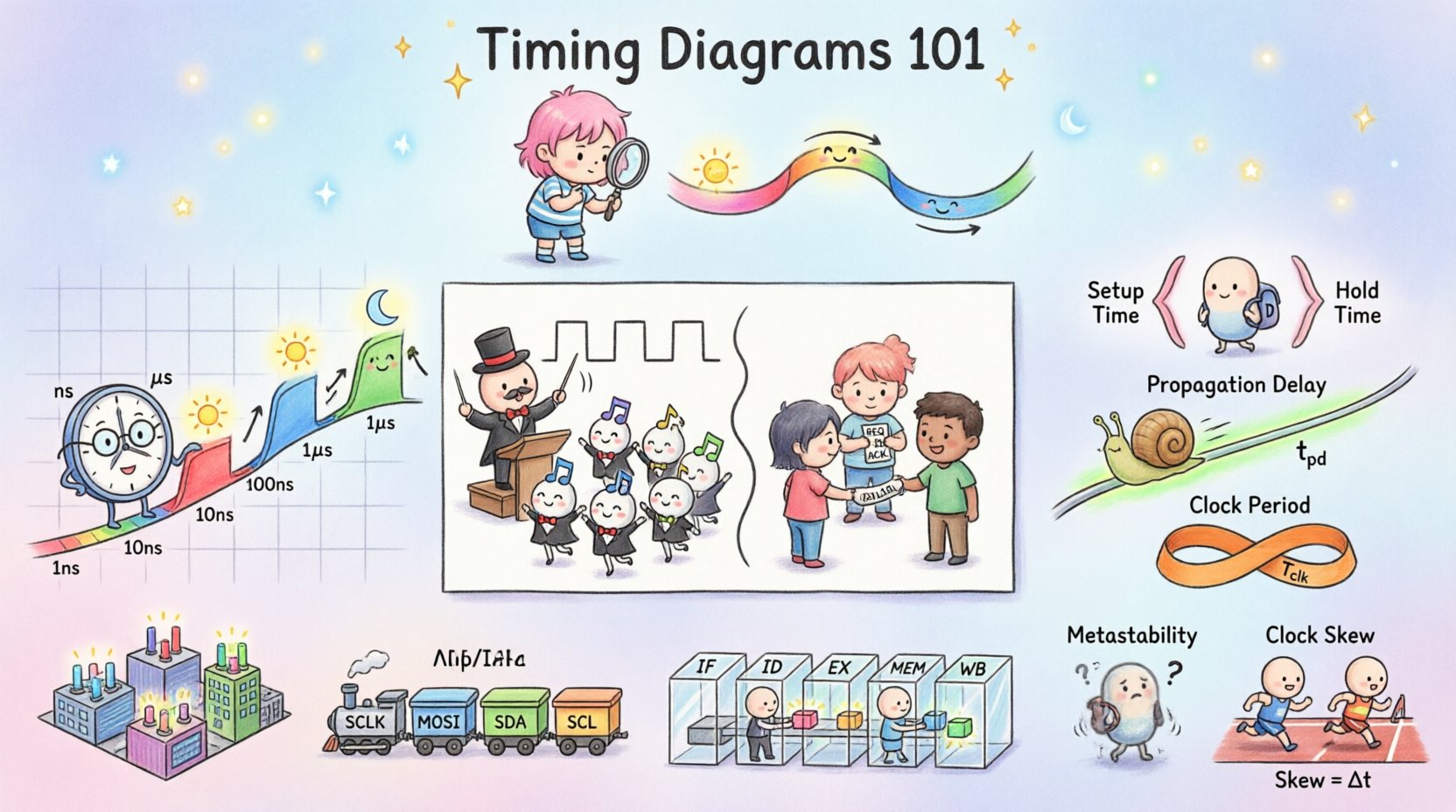

Czym jest diagram czasowy? ⏱️

Diagram czasowy to graficzne przedstawienie relacji między dwoma lub więcej sygnałami w czasie. Działa jak linia czasu dla zdarzeń cyfrowych. Każdy sygnał jest przedstawiony jako pozioma linia. Położenie pionowe wskazuje poziom logiczny lub stan. Oś pozioma reprezentuje upływ czasu.

Te diagramy są kluczowe do weryfikacji poprawnego działania układu cyfrowego. Pomagają inżynierom przewidywać, jak dane poruszają się przez rejestry, szyny i pamięć. Bez nich debugowanie problemów sprzętowych staje się niemal niemożliwe. Zamykają luki między abstrakcyjną logiką a rzeczywistością fizyczną.

Kluczowe elementy sygnałów cyfrowych 📡

Zanim przejdziemy do analizy diagramów, należy zrozumieć same sygnały. Układy cyfrowe opierają się na poziomach napięcia do reprezentowania danych binarnych. Te poziomy nie są zawsze stałe; przechodzą między stanami.

- Stan logiczny wysoki (1): Zazwyczaj reprezentuje napięcie bliskie poziomowi zasilania.

- Stan logiczny niski (0): Zazwyczaj reprezentuje napięcie bliskie ziemi.

- Krawędzie: Punkty przejścia między wysokim a niskim stanem. Krawędzie narastające przechodzą od niskiego do wysokiego. Krawędzie spadające przechodzą od wysokiego do niskiego.

- Stan ustalony: Okres, w którym sygnał pozostaje stały.

- Marginesy szumów: Tolerancja sygnału przed jego nieprawidłowym odczytaniem.

Diagramy czasowe wizualizują te przejścia. Pokazują dokładnie, kiedy sygnał się zmienia i jak długo pozostaje w danym stanie. Ta precyzja jest kluczowa do zapewnienia integralności danych.

Zrozumienie osi czasu ⏳

Oś pozioma jest fundamentem każdego diagramu czasowego. Reprezentuje upływ czasu. W projektowaniu cyfrowym oś ta często jest zsynchronizowana z sygnałem zegara. Zegar działa jak bicie serca systemu.

Jednostki na osi czasu różnią się w zależności od prędkości obwodu. Powszechnie używane jednostki to:

- Sekundy (s): Używane dla bardzo wolnych układów.

- Mili-sekundy (ms): 10^-3 sekundy.

- Mikrosekundy (µs): 10^-6 sekundy.

- Nanosekundy (ns): 10^-9 sekundy. Standard dla nowoczesnych procesorów.

- Pikosekundy (ps): 10^-12 sekund. Wymagane dla interfejsów o wysokiej prędkości.

Przy czytaniu diagramu szukaj oznaczeń skali. Wskazują one na czas trwania każdego cyklu. Pomaga to w obliczaniu opóźnień propagacji oraz zapewnieniu, że sygnały przychodzą w wymaganym oknie czasowym.

Systemy synchroniczne vs asynchroniczne 🔄

Systemy cyfrowe ogólnie dzielą się na dwa rodzaje w zależności od sposobu obsługi czasu. Zrozumienie różnicy jest kluczowe do rysowania dokładnych diagramów.

1. Systemy synchroniczne

W projektach synchronicznych wszystkie zmiany stanu zachodzą względem sygnału zegarowego globalnego. Diagram czasowy pokaże okresowy kształt sygnału zegarowego. Każdy przerzutnik aktualizuje się na aktywnym zboczu tego zegara.

- Zalety:Prawidłowe zachowanie. Łatwiejsze weryfikowanie.

- Wyzwania:Zaburzenie zegara może powodować problemy, jeśli sygnały przychodzą w różnych momentach.

- Cecha diagramu:Pionowe linie często są zgodne z krawędziami zegara, aby pokazać chwile przechwytywania.

2. Systemy asynchroniczne

Projekty asynchroniczne nie opierają się na zegarze globalnym. Zamiast tego używają protokołów wymiany potwierdzeń lub lokalnych sygnałów do wyzwalania działań. Diagramy czasowe są tutaj bardziej nieregularne.

- Zalety:Zmniejszone zużycie mocy w niektórych przypadkach. Szybsze średnie czasy reakcji.

- Wyzwania:Złożone w weryfikacji. Podatne na warunki wyścigu.

- Cecha diagramu:Sygnały wzajemnie wyzwalają się bez stałego rytmu.

Krytyczne parametry czasowe 📏

Pewne pomiary określają wiarygodność diagramu czasowego. Te parametry decydują, czy obwód będzie działał poprawnie we wszystkich warunkach.

| Parametr | Opis | Znaczenie |

|---|---|---|

| Opóźnienie propagacji | Czas potrzebny sygnałowi na przejście od wejścia do wyjścia. | Ogranicza maksymalną częstotliwość pracy. |

| Czas ustawienia | Dane czasowe muszą być stabilne przed krawędzią zegara. | Zapewnia, że przechwytywacz przechwytuje poprawną wartość. |

| Czas utrzymania | Dane czasowe muszą pozostać stabilne po krawędzi zegara. | Zapobiega przechwytywaczowi odczytaniu zmieniającej się wartości. |

| Okres zegara | Czas trwania jednego pełnego cyklu sygnału zegarowego. | Określa szybkość działania systemu. |

| Współczynnik wypełnienia | Procent okresu, w którym sygnał jest wysoki. | Wpływ na zużycie energii i marginesy czasowe. |

Szczegółowy przegląd: Czas ustawienia i czas utrzymania

Czas ustawienia i czas utrzymania to najważniejsze ograniczenia dla logiki sekwencyjnej. W przypadku ich naruszenia system może wejść w stan metastabilny, w którym wyjście jest nieokreślone.

Naruszenie czasu ustawienia: Występuje, gdy dane zmieniają się zbyt blisko krawędzi zegara. Obwód nie ma wystarczająco dużo czasu na przygotowanie do przechwytywania. Wynikiem często jest błąd logiczny.

Naruszenie czasu utrzymania: Występuje, gdy dane zmieniają się zbyt szybko po krawędzi zegara. Obwód wciąż próbuje przechwycić poprzednią wartość. Jest to często trudniejsze do naprawienia, ponieważ zależy od fizycznej kompozycji układu.

Czytanie i analizowanie diagramów 🔍

Analiza diagramu czasowego wymaga systematycznego podejścia. Postępuj zgodnie z poniższymi krokami, aby poprawnie zinterpretować dane wizualne.

- Zidentyfikuj zegar: Znajdź sygnał okresowy. Jest to punkt odniesienia.

- Znajdź aktywne krawędzie: Określ, czy system aktywuje się na zboczu narastającym czy spadającym.

- Śledź zależności sygnałów: Zobacz, jak zmiany w jednym sygnale wpływają na inne.

- Sprawdź obecność zakłóceń: Poszukaj krótkich impulsów, które mogą być szumem lub niechcianymi przejściami.

- Weryfikuj ograniczenia: Upewnij się, że czas ustawienia i czas utrzymania są zachowane dla wszystkich rejestrów.

Rozważ prosty scenariusz przesyłania danych. CPU wysyła dane do pamięci. Diagram czasowy pokaże najpierw stabilizację linii adresowych, następnie linii danych, a na końcu sygnału zapisu. Każdy krok musi odbyć się w określonym oknie czasowym.

Typowe naruszenia i ich skutki ⚠️

Nawet doświadczeni inżynierowie napotykają problemy z czasem. Zrozumienie typowych naruszeń pomaga w diagnozowaniu problemów.

1. Metastabilność

Gdy sygnał narusza czas ustawienia lub czas utrzymania, wyjście przerzutnika może oscylować przed ustabilizowaniem się. Ten stan nazywa się metastabilnością. Może się rozprzestrzeniać przez system, powodując niestabilne zachowanie. Często stosuje się obwody synchronizacji, aby zmniejszyć ten ryzyko.

2. Zeskok

Zeskok zegara występuje, gdy sygnał zegarowy dociera do różnych komponentów w różnych momentach. Może to zmniejszyć skuteczny margines czasowy. Zeskok dodatni daje więcej czasu ustawienia, ale mniej czasu utrzymania. Zeskok ujemny robi dokładnie odwrotnie.

3. Warunki wyścigu

Warunki wyścigu występują, gdy wyjście zależy od kolejności zdarzeń. Jeśli dwa sygnały zmieniają się jednocześnie, kolejność ich przetwarzania decyduje o końcowym stanie. Diagramy czasowe pomagają wizualizować te sekwencje, aby zapobiec wyścigom.

Zastosowanie w architekturze komputerów 🖥️

Diagramy czasowe to nie tylko narzędzia teoretyczne. Są szeroko wykorzystywane w rzeczywistej architekturze.

Interfejsy pamięci

DRAM i SRAM mają ścisłe wymagania czasowe. Kontroler pamięci musi czekać na określone opóźnienia przed odczytem lub zapisem. Diagramy czasowe definiują sekwencje magistrali poleceń. Zapewniają one, że bank pamięci jest gotowy przed dostępem do danych.

Protokoły magistrali

Protokoły takie jak I2C, SPI i UART opierają się na czasie w komunikacji. Linia zegarowa w SPI synchronizuje przesyłanie danych. W UART czas jest oparty na szybkości transmisji (baud rate). Odbiornik musi próbkować linię danych dokładnie w środku okresu bitu. Diagram czasowy pokazuje ustawienie bitu startowego, bitów danych i bitu stopu.

Etapy procesu potokowego

Nowoczesne procesory używają przetwarzania potokowego, aby wykonywać wiele instrukcji jednocześnie. Każdy etap musi zostać zakończony w ciągu jednego cyklu zegarowego. Diagramy czasowe pokazują przepływ danych przez etapy pobierania, dekodowania, wykonywania i zapisu wyników. Pomagają one wykrywać zatrzymania, gdy jeden etap czeka na inny.

Najlepsze praktyki dokumentacji 📝

Tworzenie jasnych diagramów czasowych zapewnia, że inni inżynierowie zrozumieją Twój projekt. Postępuj zgodnie z tymi wskazówkami, aby skutecznie dokumentować.

- Używaj spójnych skal: Upewnij się, że oś czasu jest jednolita przez całą dokumentację.

- Oznacz jasno: Nazwij każdy sygnał. Unikaj ogólnych oznaczeń takich jak „Sygnał 1”.

- Wyróżnij ograniczenia: Używaj nawiasów lub zacienionych obszarów, aby pokazać okna ustawienia i utrzymania.

- Grupuj powiązane sygnały: Trzymaj sygnały sterujące razem oraz sygnały danych razem.

- Dołącz adnotacje: Dodaj notatki wyjaśniające złożone przejścia lub specjalne zachowania.

Zaawansowane rozważania 🔬

Wraz z szybszymi systemami analiza czasowa staje się bardziej złożona. Wiele czynników dodaje warstwy trudności.

1. Szum zasilacza

Fluktuacje napięcia mogą przesuwać poziomy progu bramek logicznych. To skutecznie zmienia opóźnienie propagacji. Diagramy czasowe muszą uwzględniać najgorsze przypadki napięciowe.

2. Zmiany temperatury

Elementy elektroniczne zachowują się inaczej w różnych temperaturach. Wysokie temperatury zwiększają oporność i opóźnienia. Niskie temperatury mogą wpływać na pojemność. Projektanci muszą zweryfikować czasowanie w całym zakresie pracy temperatur.

3. Integralność sygnału

Długie ścieżki na płycie drukowanej działają jak linie przesyłowe. Odbicia i zakłócenia międzyprzewodowe mogą zakłócać sygnały. Diagramy czasowe powinny zawierać diagramy oczkowe lub metryki jakości sygnału dla szybkich połączeń.

Wnioski dotyczące analizy czasowej 🎯

Diagramy czasowe to mapa do nawigowania w logice cyfrowej. Przekładają abstrakcyjne stany binarne na zdarzenia fizyczne w czasie. Dla studenta informatyki opanowanie umiejętności czytania i tworzenia tych diagramów jest podstawową kompetencją.

Zrozumienie cykli zegara, opóźnień propagacji i ograniczeń ustawienia pozwala projektować systemy wytrzymałe i efektywne. Umiejętność wizualizacji przepływu sygnału zapobiega kosztownym błędom w projektowaniu sprzętu. W miarę postępu technologicznego zasady pozostają te same. Czas to zmienna stała.

Skup się na podstawach. Ćwicz czytanie istniejących diagramów. Rysuj własne dla każdego nowego obwodu, który budujesz. Ta dyscyplina bardzo Ci pomoże w karierze technicznej.