Systemy cyfrowe opierają się na dokładnej synchronizacji, aby poprawnie działać. Bez dokładnego czasu uszkodzenie danych, awarie systemu i niebezpieczeństwa bezpieczeństwa stają się nieuniknione. Diagram czasowy zapewnia wizualne przedstawienie zmian sygnałów w czasie, dając jasne widzenie relacji między cyklami zegara, ważnością danych i sygnałami sterującymi. Niniejszy przewodnik bada kluczową rolę diagramów czasowych w różnych sektorach, szczegółowo opisując praktyczne przykłady i rozwiązania techniczne dla typowych wyzwań.

🔍 Zrozumienie podstaw

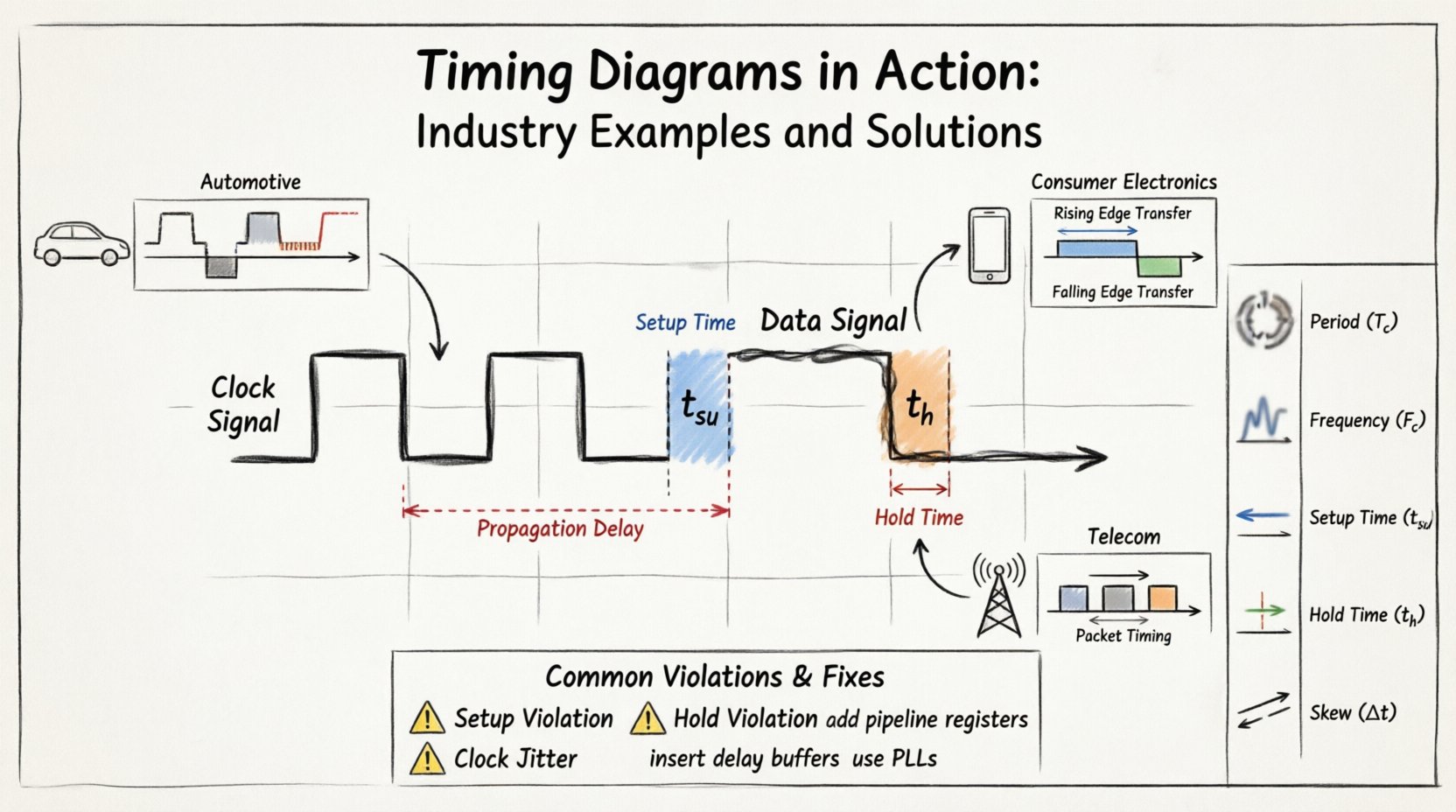

Zanim przejdziemy do konkretnych zastosowań, konieczne jest zrozumienie podstawowych elementów diagramu czasowego. Te diagramy odwzorowują zachowanie sygnałów względem zegara odniesienia. Nie są to po prostu rysunki; są to ograniczenia matematyczne, które określają zachowanie sprzętu.

- Krawędzie sygnału: Przejście od niskiego do wysokiego (krawędź narastająca) lub od wysokiego do niskiego (krawędź spadająca) wywołuje zmiany stanu w logice sekwencyjnej.

- Okres zegara: Czas pomiędzy dwoma kolejnymi krawędziami tego samego kierunku określa czas dostępny do ustabilizowania logiki.

- Opóźnienie propagacji: Czas potrzebny sygnałowi na przejście od pinu wejściowego do pinu wyjściowego przez bramki logiczne.

- Czasy ustalania i utrzymywania: Kluczowe ograniczenia zapewniające stabilność danych przed i po krawędzi zegara.

Gdy te parametry są naruszone, obwód może wejść w stan metastabilny, co prowadzi do niestabilnego działania. Inżynierowie używają diagramów czasowych, aby zweryfikować, czy fizyczna realizacja projektu spełnia te wymagania logiczne.

🚗 Elektronika samochodowa: krytyczne dla bezpieczeństwa czasy

Przemysł motoryzacyjny wymaga najwyższej wiarygodności. Samochody zawierają dziesiątki jednostek sterujących elektronicznie (ECU), które komunikują się przez magistrale takie jak CAN (sieć obszaru sterowania), LIN (lokalna sieć łączności) i FlexRay. Analiza czasu tutaj nie dotyczy tylko szybkości, ale przede wszystkim determinizmu i bezpieczeństwa.

1. Arbitracja magistrali CAN

Magistrala CAN pozwala wielu węzłom komunikować się po jednym przewodzie. Diagram czasowy arbitracji CAN ujawnia, jak ustalana jest priorytetność podczas konkurencji magistrali.

- Dominujący vs. Rezynujący: Poziomy logiczne są reprezentowane przez stany napięcia. Bit dominujący (0) nadpisuje bit rezynujący (1).

- Synchronizacja: Węzły synchronizują się z początkiem bitu ramki za pomocą odcinków synchronizacji.

- Punkt próbkowania: Dane są próbkowane w określonym procentzie czasu bitu, aby uniknąć szumów.

Jeśli punkt próbkowania jest zbyt blisko krawędzi, szum może spowodować błędy bitów. Jeśli jest zbyt późno, dane mogą nie być stabilne. Diagramy czasowe pomagają inżynierom poprawnie ustawić punkt próbkowania, zazwyczaj około 80% czasu bitu.

2. Próbkowanie ADC w łączeniu czujników

Nowoczesne pojazdy wykorzystują wiele czujników (radar, lidar, kamery), aby stworzyć obraz otoczenia. Przekształtniki analogowo-cyfrowe (ADC) muszą próbkować sygnały w dokładnych odstępach czasu, aby uniknąć zjawiska aliasingu.

- Drgania zegara:Zmiany w czasie krawędzi zegara wprowadzają szum do sygnału cyfrowego.

- Opóźnienie: Czas od wejścia czujnika do wyjścia przetworzonych danych musi być minimalizowany w celu kontroli w czasie rzeczywistym.

- Przemiennik:Wiele przetworników ADC często działa równolegle. Diagramy czasowe zapewniają zgodność ich faz, aby zapobiec przerwom w danych.

📱 Elektronika użytkowa: Interfejsy wysokiej prędkości

Urządzenia użytkowe priorytetowo ustawiają wydajność i efektywność energetyczną. Interfejsy takie jak pamięć DDR i połączenia wyświetlające wymagają ścisłych okien czasowych, aby osiągnąć wysoką przepustowość bez zwiększania zużycia energii.

1. Interfejsy pamięci DDR

Pamięć Double Data Rate (DDR) przesyła dane zarówno na zboczu narastającym, jak i opadającym sygnału zegarowego. Dzięki temu podwaja się skuteczna prędkość przesyłania danych, ale czas okna stabilności danych zmniejsza się o połowę.

| Parametr | Definicja | Skutki naruszenia |

|---|---|---|

| Czas ustalenia | Czas, przez który dane muszą być stabilne przed zboczem zegarowym | Pominięcie przesyłania danych, zawieszenie systemu |

| Czas utrzymania | Czas, przez który dane muszą pozostać stabilne po zboczu zegarowym | Zakłócone dane, odwrócenie bitów |

| Zachwianie zegara | Różnica w czasie przybycia sygnału zegarowego do różnych chipów | Zmniejszony margines czasowy, niestabilność |

| Cykl roboczy | Stosunek czasu wysokiego do całkowitego okresu | Nierównowaga wydajności, zwiększone drgania |

W DDR4 i DDR5 magistrala poleceń i adresów często działa z niższą częstotliwością niż magistrala danych. Diagramy czasowe muszą uwzględniać sygnały strobu źródłowego synchronizowanego (DQS) towarzyszące danym, aby wskazać okna ważne.

2. Interfejsy wyświetlania (MIPI DSI)

Urządzenia mobilne wykorzystują interfejs szeregowy wyświetlania MIPI (DSI), aby połączyć procesor z ekranem. Ten interfejs wykorzystuje wysokoprzepustowe linie różnicowe.

- Tryb polecenia niskiego poziomu energii (LP):Tryb niskiego zużycia energii do przesyłania poleceń, opierający się na ścisłym czasie sekwencji wzbudzenia.

- Tryb wysokiej prędkości przesyłania danych (HS):Przesyłanie o wysokiej prędkości, w którym odzyskiwanie zegara odbywa się na strumieniu danych.

- Czas przełączenia:Czas wymagany do przełączenia się z trybu nadawania na tryb odbioru na tej samej linii.

Niezgodność w tych diagramach czasowych prowadzi do zjawisk na ekranie, migań lub całkowitej utraty sygnału wideo.

📡 Telekomunikacja: opóźnienie i przepustowość

W telekomunikacji czasoprzestrzeń jest synonimem opóźnienia. Czas dostarczania pakietów i synchronizacja w rozproszonych sieciach są kluczowe dla usług takich jak 5G i handel高频.

1. Sygnały PCIe

Standard Peripheral Component Interconnect Express (PCIe) jest szeroko stosowany do łączenia komponentów o wysokiej prędkości. Wykorzystuje szeregowe kanały z wbudowanymi zegarami lub zegarami synchronizowanymi z źródłem.

- Równoważenie:Integralność sygnału pogarsza się wraz z odległością. Diagramy czasowe pokazują, jak filtry równoważą straty.

- Nauka połączenia: Ciąg stanów z czasowym wyznaczeniem, aby ustalić prędkość połączenia i szerokość kanału.

- Sterowanie przepływem: Okna czasowe sterowania przepływem opartego na kredytach zapobiegają przepelnieniu buforów.

2. PHY Ethernet

Standardowy Ethernet opiera się na wspólnym zegarze lub odtworzeniu zegara. Ethernet Gigabit i wyższe wykorzystują kodowanie 8b/10b, aby zapewnić wystarczającą liczbę przejść do odtworzenia zegara.

- Okresy bezczynności: Zdefiniowane okna czasowe, w których nie wysyłany jest żaden dane, aby utrzymać synchronizację.

- Ogranicznik początku ramki: Określony wzorzec bitów oznaczający początek pakietu, wymagający dokładnego czasu wykrycia.

- Odstęp między pakietami: Obowiązkowy opóźnienie między pakietami, aby umożliwić ponowne uruchomienie sprzętu.

⚠️ Powszechne naruszenia czasowe i rozwiązania

Nawet przy starannym projekcie występują naruszenia czasowe. Identyfikacja przyczyny wymaga analizy diagramu czasowego, aby zobaczyć, gdzie sygnały odchylają się od oczekiwań.

1. Naruszenia czasu ustawienia

Występuje, gdy dane przychodzą zbyt późno, aby zostały uchwycione przez krawędź zegara.

- Przyczyny:Zbyt duża głębokość logiki, długie opóźnienia przewodów lub przesunięcie zegara.

- Rozwiązania:

- Wstaw rejestrzy pipeline, aby rozbić długie ścieżki.

- Optymalizuj syntezę logiki, aby zmniejszyć liczbę bramek.

- Dostosuj częstotliwość zegara, aby zapewnić więcej czasu.

2. Naruszenia czasu utrzymania

Występuje, gdy dane zmieniają się zbyt szybko po krawędzi zegara, nadpisując przechwyconą wartość.

- Przyczyny:Krótkie opóźnienia ścieżek, przesunięcie zegara (clock skew), gdy zegar przechwytywania przychodzi zbyt późno.

- Rozwiązania:

- Wstaw opóźnienia w ścieżce danych.

- Użyj technik przesunięcia czasu, aby wyrównać ścieżki.

- Upewnij się, że sieć dystrybucji zegara ma minimalne przesunięcie.

3. Przesunięcie zegara i drgania (jitter)

Przesunięcie zegara to różnica w czasie przybycia sygnału zegarowego na różnych rejestrach. Drgania (jitter) to krótkoterminowa zmienność krawędzi zegara.

- Skutki:Zmniejsza efektywne margines czasowy dostępny dla danych.

- Rozwiązania:

- Użyj generatorów zegara o małym jitterze.

- Projektuj zrównoważone drzewa zegarowe z przewodami o tej samej długości.

- Zaimplementuj pętle synchronizacji fazowej (PLL), aby oczyścić sygnały zegarowe.

✅ Najlepsze praktyki w implementacji

Osiągnięcie stabilnego czasowania wymaga systematycznego podejścia na całym etapie projektowania. Dokumentacja i weryfikacja są równie ważne jak sam obwód.

1. Wczesne określanie ograniczeń czasowych

Nie czekaj aż do fazy implementacji, by określić wymagania czasowe. Dokumentuj częstotliwości zegarów, opóźnienia wejściowe i wyjściowe w specyfikacji projektu. Zapewnia to, że wszyscy uczestnicy projektu zrozumieją granice systemu.

2. Użyj analizy statycznej czasu

Narzędzia analizy statycznej czasu (STA) obliczają najgorsze przypadki opóźnień bez symulacji każdej kombinacji wejściowej. Ta metoda jest efektywna i obejmuje wszystkie możliwe stany, zapewniając, że nie zostaną pominięte żadne naruszenia czasowe.

3. Weryfikacja poprzez symulację

Choć analiza statyczna czasu jest potężna, symulacja dynamiczna zapewnia widok zachowania sygnałów w określonych warunkach. Używaj symulacji do weryfikacji krytycznych ścieżek, szczególnie tych z logiką asynchroniczną lub złożonymi maszynami stanów.

4. Względy projektowania fizycznego

Układ fizyczny układu lub płytki bezpośrednio wpływa na czasowanie.

- Długość przewodu:Dłuższe przewody wprowadzają większą pojemność i opór, zwiększając opóźnienie.

- Zjawisko przekłucia (crosstalk):Sygnały sąsiednie mogą wywoływać szum, powodując fałszywe przejścia.

- Szum zasilania: Spadania napięcia mogą spowolnić szybkość przełączania bramek.

🛠️ Usuwanie awarii w scenariuszach z rzeczywistego świata

Gdy system nie spełnia wymagań czasowych, konieczna jest zorganizowana procedura diagnostyczna. Poniższe kroki przedstawiają logiczny sposób rozwiązywania problemów z czasem.

- Krok 1: Zidentyfikuj ścieżkę.Znajdź konkretną ścieżkę od rejestru do rejestru powodującą awarię. Spójrz do raportu czasowego na najbardziej ujemny czas przesunięcia (slack).

- Krok 2: Analiza przebiegów sygnałów.Użyj przeglądarki wykresów czasowych, aby zbadać rzeczywiste przejścia sygnałów. Porównaj je z wartościami oczekiwanymi.

- Krok 3: Sprawdź zegar.Zweryfikuj jakość sygnału zegara. Poszukaj drgań (jitter), zniekształceń cyklu roboczego lub zakłóceń.

- Krok 4: Przejrzyj ograniczenia.Upewnij się, że ograniczenia w pliku projektu odpowiadają rzeczywistości fizycznej sprzętu.

- Krok 5: Powtarzaj.Wprowadź zmiany w logice lub układzie, a następnie ponownie uruchom analizę czasową.

📊 Podsumowanie parametrów czasowych

Aby ułatwić szybkie odnalezienie informacji, przedstawiamy podsumowanie kluczowych parametrów czasowych stosowanych w różnych branżach.

| Parametr | Symbol | Typowa jednostka | Opis |

|---|---|---|---|

| Okres | Tc | ns | Czas między kolejnymi krawędziami zegara |

| Częstotliwość | Fc | Hz | Odwrotność okresu |

| Czas ustalenia | tsu | ns | Stabilizacja danych wymagana przed krawędzią zegara |

| Czas utrzymania | th | ns | Stabilizacja danych wymagana po krawędzi zegara |

| Opóźnienie propagacji | tpd | ns | Czas potrzebny sygnałowi na przejście przez logikę |

| Zeskok | Δt | ps | Różnica czasu przybycia zegara |

🔄 Zarządzanie projektami asynchronicznymi

Nie wszystkie systemy działają na jednym zegarze. Projektowanie asynchroniczne obejmuje przekazywanie danych między różnymi domenami zegarowymi. Oznacza to ryzyko metastabilności, gdy przerzutnik wchodzi w stan nieokreślony.

- Ciągi synchronizacji: Użyj synchronizatora wielostopniowego (zazwyczaj dwóch przerzutników), aby umożliwić zakończenie sygnału przed jego wykorzystaniem.

- Protokoły wymiany sygnałów: Zaimplementuj mechanizmy żądania-potwierdzenia, aby upewnić się, że odbiorca jest gotowy przed wysłaniem danych.

- Bufory FIFO: Użyj struktur pamięci First-In-First-Out, aby rozdzielić szybkości producenta i konsumenta.

Diagramy czasowe dla projektów asynchronicznych pokazują zależność między dwoma niezależnymi zegarami. Kluczem jest zapewnienie, że ścieżka danych ma wystarczająco dużo czasu na zakończenie przed tym, jak zegar odbiorczy ją próbuje odczytać.

🌟 Ostateczne rozważania

Diagramy czasowe są fundamentem weryfikacji systemów cyfrowych. Łączą abstrakcyjną logikę z rzeczywistością fizyczną. Zrozumienie subtelności czasu ustawienia, czasu utrzymania, zasobu zegara i drgań pozwala inżynierom projektować systemy odporno, wydajne i niezawodne.

Nie ma znaczenia, czy chodzi o systemy bezpieczeństwa w samochodach, urządzenia konsumenckie czy infrastrukturę telekomunikacyjną – zasady pozostają te same. Dokładność w czasie prowadzi do dokładności w działaniu. Ciągłe monitorowanie i przestrzeganie najlepszych praktyk zapewniają, że projekty będą funkcjonalne przez cały cykl życia. Wraz z postępem technologii i wzrostem prędkości, znaczenie szczegółowej analizy czasowej będzie tylko rosnąć.

Dla zespołów poszukujących poprawy jakości projektu, inwestowanie czasu w dokładne schematy czasowe i przepływy weryfikacji jest istotne. Zmniejsza to ryzyko, obniża koszty debugowania i zapewnia, że ostateczny produkt spełnia swoje specyfikacje. Dzięki odpowiednim narzędziom i metodologiom wyzwania związane z czasem stają się zarządzalnymi ograniczeniami, a nie przeszkodami.