工程溝通極度依賴視覺精確性。在討論系統互動、信號傳播或資料流時,一張結構良好的時序圖便成為通用語言。這些圖表能捕捉事件在時間上的關係,使工程師能有效診斷問題、驗證邏輯並記錄系統行為。然而,一張雜亂、模糊或比例不當的圖表,可能導致成本高昂的誤解。本指南概述了建立清晰圖表的必要標準,確保技術真實性得以傳達而不會產生混淆。

📊 時序圖基礎知識解析

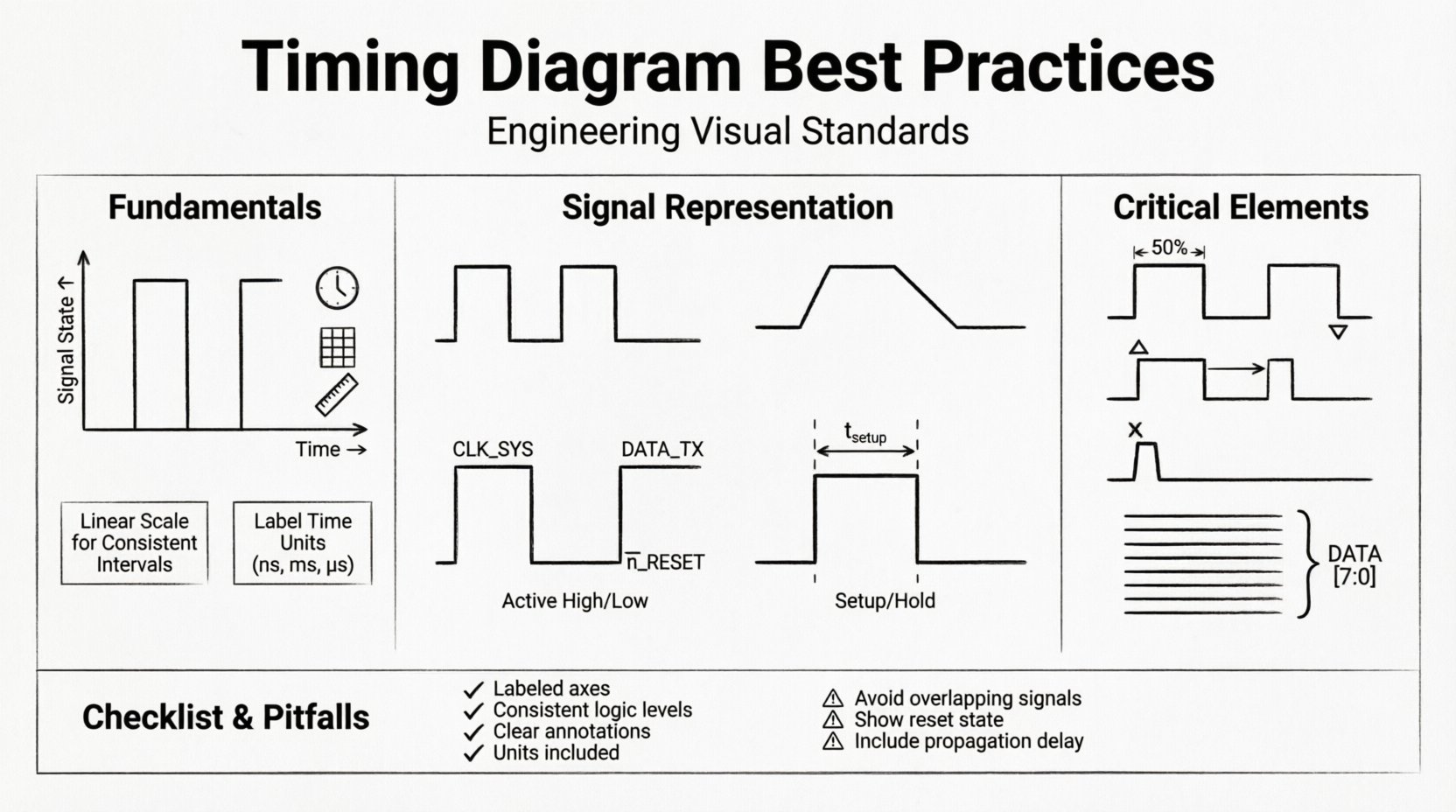

時序圖是信號隨時間變化的圖形化表示。它不僅僅是一張圖畫,更是一份規格說明。無論您是在處理硬體介面、嵌入式系統或軟體協定,其基本原理始終一致:時間水平流動,信號狀態則垂直繪製。在此情境下,清晰度並非奢侈品,而是確保安全與可靠性的必要條件。

在製作這些視覺圖表時,目標是降低讀者的認知負擔。讀者不應需要猜測時鐘從何處開始、哪條線代表資料,或電壓閾值為何。圖表中的每一項元素都必須具有明確用途。

- 時間軸: 水平方向代表時間的推進。根據所記錄的事件,可採用線性或對數方式。

- 訊號線: 垂直方向代表訊號的狀態,例如高/低、1/0 或電壓等級。

- 事件: 時間上的特定點,發生變化的時刻,例如邊緣、脈衝或資料傳輸。

📏 設定您的畫布與比例

清晰圖表的基礎是網格。若缺乏一致的比例,事件之間的關係將會扭曲。一張在某個縮放層級看起來正確的草圖,可能在另一個層級暴露關鍵的時序違規。

1. 定義時間比例

時間比例應根據系統中最快的事件來選擇。若您正在記錄微秒級的互動,以毫秒為單位繪製時間軸將會掩蓋細節。反之,若事件跨越數秒,使用微秒比例則會產生不必要的雜訊。務必在軸上清楚標示時間單位。

- 線性比例: 用於一致的間隔。這是大多數協定文件的標準。

- 對數比例: 極少使用,但當事件跨越數個數量級時(例如啟動延遲與處理時間)則為必要。

2. 網格線與參考點

網格線有助於眼睛追蹤圖表中的時間間隔。粗網格線應標示主要單位(例如 10ms),而細網格線則標示次要單位(例如 1ms)。這種視覺層次結構可防止讀者迷失方向。

確保垂直網格線與重要事件對齊。若時鐘邊緣恰好落在網格線上,將為讀取建立與保持時間提供自然的參考點。若事件代表真實世界的測量值,切勿強行使其符合網格;應調整網格或使用註解來顯示偏移量。

⚡ 準確呈現訊號

訊號的繪製方式決定了其被解讀的方式。上升沿表示從低電平轉為高電平,但該轉換的速率與形狀可能隱含關於訊號完整性的意義。

1. 訊號狀態與電平

明確定義何謂邏輯狀態。在數位邏輯中,通常為 0(低)與 1(高)。在類比或混合訊號情境中,則需使用電壓等級(例如 0V 至 5V)。使用不同的線條樣式來區分:

- 主動高: 當訊號線位於上層時,訊號為真。

- 主動低: 當訊號線位於下層時,訊號為真(通常以訊號名稱上方加一橫線表示)。

2. 邊緣表示

邊緣是圖示中最重要的部分。它們標示出狀態變化的確切時刻。對於理想的轉換,請使用尖銳且實線。如果需要表示物理上的上升速率或上升時間,應繪製為斜線,而非垂直的尖峰。

除非特別用於記錄雜訊或閃爍現象,否則應避免使用鋸齒狀線條。乾淨的線條表示穩定;鋸齒狀線條則暗示干擾。繪製線條形狀時應有明確的考量。

3. 信號命名規範

信號名稱不僅僅是標籤;它是一種定義。應避免使用如Signal_A或Wire_1之類的通用名稱。相反,應使用能描述功能的名稱,例如CLOCK_SYS或DATA_TX.

- 前置詞: 使用標準前置詞來標示信號類型(例如,

N代表負邏輯,CLK代表時鐘)。 - 大小寫:常數與信號使用大寫,變數則依情況使用混合大小寫。

- 一致性: 確保圖示上的名稱與程式碼或資料手冊中的名稱完全一致。

⏱️ 時鐘與同步

時鐘驅動同步系統的時序。錯誤地表示時鐘會使整個圖示失效。時鐘信號通常是讀者首先檢查的參考點。

1. 占空比與週期

除非系統明確要求變動時序,否則應以一致的占空比繪製時鐘信號。若占空比非50%,請標註高電平與低電平的持續時間。週期(一個完整週期的時間)應清楚標示。

對於變頻系統,不要假設線條長度不變即代表時間不變。若週期差異顯著,應分別標示每個週期。

2. 邊緣觸發

請標示系統是於上升沿(正向)還是下降沿(負向)觸發。可在邊緣處使用箭頭或小三角形。這對於理解資料何時被採樣至關重要。

- 上升沿:用一個小三角形指向上方標記。

- 下降沿:用一個小三角形指向下方標記。

3. 震盪與相位

在高速系統中,震盪(時間上的變化)是一個已知因素。如果你繪製的是理論上的理想情況,直線即可。如果你在記錄實際測量的行為,請使用陰影區域或多條軌跡來顯示波動範圍。多個時鐘之間的相位關係應明確標示。

🔄 處理資料轉換

資料信號通常比時鐘更為複雜,其變化取決於系統的狀態。正確記錄這些轉換需要關注資料與時鐘之間的關係。

1. 建立時間與保持時間

這些是確保可靠資料捕獲的關鍵限制條件。建立時間是指時鐘邊沿前資料必須穩定的時間長度。保持時間是指時鐘邊沿後資料必須保持穩定的時間長度。可將其視為相對於時鐘邊沿的時間窗。

繪製垂直虛線以標示建立時間與保持時間的範圍。以時間單位標示持續時間(例如,t_setup = 5ns)。這能直觀地顯示系統正常運作所擁有的餘裕。

2. 共振不穩定狀態

當信號跨越時鐘域時,可能產生共鳴不穩定狀態。這是一種信號既非完全高電平也非完全低電平的狀態。可使用虛線或時序窗中的特定陰影來表示。記錄此狀態可提醒讀者,該信號可能需要比平常更長的時間才能穩定。

3. 閃爍與雜訊

雜訊脈衝,稱為閃爍,可能導致邏輯錯誤。如果閃爍是已知問題,應繪製為窄脈衝,且未達到接收邏輯的最小脈衝寬度要求。不要隱藏這些異常現象;它們往往是間歇性故障的根本原因。

🏷️ 註解與標籤

圖表中的文字具有重要意義。過度堆疊文字會使圖表難以閱讀。標註不足則會導致含義模糊。應透過策略性佈局來取得平衡。

1. 文字定位

將文字放置在信號相關部分附近,但避免與信號線重疊。若信號線過於擁擠,無法直接在上方或下方放置文字,可使用引線(連接文字與信號的細線)。

2. 單位與符號

務必包含單位。時間單位應為秒、毫秒或納秒。電壓單位應為伏特。不要依賴讀者自行猜測。在顯示邏輯方程式時,應使用標準符號表示邏輯運算(例如,! 表示非運算,& 表示與運算)。若併列顯示邏輯方程式與時序圖,應使用標準符號。

3. 可讀性

字型大小至關重要。無論是印刷文件還是螢幕顯示,文字都必須在不放大情況下清晰可讀。若圖表較為複雜,可考慮拆分為多個視圖:一個高階概覽與特定事件的詳細特寫。

🚫 應避免的常見錯誤

即使是經驗豐富的工程師在繪製這些視覺圖時也會犯錯。了解常見錯誤可以節省數小時的除錯時間。

- 忽略傳播延遲: 訊號需要時間通過導線和邏輯閘傳輸。如果訊號在點 A 發生變化並到達點 B,請畫出延遲。點 B 處的垂直線表示瞬間傳輸,這在物理上是不可能的。

- 邏輯電平不一致: 確保高電平和低電平的定義在圖示中途不會改變。這會造成混淆且具有危險性。

- 訊號重疊: 如果兩個訊號必須交叉,請確保它們能清楚區分。若輸出媒介允許,可使用不同線條粗細或顏色。

- 遺漏重置狀態: 系統通常從特定狀態開始。在時鐘啟動前顯示初始狀態。這可避免對時間零點時訊號行為產生混淆。

🧠 高階考量

隨著系統變得更複雜,時序圖必須演進以處理多通道和非同步情境。

1. 多通道時序

處理匯流排(如資料匯流排)時,將相關訊號分組。使用括號表示上方的線條代表匯流排寬度(例如 “DATA[7:0])。顯示整個群組的轉換,以表示並行傳輸。

2. 非同步握手機制

並非所有系統都使用全局時鐘。握手機制依賴於請求與確認訊號。請清楚地繪製這些訊號,並用箭頭標示握手機制的方向。顯示系統暫停等待訊號到達的等待狀態。

3. 電源管理狀態

現代系統會進入低功耗模式。請在時序圖中標示這些轉換。訊號可能變低以表示睡眠模式,但時鐘可能停止或減慢。應將電源狀態與時序狀態一併記錄。

✅ 審查檢查清單

在最終確定圖示前,請逐一核對此檢查清單,以確保符合最佳實務。

| 檢查項目 | 標準 |

|---|---|

| 時間軸 | 比例是否為線性且標有單位? |

| 訊號名稱 | 所有訊號是否都以功能性和一致的方式命名? |

| 時鐘邊緣 | 上升/下降邊緣是否清楚標示? |

| 轉換 | 建立/保持時間是否可見並已標示? |

| 延遲 | 相關處是否包含傳播延遲? |

| 註解 | 文字是否清晰可讀且無重疊? |

| 單位 | 所有測量是否都附有單位(如 ns、V 等)? |

| 初始狀態 | 起始處是否顯示重置或空閒狀態? |

| 清晰度 | 同僚工程師能否在不提問題的情況下理解此圖? |

📝 文件編寫的最後想法

時序圖的品質反映了其背後工程品質。清晰的圖表促進硬體與軟體團隊之間的合作,減少除錯時間,並確保未來維護者能理解系統的行為。它是一種真理的工具,而不僅僅是圖示。

重視精確性勝於美觀。雖然漂亮的圖表令人愉悅,但正確的圖表才是不可或缺的。花時間核對測量值,標示每一項限制條件,並使你的視覺語言與技術規格保持一致。遵循這些做法,才能確保時序資訊在產品生命週期中始終準確無誤。

請記住,圖表是一份合約。它定義了系統的行為方式。當您畫出一條線時,其實是在對信號行為作出承諾。請確保這項承諾清晰、準確且無歧義。

採用這些標準能提升文件編寫的專業水準。這向你的團隊與利益相關者傳達出你重視可靠性與清晰度。在複雜的系統設計世界中,一張優秀的圖表往往就是成功發佈與持續問題之間的差別。

🔧 結論

製作有效的時序圖需要對佈局、標示與呈現方式採取嚴謹的方法。透過優先考慮清晰度、一致性與技術準確性,工程師能產出可作為開發與維護可靠參考的視覺圖表。遵循關於信號呈現、時鐘同步與註解的指引,以確保你的文件能經得起時間與複雜性的考驗。