在數位電子學與電腦工程中,理解訊號之間的時間關係是確保系統可靠性的基礎。時序圖作為描述這些關係的主要視覺語言,將訊號狀態對應到時間軸上,使工程師能夠觀察資料流、時鐘同步以及電路內可能的危險狀況。本指南探討波形分析中常見的結構元件、操作模式與關鍵情境。

無論是設計積體電路還是除錯嵌入式系統,能夠解讀並建立準確的時序表示都是核心能力。本文檔提供訊號互動方式、必須遵守的限制條件,以及驗證過程中常見的陷阱之技術概覽。

📐 時序圖的結構

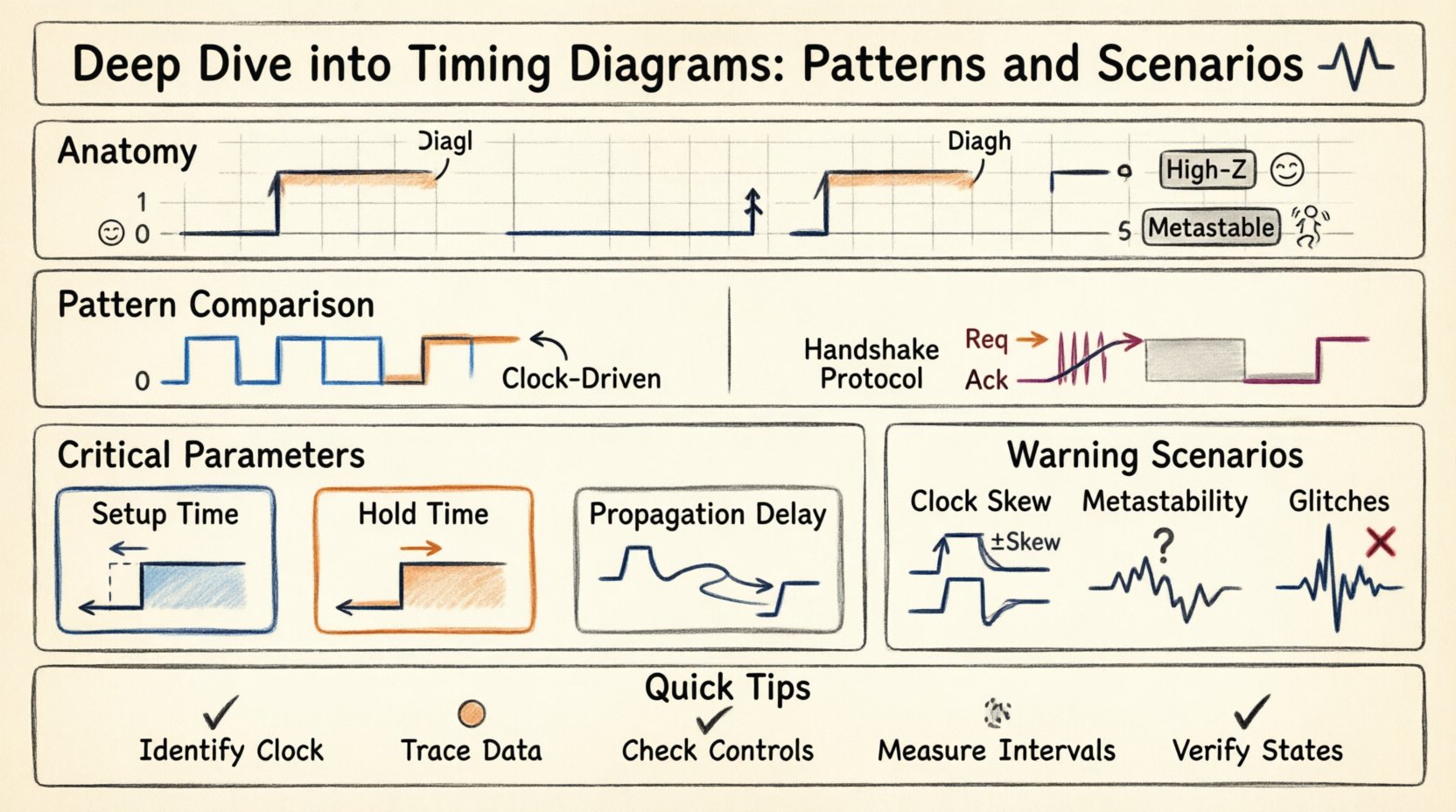

時序圖是一種圖形化表示,其中水平軸代表時間,垂直軸代表訊號電平。每一條水平線對應設計中的一個特定訊號或網路。理解這些元件是準確分析的第一步。

- 時間軸:通常從左向右水平運行。其形式可為線性或對數,取決於所觀察事件的規模。

- 訊號線:代表電壓電平的單獨波形。高電壓通常表示邏輯 1,低電壓則表示邏輯 0。

- 轉換:垂直線,表示狀態的變化,例如上升沿(0 到 1)或下降沿(1 到 0)。

- 標籤:文字註解,用以識別特定訊號、接腳或控制線。

- 標記:垂直虛線,通常用來標示特定事件,例如時鐘脈衝或重置觸發。

🔢 邏輯電平與狀態

數位訊號並非總是嚴格處於 0 或 1。在實際情境中,訊號可能處於未定義狀態或高阻抗狀態。完整的圖表應考慮這些變化。

- 邏輯高電平(1): 訊號被驅動至被識別為邏輯真值的電壓電平。

- 邏輯低電平(0): 訊號被驅動至被識別為邏輯假值的電壓電平。

- 高阻抗(High-Z): 訊號與驅動源斷開,實際上處於浮空狀態。這在三態緩衝器中很常見。

- 亞穩態(Metastable): 訊號既非高電平也非低電平的狀態,通常發生在異步轉換期間。

⚙️ 常見的時序模式

設計遵循可預測的模式以確保資料完整性。這些模式定義了資料相對於控制訊號的傳輸方式。識別這些模式有助於驗證設計是否符合規格要求。

📌 同步資料傳輸

同步設計依賴於全域時鐘訊號來協調動作。資料僅在特定時刻被採樣,通常是時鐘的上升沿或下降沿。

- 時鐘驅動: 所有狀態變更都與時鐘邊緣相關。

- 資料有效性: 資料必須在時鐘邊緣之前保持穩定,並在邊緣之後繼續保持穩定。

- 傳播: 時鐘邊緣與輸出變更之間存在延遲。

📌 異步握手

異步通訊不依賴共享時鐘,而是使用控制信號來指示資料何時準備就緒以及何時已被接收。

- 請求(Req): 發送方表示資料已可用。

- 確認(Ack): 接收方表示資料已被接受。

- 等待狀態: 發送方可能暫停,直到接收方準備就緒。

| 特性 | 同步模式 | 異步模式 |

|---|---|---|

| 協調 | 全域時鐘信號 | 控制握手信號 |

| 速度 | 通常較高 | 可變,取決於回應 |

| 複雜度 | 時鐘分佈網絡 | 協議邏輯 |

| 延遲 | 可預測 | 可變 |

⏱️ 關鍵時序參數

除了視覺線條之外,特定的數值限制定義了電路是否能正確運作。這些參數對於靜態時序分析至關重要,必須根據物理極限進行驗證。

🛑 建立時間

建立時間是指資料信號在時鐘邊緣之前必須保持穩定的最短時間。如果資料在時鐘邊緣附近變動過快,接收端的正反器可能無法正確捕捉到值。

- 測量: 從活躍的時鐘邊緣向後測量時間。

- 風險: 違反會導致錯誤的資料捕捉。

- 要求: 資料路徑延遲必須足夠長,以滿足建立時間視窗。

🛑 保持時間

保持時間是指資料信號在時鐘邊緣之後必須保持穩定的最短時間。這確保鎖存器有足夠時間鎖定輸入值。

- 測量: 從活躍的時鐘邊緣向前測量時間。

- 風險: 違反會導致亞穩態或錯誤資料的捕捉。

- 要求: 資料路徑延遲必須足夠短,以確保保持時間視窗的成立。

⚡ 傳播延遲

這是信號從邏輯閘的輸入傳播到輸出所需時間。其大小取決於負載電容和電晶體的內部電阻。

- tpd(高至低): 從 1 轉換到 0 所需的時間。

- tpd(低至高): 從 0 轉換到 1 所需的時間。

- 偏移: 平行路徑之間的延遲差異。

🚨 關鍵時序情境

某些情境會帶來重大挑戰,需要仔細分析。這些情況通常涉及不同時鐘域之間的互動,或硬體本身的物理限制。

🔄 時鐘偏移

時鐘偏移發生在時鐘信號以不同時間抵達不同元件時。這可能是由於佈線差異或物理距離造成的。

- 正偏移: 目標時鐘信號比源時鐘信號到達得更晚。

- 負偏移: 目標時鐘信號比源時鐘信號到達得更早。

- 影響: 可能有效減少建立時間餘量,或增加保持時間違規。

🌊 元穩定狀態

元穩定狀態是一種觸發器輸出既非高電平也非低電平的狀態。通常發生在建立時間或保持時間違規時,特別是在異步跨接處。

- 解決方式: 電路最終會轉換到穩定狀態,但所需時間是不可預測的。

- 修正方法: 使用同步器(多級觸發器)以降低失敗機率。

- 平均無故障時間(MTBF): 平均無故障時間是根據元穩定狀態的解決率計算得出的。

📉 閃爍

閃爍是信號中短暫的尖峰,可能被誤認為是有效的轉換。它們通常因不同路徑上的傳播延遲差異而產生。

- 原因: 路徑長度不等或競爭條件。

- 影響: 可能觸發下游邏輯中的非預期狀態變更。

- 緩解措施: 使用濾波邏輯,或確保時序閉合正確。

🔍 波形分析

檢視時序圖時,系統化的方法可確保不遺漏任何細節。工程師必須追蹤資料與控制信號的傳輸流程,以識別差異。

🔍 分步分析

- 識別時鐘: 找到主要時鐘信號。判斷它是上升沿觸發還是下降沿觸發。

- 追蹤資料路徑: 從源頭跟隨資料線到目的地。

- 檢查控制信號: 確認使能、重置和清除信號是否正確地被激活。

- 測量間隔: 計算特定事件之間的時間以驗證建立和保持要求。

- 驗證狀態轉換: 確保輸出狀態符合預期的邏輯功能。

🔍 讀取邊緣觸發

了解組件對信號邊緣的反應至關重要。

- 正邊緣觸發: 動作發生在從低電平轉換到高電平的瞬間。

- 負邊緣觸發: 動作發生在從高電平轉換到低電平的瞬間。

- 電平觸發: 只要信號保持在特定電平,動作就會持續發生。

🛠️ 文件編寫標準

清晰的文件編寫可確保其他工程師能理解設計。符號和標籤的一致性可防止調試或交接時產生誤解。

📝 標籤規範

- 信號名稱: 使用一致的命名規範(例如,

clk,rst_n,data_in). - 極性:明確標示低電平有效的信號,通常使用上劃線或後綴。

- 單位: 在時間軸上明確標示時間單位(ns、µs、ms)。

- 縮放: 確保時間比例適合所顯示的事件。

📝 視覺清晰度

- 間距: 儘可能避免線條重疊。

- 對比度: 為不同類型的訊號使用明顯不同的顏色或線條粗細。

- 註解: 加入註解以解釋複雜行為或特定限制。

- 網格: 使用網格背景以協助測量時間間隔。

🚧 問題排查流程

當設計未能滿足時序要求時,結構化的問題排查流程有助於找出根本原因。這包括根據實際物理限制來檢視圖表。

🚧 違反項識別

- 檢查建立時間: 資料相對於時鐘是否到達得太晚?

- 檢查保持時間: 資料是否在時鐘後過於迅速變更?

- 檢查時鐘頻率: 時鐘週期是否短於所需的最小值?

🚧 缓解策略

- 流水線暫存器: 插入額外的暫存器以切斷長的組合邏輯路徑。

- 時鐘門控: 減少活動以降低功耗,並可能改善時序。

- 插入緩衝器: 加入緩衝器以平衡平行路徑上的延遲。

- 時序約束: 定義錯誤路徑以排除不影響資料流的邏輯。

📈 設計最佳實務

在設計階段採用最佳實務可降低開發週期後期出現時序問題的可能性。主動規劃比被動修復更有效率。

- 統一介面:使用已知的通訊協定進行資料傳輸,以簡化時序驗證。

- 最小化非同步路徑:盡量減少非同步互動,以降低亞穩態風險。

- 記錄假設:在設計規格中明確說明時鐘頻率與電壓等級。

- 定期審查:在專案的每個主要里程碑階段進行時序審查。

🎯 關鍵概念總結

時序圖是用來視覺化數位系統時間行為的關鍵工具。它們能顯示資料與控制訊號隨時間的互動情形,並突顯如建立時間與保持時間等關鍵限制。透過理解這些圖表的結構,工程師可辨識模式、預測錯誤,並確保系統具備穩健的性能。

主要重點包括同步與非同步模式的區別、時鐘偏移管理的重要性,以及明確文件標準的必要性。遵循這些原則可促進可靠設計,並簡化驗證流程。

持續分析波形資料可確保設計始終維持在操作範圍內。隨著技術進步與時鐘頻率提升,時序分析所需的精確度變得更加關鍵。掌握這些概念,才能打造出穩定且高效率的數位架構。