在数字系统的复杂架构中,理解信号状态变化的精确时刻至关重要。时序图提供了信号随时间演变的视觉表示。它们是工程师、开发人员和设计师不可或缺的工具,用于验证组件之间的交互是否正确。如果没有这些视觉辅助工具,调试异步通信或验证时钟域就会变成一种猜测。本指南探讨了时序图在系统设计中的工作原理、优势和应用。

什么是时序图? ⚙️

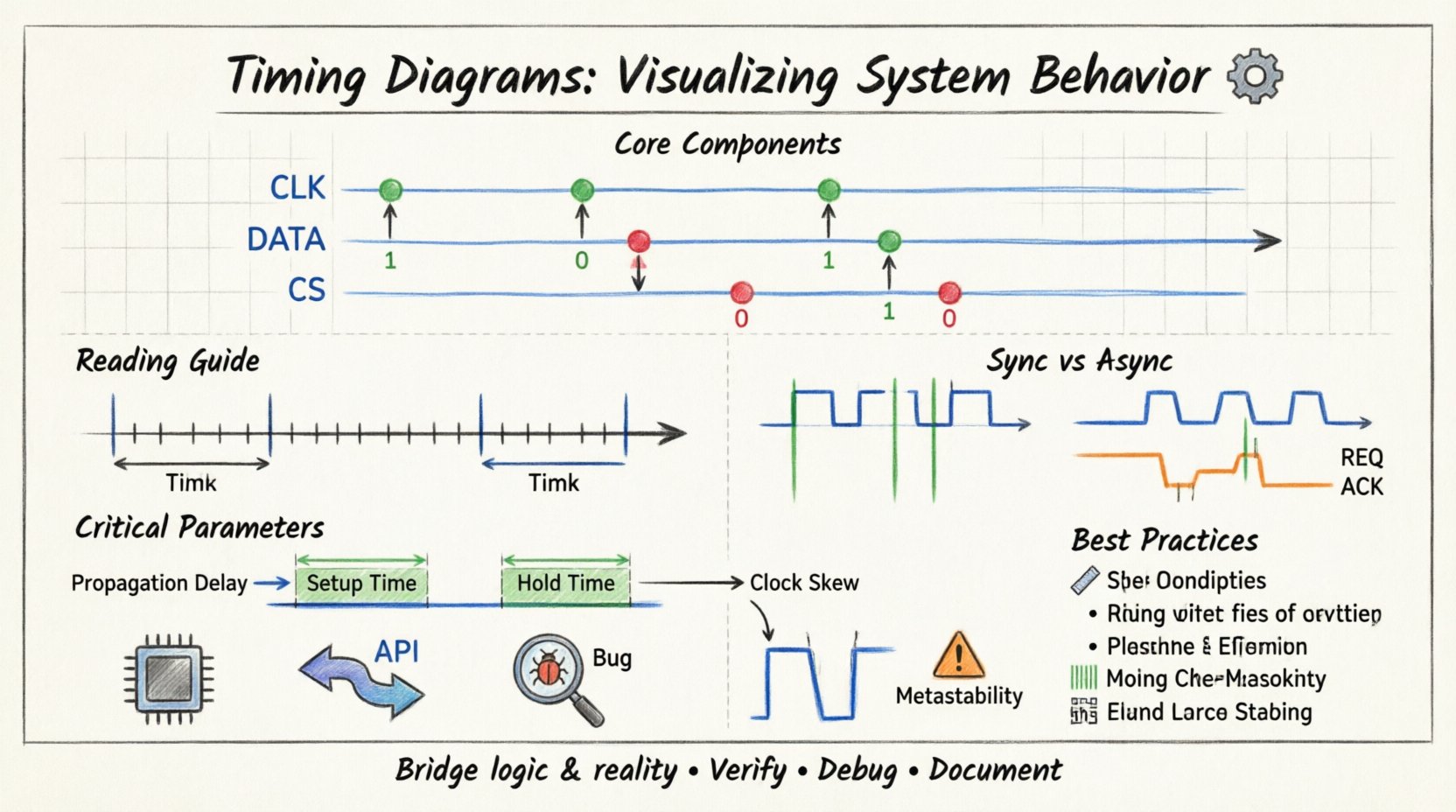

时序图是一种图表,用于展示信号在一段时间内的行为。它将信号的逻辑状态与时间轴对应起来。与显示物理连接的电路图不同,时序图关注的是事件之间的时序关系。它们可以回答诸如:信号A是否在信号B之前发生变化?时钟脉冲是否足够宽?数据需要多长时间才能稳定?等问题。

这些图表在以下方面至关重要:

- 验证硬件协议

- 记录软件逻辑交互

- 调试竞争条件

- 验证时钟与数据对齐

时序图的核心组成部分 🧩

要有效解读时序图,必须理解其基本构成要素。每个时序图都包含特定元素,用以传达系统运行的相关信息。

1. 时间轴 📏

横轴表示时间,通常从左向右流动。时间尺度可以是绝对的(纳秒、微秒)或相对的(时钟周期)。在同步系统中,时间通常被划分为与时钟边沿对应的离散步骤。

2. 信号线 📡

每条线代表一个特定的信号、导线或数据总线。这些线通常用名称标记,例如CLK, DATA, CS(芯片选择),或RST(复位)。线的垂直位置用于区分不同的信号,以避免混淆。

3. 逻辑电平 🟢🔴

信号通常处于离散状态。在数字逻辑中,这些状态为高电平(逻辑1)和低电平(逻辑0)。时序图展示了这些状态之间的转换。从低到高的转换称为上升沿,从高到低的转换称为下降沿。

4. 事件与转换 🔄

事件是信号状态发生变化的特定时刻。这些时刻通常用垂直线或箭头标记。重要事件包括时钟边沿、数据锁存和确认信号。这些事件之间的间距表示持续时间。

有效阅读时序图 👁️

阅读这些图表需要采用系统化的方法。错误理解事件的顺序可能导致设计缺陷。遵循以下原则可确保准确性。

- 从左到右: 始终从开始(左)到结束(右)阅读时间轴。这表示操作的时间顺序流程。

- 垂直对齐: 垂直对齐的事件同时发生。如果两个信号在完全相同的垂直线上发生变化,则它们是并发的。

- 持续时间: 信号状态的水平长度表示其保持该状态的时间长短。宽脉冲意味着持续时间更长。

- 依赖关系: 寻找因果关系。一个信号的变化通常会触发另一个信号。该图展示了这些触发之间的延迟。

同步系统与异步系统 🔄

时序图的差异显著取决于系统是同步还是异步。理解这一区别对于准确分析至关重要。

同步系统 ⏰

这些系统依赖于全局时钟信号。所有状态变化都发生在特定的时钟边沿(上升沿或下降沿)。图中会显示规律的时钟波形。只有在时钟允许时才会采样数据。这使得时序可预测,但引入了建立时间和保持时间等约束。

异步系统 🕰️

这些系统不依赖全局时钟。状态变化发生在输入信号发生变化时。这里的时序图看起来不那么规则。它们侧重于握手协议。一个信号必须先变高,然后另一个信号变高,再一起变低。这需要仔细分析延迟,以防止竞争条件。

时序分析中的关键参数 ⚙️

除了简单地画线之外,工程师还会分析特定参数以确保可靠性。这些参数定义了系统正常工作的窗口。

- 传播延迟: 信号通过一个元件从输入到输出所需的时间。该延迟会在逻辑门之间累积。

- 建立时间: 在时钟边沿之前,数据必须保持稳定的最短时间。如果数据变化太晚,触发器将无法正确捕获它。

- 保持时间: 在时钟边沿之后,数据必须保持稳定的最短时间。如果数据变化太快,当前值将丢失。

- 时钟偏移: 时钟信号在不同元件上到达时间的差异。高偏移可能导致建立时间或保持时间违规。

- 亚稳态: 一种触发器输出既非高电平也非低电平的状态。当建立时间或保持时间被违反时会发生这种情况。时序图有助于可视化亚稳态的风险。

在硬件和软件中的应用 🔌

时序图不仅限于硬件。它们在软件架构和协议设计中也得到广泛应用。

硬件设计

在硬件中,这些图用于验证总线协议。例如,验证读取选通脉冲激活之前地址总线是否稳定。它们确保内存访问时间与处理器时钟速度匹配。它们还用于分析信号转换期间的功耗尖峰。

软件与协议

在软件中,时序图用于映射API调用或消息交换。它们展示了服务之间请求和响应的顺序。这有助于识别分布式系统中的延迟问题。它们明确了多线程环境中的操作顺序。

常见陷阱与错误 🛑

如果不仔细操作,创建或阅读时序图可能会导致错误。了解常见错误有助于提高准确性。

- 忽略低电平有效: 许多信号使用低电平有效的逻辑(反相)。一条线下降到低电平可能表示信号处于激活状态。务必检查图例或标签。

- 假设瞬时转换: 实际信号具有上升时间和下降时间。理想图中显示为垂直线,但物理信号是斜坡状的。这种斜坡会影响信号完整性。

- 忽略毛刺: 未达到最小宽度要求的短脉冲可能引起误触发。这些通常被称为毛刺。

- 误解高阻态: 高阻态表示信号处于断开状态。在图中,这表现为虚线或特定符号。忽略这一点可能导致总线竞争错误。

- 时钟对齐错误: 假设所有时钟都相位对齐,但实际上并非如此。偏移可能导致数据被错误采样。

图示类型对比 📊

不同场景需要不同的可视化方法。尽管时序图功能强大,但并非唯一工具。

| 图示类型 | 主要关注点 | 最适合用于 |

|---|---|---|

| 时序图 | 时间和信号状态 | 验证时钟/数据关系 |

| 状态图 | 系统状态 | 定义逻辑流程和条件 |

| 顺序图 | 消息顺序 | 软件交互和API调用 |

| 电路原理图 | 物理连接 | 布线和元器件布局 |

| 波形查看器 | 实时信号 | 调试实际硬件行为 |

文档编写最佳实践 📝

为了使时序图对团队和未来参考更有用,请遵循这些最佳实践。清晰的文档可以减少歧义,加快调试速度。

- 为所有内容添加标签: 每条信号线都必须有明确的名称。避免使用像这样的通用标签Sig1.

- 包含单位: 在坐标轴上注明时间单位。我们查看的是毫秒还是时钟周期?

- 标记关键点: 明确突出显示建立时间和保持时间窗口。使用阴影或不同颜色来标记关键时序窗口。

- 保持整洁有序: 将相关的信号分组在一起。例如,所有控制信号放在上方,数据信号放在下方。

- 记录假设条件: 记录创建过程中所做的任何假设。例如,假设传播延迟为零或特定负载条件。

- 使用一致的符号: 使用标准符号表示上升沿、下降沿和高阻态。

创建图表的逐步指南 🛠️

从零开始创建时序图需要有条理的方法。遵循以下步骤以确保完整性。

- 识别信号: 列出交互中涉及的所有输入和输出信号。

- 确定顺序: 定义事件的顺序。是什么触发了这个过程?

- 设定时间尺度: 决定时间轴的粒度。

- 绘制时钟: 如果是同步的,首先绘制时钟信号。它将作为整个图表的基准。

- 添加数据: 将数据信号相对于时钟边沿进行绘制。

- 检查约束条件: 根据绘制的信号验证建立时间和保持时间。

- 审查: 逐条检查时间线,确保不存在逻辑断点。

时序在调试中的作用 🐞

当系统出现故障时,时序图通常是工程师首先查看的地方。它们有助于判断问题是逻辑性的还是时序性的。如果逻辑正确但时序错误,系统会间歇性失效。这通常比硬性逻辑错误更难复现。

调试场景包括:

- 数据损坏: 信号在被读取时发生改变。

- 错过中断: 中断信号过短,无法被检测到。

- 总线竞争: 两个设备同时驱动总线。

- 时钟域跨接: 信号在不同频率的时钟域之间移动,但未进行适当的同步。

理解数据宽度与对齐 📐

时序图还能可视化数据宽度。并行总线需要多条信号线。每条信号线必须同步跳变。对齐错误可能导致数据错误。图中展示了比特在时钟周期内的对齐方式。对于串行通信,时序图显示比特流,突出显示比特周期和采样点。

高级主题:抖动与噪声 📉

现实中的信号并非完美。抖动是指时钟边沿与其理想位置的偏差。噪声是信号电平的随机波动。时序图可以通过在边沿周围显示一个粗带而非尖锐线条来表示抖动,这表示不确定性。设计人员必须确保系统能够容忍这种不确定性。抖动带与建立/保持窗口之间的余量即为安全裕量。

与测试套件的集成 🧪

时序图不仅用于设计。它们还用于生成测试用例。自动化测试套件可以检查实际系统行为是否与图示一致。如果测量到的时序超出容差范围,测试即失败。这确保了硬件或软件在整个生命周期内都符合规范。

关于系统可视化的结论 🎯

时序图仍然是系统工程的基石。它们弥合了抽象逻辑与物理现实之间的鸿沟。通过可视化时间与信号的流动,工程师可以在故障发生前预测其出现。它们促进了软硬件团队之间的沟通。一张绘制良好的图表所传达的信息,远超过数页文字。随着系统速度加快、结构更复杂,对精确时序分析的需求日益增长。掌握这些图表是确保设计稳健可靠的关键。

请始终优先考虑清晰度和准确性。避免假设。验证每一次跳变。通过练习,阅读和绘制这些图表会逐渐成为设计过程中的直觉部分。它们是引导旅行者穿越数字逻辑领域的地图。