Zeitdiagramme sind essenzielle Werkzeuge zur Visualisierung des Verhaltens digitaler Signale über einen bestimmten Zeitraum. In der digitalen Elektronik und dem Bereich der Computertechnik ist das Verständnis der Wechselwirkungen zwischen Signalen entscheidend für Stabilität und Leistungsfähigkeit eines Systems. Diese Anleitung bietet eine detaillierte Untersuchung der Notation von Zeitdiagrammen, um sicherzustellen, dass Sie Wellenformen präzise lesen, erstellen und interpretieren können. Wir werden Signalpegel, Zeitachsen, Übergänge und kritische Zeitparameter untersuchen, ohne auf spezifische Softwarewerkzeuge zurückzugreifen.

🔍 Verständnis der zentralen Komponenten von Zeitdiagrammen

Grundlegend stellt ein Zeitdiagramm den logischen Zustand von Signalen im Verhältnis zur Zeit dar. Es dient als Bauplan dafür, wie Daten durch ein System fließen. Um diese Diagramme korrekt zu interpretieren, muss man die grundlegenden Achsen und Signalrepräsentationen verstehen.

- Horizontale Achse:Stellt die Zeit dar. Diese Achse verläuft von links nach rechts und zeigt die Reihenfolge der Ereignisse an.

- Vertikale Achse:Stellt den Logikzustand oder die Spannungshöhe einer bestimmten Signalleitung dar.

- Signalleitungen:Jede horizontale Linie entspricht einem bestimmten Draht, einer Netzeinheit oder einer logischen Variablen im Schaltkreis.

- Logische Pegel:Signale wechseln in der Regel zwischen zwei Zuständen, die üblicherweise als High und Low bezeichnet werden.

Beim Analysieren eines Zeitdiagramms sucht der Betrachter die Beziehung zwischen Änderungen eines Signals und Änderungen eines anderen Signals. Diese Beziehung bestimmt, ob Daten korrekt erfasst werden oder ob Fehler auftreten. Eine korrekte Notation stellt sicher, dass diese Beziehungen für Ingenieure, die das Design überprüfen, eindeutig sind.

⚡ Logische Pegel und Zustände von Signalen

Digitale Systeme arbeiten nach binären Prinzipien, aber die physische Darstellung variiert. Die Notation muss klar definieren, was einen logischen Eins- und einen logischen Null-Zustand darstellt. Falsche Interpretation dieser Pegel kann zu katastrophalen Fehlern im Design führen.

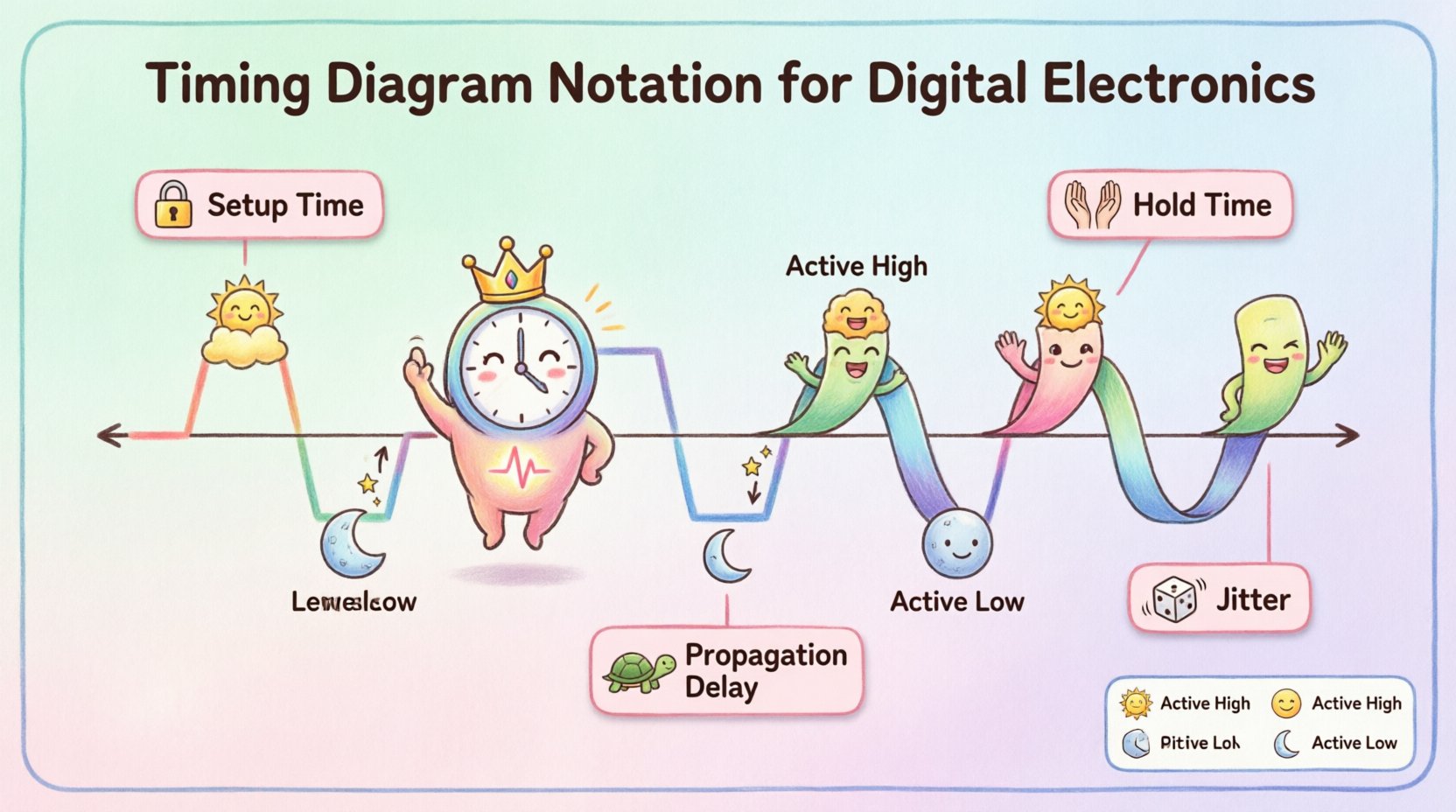

Aktiv-Hoch gegenüber aktiv-Niedrig

Signale können aktiv sein, wenn sie hoch sind, oder aktiv, wenn sie niedrig sind. Dieser Begriff ist für Steuersignale wie Zurücksetzungen oder Aktivierungen von entscheidender Bedeutung.

- Aktiv-Hoch:Das Signal erfüllt seine Funktion, wenn die Spannung hoch ist (Logik 1). Dies ist die Norm für die meisten Datensignale.

- Aktiv-Niedrig:Das Signal erfüllt seine Funktion, wenn die Spannung niedrig ist (Logik 0). Steuersignale verwenden diese Notation oft, um Rauschen zu reduzieren oder spezifischen Hardwareanforderungen zu entsprechen.

- Notationskennzeichen:Aktiv-niedrige Signale werden oft durch einen Strich über dem Namen oder eine kleine Kugel am Ende der Linie in Schaltplänen gekennzeichnet.

Logische Spannungsniveaus

Während Logik 0 und 1 abstrakt sind, stellt das Zeitdiagramm physikalische Spannungen dar. Die Notation sollte idealerweise die Spannungsschwellen angeben.

- Logik-Hoch:Typischerweise durch eine Spannung über einer bestimmten Schwelle dargestellt (z. B. 3,3 V oder 5 V).

- Logik-Niedrig:Typischerweise durch eine Spannung unter einer bestimmten Schwelle dargestellt (z. B. 0 V).

- Undefinierter Bereich: Der Bereich zwischen den hohen und niedrigen Schwellwerten, in dem der Signalzustand unbestimmt ist. Diagramme sollten sich in diesem Bereich nicht aufhalten.

⏱️ Zeitachse und Synchronisation

Die Darstellung der Zeit ist die zweitwichtigste Aspekt von Zeitdiagrammen. Im Gegensatz zur Spannung ist die Zeit kontinuierlich, aber digitale Signale ändern sich zu diskreten Zeitpunkten. Die Notation muss sowohl synchrone als auch asynchrone Ereignisse berücksichtigen.

Taktsignale

Die meisten digitalen Systeme stützen sich auf einen Takt, um die Abläufe zu synchronisieren. Das Taktsignal ist das Herzschlag des Systems.

- Periode: Die Zeit, die für eine vollständige Zyklus des Takts benötigt wird.

- Frequenz: Die Anzahl der Zyklen pro Sekunde, üblicherweise in Hertz gemessen.

- Tastverhältnis: Der Prozentsatz der Periode, in dem das Signal hoch ist.

- Notation: Taktsignale werden oft mit einem Rechteckwellenmuster gezeichnet.

Relativ vs. Absolut Zeit

Zeitdiagramme können relative oder absolute Zeit verwenden.

- Relative Zeit: Messungen erfolgen von einem Bezugspunkt aus, beispielsweise einer bestimmten Taktränder. Dies ist üblich bei der Analyse von Setup- und Hold-Zeiten.

- Absolute Zeit: Den Ereignissen werden spezifische Zeitstempel zugewiesen, was nützlich ist, um Kommunikationsprotokolle über lange Zeiträume zu debuggen.

Zeitskalen

Die Auswahl der richtigen Zeitskala ist entscheidend für Klarheit.

- Nanosekunden: Wird für Hochgeschwindigkeitslogik verwendet, bei der Signale schnell wechseln.

- Mikrosekunden: Wird für langsamere Peripherieinteraktionen verwendet.

- Millisekunden: Wird für die Stromversorgungssteuerung auf Systemebene oder für niedrige Frequenzevents verwendet.

🔄 Flankenübergänge und Notation

Der Moment, in dem ein Signal seinen Zustand ändert, ist genauso wichtig wie der Zustand selbst. Die Notation muss klar darstellen, wie und wann diese Übergänge stattfinden.

Ansteigende und abfallende Flanken

Kanten stellen den Übergang zwischen Logikpegeln dar.

- Ansteigende Kante: Der Übergang von Low nach High. Oft gekennzeichnet durch eine senkrechte Linie oder einen nach oben zeigenden Pfeil.

- Abfallende Kante: Der Übergang von High nach Low. Oft gekennzeichnet durch eine senkrechte Linie oder einen nach unten zeigenden Pfeil.

- Steigung: In idealisierten Diagrammen sind Kanten senkrecht. In realen Diagrammen haben Kanten eine Steigung, die Anstiegszeit oder Abfallzeit darstellt.

Übergangsverzögerungen

Signale schalten nicht sofort um. Die Notation muss Verzögerungen bei der Signalübertragung berücksichtigen.

- Ausbreitungsverzögerung: Die Zeit, die benötigt wird, damit eine Änderung am Eingang zu einer Änderung am Ausgang führt.

- Notation: Oft durch einen Abstand zwischen dem Eingangsübergang und dem Ausgangsübergang gekennzeichnet.

Glitches und Hazard

Unbeabsichtigte Übergänge können aufgrund von Schaltungsverzögerungen auftreten. Sie werden oft als kurze Spitzen dargestellt.

- Glitch: Ein kurzer Impuls, der nicht vorhanden sein sollte. Die Notation kann gestrichelte Linien oder unterschiedliche Farben verwenden.

- Hazard: Eine potenzielle Fehlausgabe aufgrund von Zeitverzögerungen.

📏 Kritische Zeitparameter

Bestimmte Parameter definieren die Zuverlässigkeit einer digitalen Schnittstelle. Dies sind die Messgrößen, die Ingenieure verwenden, um die Datenintegrität zu gewährleisten.

| Parameter | Beschreibung | Einheit |

|---|---|---|

| Setup-Zeit | Die Daten müssen vor dem Taktflankenauftritt stabil sein. | Zeit (ns) |

| Hold-Zeit | Die Daten müssen nach dem Taktflankenauftritt stabil bleiben. | Zeit (ns) |

| Ausbreitungsverzögerung | Zeit von der Eingabewechsel bis zur Ausgabewechsel. | Zeit (ns) |

| Clock-to-Q | Zeit von der Taktkante bis zur Ausgabewechsel. | Zeit (ns) |

| Jitter | Variation in der Zeitpunkte eines Signalrandes. | Zeit (ps/ns) |

Setup- und Haltezeiten

Dies sind die kritischsten Einschränkungen für synchrone Systeme.

- Setup-Zeit-Verletzung: Wenn die Daten zu nahe an der Taktkante wechseln, kann das System den korrekten Wert möglicherweise nicht erfassen.

- Haltezeit-Verletzung: Wenn die Daten zu früh nach der Taktkante wechseln, kann das System den Wert verlieren.

- Notation: Diese werden typischerweise als Zeitfenster um die Taktkante herum dargestellt, in denen die Datenleitung nicht wechseln darf.

Ausbreitungsverzögerung

Diese Verzögerung beeinflusst die maximale Frequenz des Systems.

- Hoch-zu-Niedrig:Zeit, die benötigt wird, damit ein Signal von Hoch nach Niedrig wechselt.

- Niedrig-zu-Hoch:Zeit, die benötigt wird, damit ein Signal von Niedrig nach Hoch wechselt.

- Notation: Oft dargestellt als horizontale Lücke zwischen Eingangs- und Ausgangssignalen.

🛠️ Steuersignale und aktive Zustände

Steuersignale steuern den Datenfluss. Ihre Notation muss deutlich anzeigen, wann sie aktiv sind.

| Signaltyp | Aktiver Zustand | Notationsbeispiel |

|---|---|---|

| Rücksetzen | Aktiv niedrig | Reset# oder Reset_bar |

| Aktivieren | Aktiv hoch | Aktivieren |

| Unterbrechung | Aktiv hoch oder niedrig | IRQ oder IRQ_bar |

| Chip-Auswahl | Aktiv niedrig | CS# |

Rücksetzsignale

Rücksetzsignale initialisieren das System. Sie können asynchron oder synchron sein.

- Asynchrones Rücksetzen:Wirkt sich unmittelbar aus, unabhängig vom Takt. Die Notation zeigt, dass die Rücksetzleitung zu jedem Zeitpunkt aktiv wird.

- Synchrones Rücksetzen:Wirkt sich nur am Taktflankenausgang aus. Die Notation zeigt, dass die Rücksetzleitung vor der Taktflanke aktiv ist.

Aktivierungssignale

Aktivierungssignale ermöglichen oder blockieren Operationen.

- Hochaktivierung:Die Operation erfolgt, wenn das Signal hoch ist.

- Niederaktivierung:Die Operation erfolgt, wenn das Signal niedrig ist.

📖 Lesen und Analysieren von Wellenformen

Das Lesen eines Zeitdiagramms erfordert einen systematischen Ansatz. Ingenieure sollten bestimmte Schritte befolgen, um Missdeutungen zu vermeiden.

Schritt-für-Schritt-Analyse

- Identifizieren Sie den Takt:Finden Sie die primäre Zeitreferenz. Alle synchronen Ereignisse beziehen sich darauf.

- Datenfluss verfolgen: Folgen Sie den Datenleitungen von der Quelle zum Ziel.

- Überprüfen Sie die Zeitfenster: Überprüfen Sie die Setup- und Haltezeiten bezüglich der Taktränder.

- Suchen Sie nach Anomalien: Identifizieren Sie Glitches, Spitzen oder unerwartete Übergänge.

- Überprüfen Sie die Logikpegel: Stellen Sie sicher, dass die aktiven Zustände den Komponentenspezifikationen entsprechen.

Häufige Missdeutungen

- Annahme einer sofortigen Änderung: Reale Signale haben Anstiegs- und Abfallzeiten. Die Annahme vertikaler Kanten kann Timing-Verstöße verbergen.

- Ignorieren asynchroner Signale: Steuersignale, die nicht getaktet sind, können jederzeit auftreten und müssen unabhängig geprüft werden.

- Falsches Lesen der aktiven Zustände: Die Verwechslung von Active High mit Active Low ist eine häufige Quelle von Designfehlern.

🚀 Fortgeschrittene Zeitverhaltensüberlegungen

Je schneller die Systeme werden, desto komplexer wird die Zeitverhaltensanalyse. Fortgeschrittene Notationen begegnen diesen Herausforderungen.

Metastabilität

Wenn ein Signal während des Setup- oder Haltefensters wechselt, kann die Ausgabe in einen metastabilen Zustand geraten.

- Definition: Das Signal stabilisiert sich auf einem mittleren Spannungsniveau.

- Notation: Oft dargestellt als Fragezeichen oder ein schraffierter Bereich zwischen High und Low.

- Auflösung: Das Signal löst sich letztendlich in High oder Low auf, aber die Dauer ist vorhersehbar.

Synchronisations-Verzögerung

Verschiedene Pfade können unterschiedliche Zeiten benötigen, um ein Ziel zu erreichen.

- Taktskew: Das Taktsignal trifft zu unterschiedlichen Zeiten bei verschiedenen Komponenten ein.

- Datenverzögerung: Datensignale treffen zu unterschiedlichen Zeiten an verschiedenen Zielen ein.

- Notation: Angezeigt als horizontale Verschiebung zwischen erwarteter und tatsächlicher Ankunftszeit.

Jitter

Jitter ist die Abweichung der Signalkante von ihrer idealen Position.

- Cycle-to-Cycle-Jitter: Variation zwischen einem Taktsignalzyklus und dem nächsten.

- Perioden-Jitter: Variation in der Gesamtdauer des Taktsignalzyklus.

- Notation: Oft dargestellt als schraffierter Bereich um die ideale Kantenposition.

📝 Best Practices für die Dokumentation

Klare Zeitdiagramme zu erstellen stellt sicher, dass andere Ihr Design verstehen können. Die Einhaltung bewährter Praktiken reduziert Mehrdeutigkeit.

- Konsistente Benennung: Verwenden Sie klare, eindeutige Namen für alle Signale. Vermeiden Sie generische Namen wie Signal1 oder Signal2.

- Standard-Symbole: Verwenden Sie Standardnotation für Kanten, Pegel und Verzögerungen, um die Branchenkompatibilität zu gewährleisten.

- Klare Zeitskalen: Beschriften Sie die Zeitachse explizit mit Einheiten (ns, µs, ms).

- Verwandte Signale gruppieren: Gruppieren Sie Signale, die zum selben Protokoll oder Subsystem gehören, zusammen.

- Kritische Zeiten hervorheben: Verwenden Sie fett gedruckte Linien oder Farben, um Setup- und Hold-Zeiten hervorzuheben.

- Legenden bereitstellen: Fügen Sie eine Legende für alle in dem Diagramm verwendeten benutzerdefinierten Symbole oder Abkürzungen hinzu.

🔚 Zusammenfassung der wichtigsten Erkenntnisse

Die Notation von Zeitdiagrammen ist eine grundlegende Fähigkeit für alle, die in der digitalen Entwicklung tätig sind. Durch das Verständnis der Kernkomponenten, Signalpegel und Zeitparameter können Ingenieure eine robuste Systemleistung sicherstellen. Eine korrekte Notation beseitigt Mehrdeutigkeit und verhindert kostspielige Designfehler. Denken Sie daran, sich auf Setup- und Hold-Zeiten zu konzentrieren, die aktiven Zustände klar zu definieren und reale Signalmerkmale wie Propagierungsverzögerung und Jitter zu berücksichtigen. Die Einhaltung dieser Richtlinien führt zu klaren, effektiven Dokumentationen.

Beim Erstellen oder Überprüfen dieser Diagramme sollten Sie immer die Logikpegel anhand der Hardware-Spezifikationen überprüfen. Stellen Sie sicher, dass die Zeitachse die tatsächliche Betriebsfrequenz des Systems widerspiegelt. Schließlich sollten Sie in Ihrer Notationsschrift über alle Dokumentationen hinweg konsistent bleiben, um die Zusammenarbeit zu erleichtern. Mit Übung wird das Interpretieren und Erstellen dieser Diagramme zu einem natürlichen Bestandteil des Entwurfsprozesses.

Abschließende Hinweise zur Umsetzung

Während dieses Leitfaden die theoretischen und notationalen Aspekte abdeckt, erfordert die praktische Umsetzung Aufmerksamkeit für die physikalische Ebene. Signalintegrität, Rauschabstand und Stromversorgung beeinflussen alle das Zeitverhalten. Kreuzen Sie die Zeitdiagramme immer mit Datenblättern und Simulationsergebnissen ab, um den Entwurf zu validieren. Kontinuierliches Lernen und die Einhaltung branchenüblicher Standards halten Ihre Entwürfe zuverlässig und effizient.