In der Welt der digitalen Elektronik und Systemgestaltung ist Zeit nicht nur eine Dimension; sie ist eine entscheidende Größe, die bestimmt, ob eine Schaltung korrekt funktioniert oder katastrophal versagt.Zeitdiagrammedienen als die visuelle Sprache, die Ingenieure verwenden, um zu kommunizieren, wie Signale im Laufe der Zeit reagieren. Egal, ob Sie eine Mikrocontroller-Schnittstelle entwerfen, einen Speicherbus debuggen oder Hochgeschwindigkeits-Datenübertragungen analysieren – das Verständnis dieser Diagramme ist unverzichtbar.

Dieser Leitfaden untersucht die Mechanik von Zeitdiagrammen und zerlegt komplexe Signalverhalten in verständliche Komponenten. Wir werden von grundlegenden Definitionen zu fortgeschrittenen Analysetechniken übergehen und sicherstellen, dass Sie die Werkzeuge besitzen, um Wellenformen präzise zu interpretieren.

🔍 Was ist ein Zeitdiagramm?

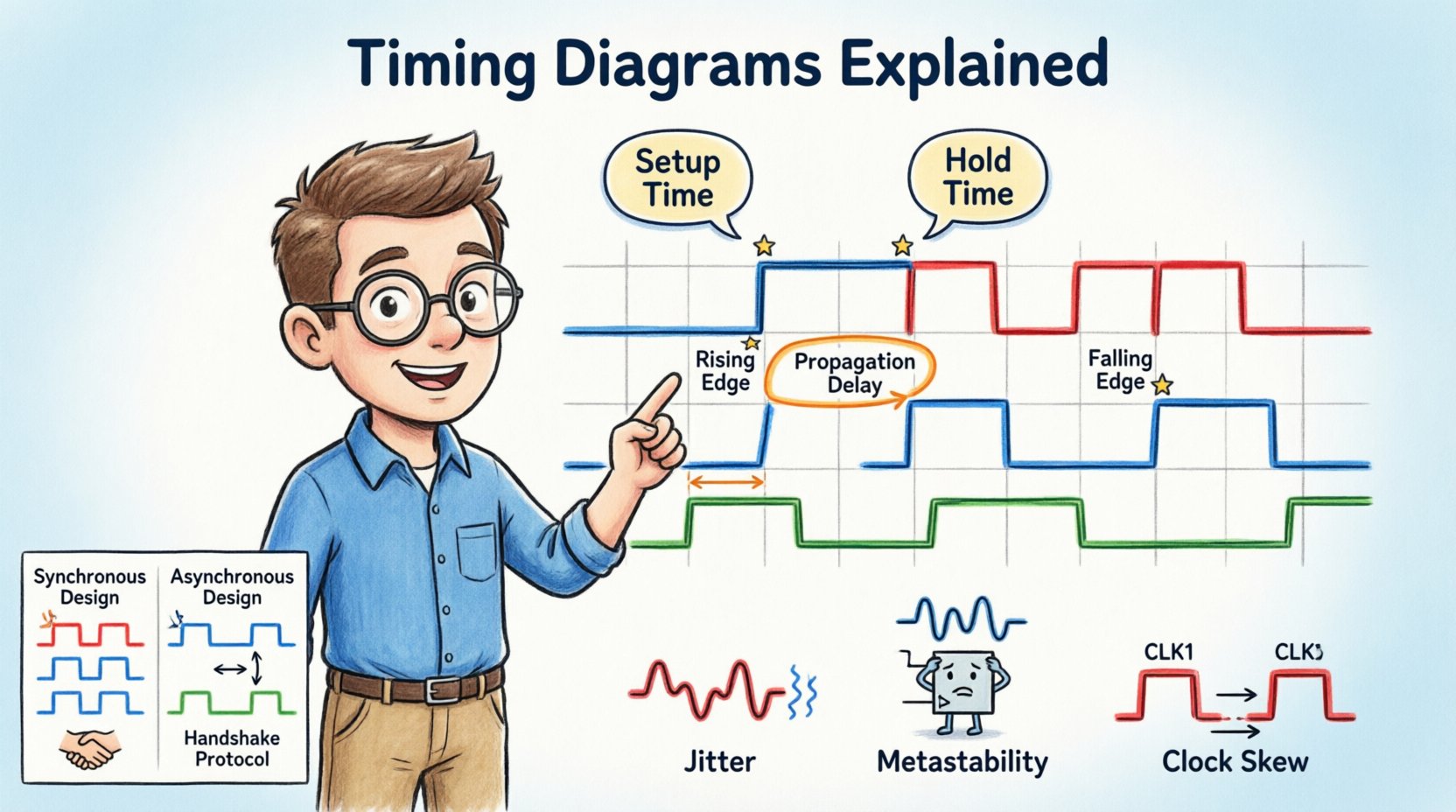

Ein Zeitdiagramm ist eine grafische Darstellung der Abfolge von Signaländerungen in einem digitalen System. Im Gegensatz zu einer Schaltungsskizze, die zeigt, wie Komponenten miteinander verbunden sind, zeigt ein Zeitdiagrammwanndiese Verbindungen ihren Zustand wechseln. Es kartiert die Signalaktivität entlang einer horizontalen Zeitachse und ermöglicht es Designern, sicherzustellen, dass Daten stabil sind, bevor ein Taktrand eintritt, oder dass Steuersignale zum richtigen Zeitpunkt aktiviert werden.

Diese Diagramme sind entscheidend für:

- Die Interaktion zwischen Hardware und Software zu überprüfen.

- Das Debuggen von Kommunikationsprotokollen.

- Sicherzustellen, dass Setup- und Hold-Zeit-Anforderungen erfüllt sind.

- Das Systemverhalten für zukünftige Wartungsarbeiten zu dokumentieren.

Ohne ein klares Verständnis der Zeitabläufe kann selbst eine logisch korrekte Schaltung aufgrund von Signalrennen oder Metastabilität versagen.

🛠️ Kernkomponenten eines Zeitdiagramms

Um ein Zeitdiagramm effektiv lesen zu können, müssen Sie seine grundlegenden Bausteine erkennen. Jeder Baustein trägt spezifische Informationen über den Zustand und die Strömung des digitalen Systems.

1. Die Zeitachse

Die horizontale Linie stellt die Fortschreitung der Zeit dar. Sie fließt normalerweise von links nach rechts. In detaillierten technischen Dokumenten kann diese Achse mit spezifischen Zeiteinheiten (Nanosekunden, Pikosekunden) oder Taktrunden markiert sein.

2. Signallinien

Vertikale Linien stellen einzelne Signale dar, wie Taktsignale, Datensysteme oder Steuersignale (z. B. Chip Select oder Lese/Schreib-Signale). Jede Linie entspricht einem bestimmten Knoten in der Schaltung.

3. Logische Zustände

Signale existieren typischerweise in einem von zwei Zuständen:

- Hoch (Logik 1 / VCC):Oft dargestellt durch eine Linie am oberen Rand der Signallinie.

- Niedrig (Logik 0 / GND):Dargestellt durch eine Linie am unteren Rand der Signallinie.

Einige Systeme verwendenaktiven NiedrigzustandLogik, bei der das Signal seine Funktion ausführt, wenn die Spannung niedrig ist. In Diagrammen wird dies oft durch einen Kreis am Signalnamen oder eine spezifische Kennzeichnung angezeigt.

4. Übergänge

Übergänge sind die Momente, in denen ein Signal von Hoch auf Niedrig oder von Niedrig auf Hoch wechselt.

- Anstiegsflanke:Übergang von Niedrig auf Hoch. Wichtig für die Auslösung von Ereignissen.

- Abfallflanke:Übergang von Hoch auf Niedrig. Wird für spezifische Steuersequenzen verwendet.

- Flankenauslösend:Das Signal wird nur während des Übergangs bewertet, nicht im stabilen Zustand.

⚙️ Wichtige Zeitparameter

Genauere digitale Gestaltung beruht auf der Quantifizierung der Beziehung zwischen Signalen. Die folgenden Parameter bilden die Grundlage der Zeitanalyse.

1. Propagationsverzögerung (tpd)

Dies ist die Zeit, die ein Signal benötigt, um vom Eingang eines Logikgatters oder Bauelements zum Ausgang zu gelangen. Kein Signal ändert sich sofort; physikalische Beschränkungen verursachen eine Verzögerung.

- Bedeutung: Wenn die Verzögerung zu lang ist, kann die nachfolgende Logik die Daten zu spät erhalten, was zu Fehlern führt.

- Messung: Gemessen vom 50%-Spannungspunkt des Eingangsübergangs zum 50%-Spannungspunkt des Ausgangsübergangs.

2. Vorbereitungszeit (tsu)

Die Vorbereitungszeit ist die Mindestdauer, während der Daten signale stabil sein müssenvordass ein Taktsignal eintrifft.

- Szenario: Wenn ein Flip-Flop Daten 5 Nanosekunden vor dem Taktimpuls bereit haben muss, ist das die Vorbereitungszeit.

- Verletzung: Wenn sich die Daten zu nahe am Taktsignal ändern, kann das System den Wert nicht korrekt erfassen.

3. Haltezeit (th)

Die Haltezeit ist die minimale Dauer, während der Daten Signale stabil bleiben müssennacheine Taktränderung eintritt.

- Szenario:Der Flip-Flop muss die Daten für eine kurze Zeit nach dem Auslöseereignis „sehen“, um sie sicher zu speichern.

- Verletzung:Wenn die Daten unmittelbar nach der Taktränderung wechseln, kann das Eingangssignal möglicherweise nicht korrekt gespeichert werden.

4. Taktschiefe

Taktschiefe tritt auf, wenn das Taktsignal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintrifft. Dies liegt oft an Längenunterschieden der Spuren auf einer Leiterplatte.

- Positive Schiefe:Der Takt trifft später am Zielort ein.

- Negative Schiefe:Der Takt trifft früher am Zielort ein.

5. Jitter

Jitter ist die kurzfristige Variation der bedeutenden Zeitpunkte eines Signals von ihren idealen Positionen in der Zeit. Er fügt der Zeitanalyse Unsicherheit hinzu.

📊 Vergleich: Synchrones vs. Asynchrones Design

Das Verständnis des Unterschieds zwischen diesen beiden Designphilosophien ist entscheidend, um Zeitdiagramme korrekt zu interpretieren.

| Merkmale | Synchrones Timing | Asynchrones Timing |

|---|---|---|

| Steuerungssignal | Verwendet einen globalen Takt | Verwendet Handshake-Signale |

| Vorhersagbarkeit | Sehr vorhersagbar | Variabel abhängig von der Last |

| Komplexität | Erfordert Taktverteilung | Erfordert komplexe Handshake-Logik |

| Stromverbrauch | Kann hoch sein (Taktwechsel) | Oft niedriger (aktivitätsabhängig) |

| Zeitdiagramm | Ausgerichtet an Taktflanken | Abhängig von der Vollendung des vorherigen Zustands |

🧐 Wie man Zeitdiagramme liest und analysiert

Die Analyse einer Wellenform erfordert einen systematischen Ansatz. Folgen Sie diesen Schritten, um sicherzustellen, dass Sie keine kritischen Details übersehen.

Schritt 1: Identifizieren Sie den Takt

Finden Sie das primäre Taktsignal. Dies ist normalerweise die Referenz für alle anderen Zeitabläufe. In synchronen Systemen sollte jede Datenumschaltung idealerweise an dieser Taktflanke ausgerichtet sein.

Schritt 2: Auf Störungen prüfen

Suchen Sie nach kurzen, unbeabsichtigten Impulsen (Störungen) an Signalleitungen. Diese können falsche Auslösevorgänge in Logikgattern verursachen. In einem sauberen Diagramm sollten Übergänge sauber sein, obwohl die Aufnahme in der Realität oft Rauschen zeigt.

Schritt 3: Setup- und Hold-Zeitfenster überprüfen

Zeichnen Sie imaginäre senkrechte Linien, die die Setup- und Hold-Zeitfenster um die aktive Taktflanke darstellen. Stellen Sie sicher, dass das Datensignal innerhalb dieser Bereiche stabil ist.

Schritt 4: Steuersignale prüfen

Stellen Sie sicher, dass Steuersignale wie Chip Select (CS) oder Enable (EN) während der gesamten Dauer des Datentransfers aktiv sind. Wenn ein Steuersignal abfällt, während noch Daten gesendet werden, tritt eine Beschädigung auf.

Schritt 5: Intervalle messen

Berechnen Sie die Zeit zwischen bestimmten Ereignissen. Zum Beispiel messen Sie die Verzögerung vom „Anforderungs“-Signal bis zum „Antwort“-Signal. Dies hilft dabei, die Leistung gegenüber Spezifikationen zu überprüfen.

🚀 Fortgeschrittene Konzepte der Zeitanalyse

Je schneller und komplexer die Systeme werden, desto weiter entwickeln sich einfache Zeitdiagramme zu anspruchsvollen Analyseanforderungen.

1. Metastabilität

Metastabilität tritt auf, wenn ein Flip-Flop eine Eingabe erhält, die die Setup- oder Hold-Zeitvorgaben verletzt. Anstatt sich klar auf eine 0 oder 1 einzustellen, geht die Ausgabe für eine vorhersehbar unbestimmte Dauer in einen undefinierten Zustand über.

- Ursache:Tritt oft auf, wenn asynchrone Signale zwischen Taktbereichen wechseln.

- Minderung:Verwenden Sie Synchronisierketten (mehrere Flip-Flops in Reihe), um die Wahrscheinlichkeit der Metastabilität zu reduzieren.

- Visuell:In einem Zeitdiagramm sieht dies aus wie ein Signal, das oszilliert oder ungewöhnlich lange braucht, um sich zu stabilisieren.

2. Setup- und Hold-Zeit-Budgets

Ingenieure berechnen ein Zeitbudget, um sicherzustellen, dass das System mit maximaler Frequenz arbeitet. Dazu werden alle Verzögerungen (Leitung, Gatter, Taktschiefe) von der Taktperiode abgezogen.

Wenn die Gesamtverzögerung die verfügbare Zeit überschreitet, muss die maximale Betriebsfrequenz reduziert werden.

3. Taktsynchronisation bei Hochgeschwindigkeitsschnittstellen

Schnittstellen wie DDR-Speicher oder PCIe erfordern eine extrem präzise Taktsynchronisation. Diese Diagramme enthalten oft:

- Augendiagramme: Eine Überlagerung vieler Signalübergänge zur Visualisierung der Signalqualität.

- Duty-Cycle-Verzerrung: Sicherstellen, dass die Hoch- und Niedrigzeiten ausgeglichen sind.

- Phasenabstimmung: Sicherstellen, dass Daten und Taktsignal über mehrere Bits hinweg synchron ankommen.

4. Zustände der Stromversorgungssteuerung

Moderne Geräte gehen in Energiesparmodi über. Taktsynchronisationsdiagramme müssen die Wachaufzeit berücksichtigen. Zum Beispiel muss ein Signal, das die Stromversorgung eines Peripheriegeräts aktiviert, vor dem Zeitpunkt erfolgen, zu dem das Gerät Daten empfangen kann.

📝 Best Practices für die Dokumentation

Klare Dokumentation verhindert Fehler während der Entwicklung und Fehlersuche. Halten Sie sich an diese Standards, wenn Sie Taktsynchronisationsdiagramme erstellen oder überprüfen.

- Konsistente Skalierung: Verwenden Sie konsistente Zeitskalen über verwandte Diagramme hinweg, um eine einfache Vergleichbarkeit zu ermöglichen.

- Klare Beschriftungen: Jedes Signal muss mit seiner Funktion und Logikpolarität beschriftet werden (z. B.

RESET#für aktiv niedrig). - Zoom-Ebenen: Bieten Sie sowohl eine Übersicht auf hoher Ebene als auch eine vergrößerte Ansicht kritischer Übergänge (wie Setup-/Hold-Zeitfenster).

- Farbcodierung: Verwenden Sie Farben, um verschiedene Spannungsdomänen oder Taktsignale zu unterscheiden (z. B. Rot für Takt, Blau für Daten).

- Versionskontrolle: Taktsynchronisationsanforderungen ändern sich. Stellen Sie sicher, dass die Diagramme entsprechend der Hardwareversion verwaltet werden.

🛠️ Häufige Fehlerquellen und Fehlerbehebung

Sogar erfahrene Ingenieure stoßen auf Taktsynchronisationsprobleme. Hier sind häufige Szenarien und deren Lösungsansätze.

Fehlerquelle 1: Ignorieren der Spurverzögerung

Leiterbahnen auf der Leiterplatte haben eine physische Länge, die eine Verzögerung verursacht. Bei hohen Frequenzen kann eine Länge von wenigen Zentimetern einer Taktschwingung entsprechen.

- Lösung: Berücksichtigen Sie die Spuränge in Ihren Zeitbudgetberechnungen.

Fallstrick 2: Schwankende Eingänge

Nicht angeschlossene Eingänge können auf eine mittlere Spannung schwanken und Oscillationen verursachen.

- Lösung: Stellen Sie sicher, dass alle Eingänge definierte Pull-up- oder Pull-down-Widerstände haben.

Fallstrick 3: Rennbedingungen

Wenn zwei Signale gleichzeitig wechseln, bestimmt die Reihenfolge ihres Eintreffens das Ergebnis.

- Lösung: Verwenden Sie Synchronisationslogik oder Zustandsmaschinen, um Ereignisse zu sequenzieren.

Fallstrick 4: Überschwingen und Unterschwingen

Signalreflexionen können dazu führen, dass Spannungen die Versorgungsspannungen überschreiten (Überschwingen) oder unter Masse fallen (Unterschwingen).

- Lösung: Implementieren Sie geeignete Abschlusswiderstände und Impedanzanpassung.

🔗 Praxisanwendungen

Zeitdiagramme werden in verschiedenen Bereichen der Ingenieurwissenschaft angewendet.

1. Speicher-Schnittstellen

DRAM und SDRAM erfordern strenge Zeitabläufe für Lese-/Schreibvorgänge. Die CAS-Latenz und die RAS-zu-CAS-Zeitverzögerung sind kritische Parameter, die in diesen Diagrammen dargestellt werden.

2. Mikrocontroller-Kommunikation

Protokolle wie I2C, SPI und UART beruhen auf spezifischen zeitlichen Beziehungen zwischen Takt- und Datenleitungen. Beispielsweise muss in I2C die Datenleitung stabil sein, während der Takt hoch ist.

3. Reihenfolge der Stromversorgung

Komplexe Systeme erfordern, dass die Versorgungsspannungen in einer bestimmten Reihenfolge eingeschaltet werden. Zeitdiagramme stellen sicher, dass die Kernspannung stabil ist, bevor die I/O-Spannung angelegt wird.

🎯 Zusammenfassung der wichtigsten Erkenntnisse

Die Beherrschung von Zeitdiagrammen erfordert Geduld und Sorgfalt. Die folgenden Punkte fassen das wesentliche Wissen für eine effektive Gestaltung und Analyse zusammen.

- Zeit ist entscheidend: Digitale Logik beruht auf präzisen zeitlichen Beziehungen zwischen Signalen.

- Setup- und Hold-Zeit: Dies sind die beiden häufigsten Einschränkungen, die die maximale Betriebsgeschwindigkeit bestimmen.

- Visuelle Überprüfung: Diagramme ermöglichen es Ihnen, potenzielle Konflikte zu erkennen, bevor die Hardware gebaut wird.

- Der Kontext ist wichtig: Berücksichtigen Sie stets die physische Umgebung (Leiterplatte, Temperatur, Spannung), die die Signalverzögerung beeinflusst.

- Standardisierung:Verwenden Sie standardisierte Symbole und Notationen, um die Klarheit der Kommunikation innerhalb von Teams zu gewährleisten.

Durch die Anwendung dieser Prinzipien stellen Sie sicher, dass Ihre digitalen Systeme robust, zuverlässig und leistungsstark sind. Die Fähigkeit, diese Diagramme zu interpretieren und zu erstellen, ist eine grundlegende Fähigkeit, die funktionale Designs von solchen unterscheidet, die im Feld versagen.

📈 Vorwärts blicken

Mit fortschreitender Technologie werden die Zeitbedingungen enger. Moderne Systeme arbeiten mit Gigahertz-Geschwindigkeiten, bei denen Nanosekunden von entscheidender Bedeutung sind. Kontinuierliches Lernen im Bereich Signalintegrität und Timing-Closure ist für Ingenieure, die an Spitzenhardware arbeiten, unerlässlich.

Beginnen Sie mit der Analyse bestehender Schaltpläne und ihrer entsprechenden Zeitdiagramme. Üben Sie das Messen von Intervallen und das Erkennen von Verstößen. Im Laufe der Zeit werden die Muster intuitiv, sodass Sie Probleme vorhersehen können, bevor sie physisch auftreten.