En electrónica digital e ingeniería de computadoras, comprender la relación temporal entre las señales es fundamental para la confiabilidad del sistema. Un diagrama de tiempo sirve como el lenguaje visual principal para describir estas relaciones. Representa los estados de las señales en función de un eje temporal, permitiendo a los ingenieros visualizar el flujo de datos, la sincronización del reloj y posibles riesgos dentro de un circuito. Esta guía explora los elementos estructurales, los patrones operativos y los escenarios críticos encontrados en el análisis de ondas.

Ya sea que se esté diseñando circuitos integrados o depurando sistemas embebidos, la capacidad de interpretar y crear representaciones temporales precisas es una competencia fundamental. Este documento proporciona una visión técnica de cómo interactúan las señales, las restricciones que deben cumplir y los errores comunes que se encuentran durante la verificación.

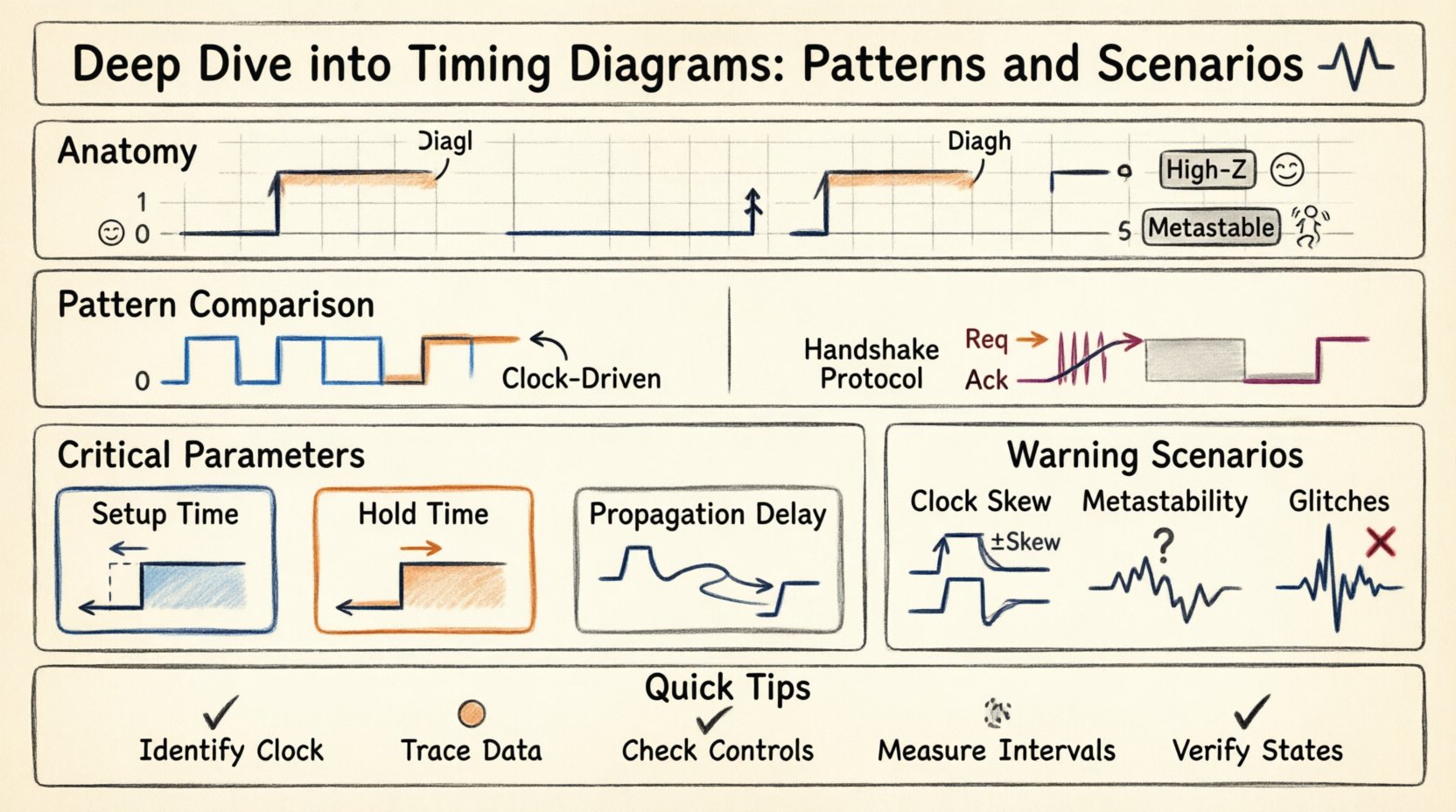

📐 Anatomía de un diagrama de tiempo

Un diagrama de tiempo es una representación gráfica en la que el eje horizontal representa el tiempo y el eje vertical representa los niveles de señal. Cada línea horizontal corresponde a una señal o red específica dentro del diseño. Comprender los componentes es el primer paso hacia un análisis preciso.

- Eje del tiempo:Normalmente se extiende horizontalmente de izquierda a derecha. Puede ser lineal o logarítmico, dependiendo de la escala de los eventos que se observan.

- Líneas de señal:Trazos individuales que representan niveles de voltaje. Un voltaje alto denota típicamente lógica 1, mientras que un voltaje bajo denota lógica 0.

- Transiciones:Líneas verticales que indican un cambio de estado, como una transición ascendente (0 a 1) o descendente (1 a 0).

- Etiquetas:Anotaciones de texto que identifican señales específicas, pines o líneas de control.

- Marcadores:Líneas verticales punteadas que a menudo se usan para indicar eventos específicos, como un pulso de reloj o un disparador de reinicio.

🔢 Niveles y estados lógicos

Las señales digitales no siempre existen estrictamente en 0 o 1. En escenarios prácticos, las señales pueden encontrarse en estados indefinidos o en estados de alta impedancia. Un diagrama completo debe tener en cuenta estas variaciones.

- Nivel lógico alto (1):La señal se impulsa a un nivel de voltaje reconocido como verdadero lógico.

- Nivel lógico bajo (0):La señal se impulsa a un nivel de voltaje reconocido como falso lógico.

- Alta-Z:La señal está desconectada del conductor, flotando efectivamente. Esto es común en los búferes de tres estados.

- Metastable:Un estado en el que la señal no es ni alta ni baja, que a menudo ocurre durante transiciones asíncronas.

⚙️ Patrones temporales comunes

Los diseños siguen patrones predecibles para garantizar la integridad de los datos. Estos patrones definen cómo se mueve la data en relación con las señales de control. Reconocer estos patrones ayuda a verificar que un diseño cumpla con sus especificaciones.

📌 Transferencia de datos síncrona

Los diseños síncronos dependen de una señal de reloj global para coordinar las acciones. Los datos solo se muestrean en momentos específicos, típicamente en el borde ascendente o descendente del reloj.

- Controlado por reloj: Todos los cambios de estado ocurren en relación con el borde del reloj.

- Validez de los datos:Los datos deben ser estables antes del borde del reloj y permanecer estables después de él.

- Propagación:Existe un retardo entre el borde del reloj y el momento en que cambia la salida.

📌 Handshake asíncrono

La comunicación asíncrona no depende de un reloj compartido. En su lugar, utiliza señales de control para indicar cuándo los datos están listos y cuándo han sido recibidos.

- Solicitud (Req):El emisor indica que los datos están disponibles.

- Confirmación (Ack):El receptor indica que los datos han sido aceptados.

- Estados de espera:El emisor puede pausar hasta que el receptor esté listo.

| Característica | Patrón síncrono | Patrón asíncrono |

|---|---|---|

| Coordinación | Señal de reloj global | Señales de handshake de control |

| Velocidad | Generalmente más alta | Variable, dependiente de la respuesta |

| Complejidad | Red de distribución de reloj | Lógica de protocolo |

| Latencia | Predecible | Variable |

⏱️ Parámetros críticos de temporización

Más allá de las líneas visuales, restricciones numéricas específicas definen si un circuito funcionará correctamente. Estos parámetros son críticos para el análisis de temporización estático y deben verificarse contra límites físicos.

🛑 Tiempo de preparación

El tiempo de preparación es la cantidad mínima de tiempo durante la cual la señal de datos debe mantenerse estable antes del borde del reloj. Si los datos cambian demasiado cerca del borde del reloj, el flip-flop receptor podría no capturar el valor correcto.

- Medición:Medido desde el borde activo del reloj hacia atrás en el tiempo.

- Riesgo:La violación conduce a una captura incorrecta de los datos.

- Requisito:El retardo en el camino de datos debe ser lo suficientemente largo para cumplir con la ventana de preparación.

🛑 Tiempo de retención

El tiempo de retención es la cantidad mínima de tiempo durante la cual la señal de datos debe mantenerse estable después del borde del reloj. Esto asegura que el latch tenga suficiente tiempo para fijar el valor de entrada.

- Medición:Medido desde el borde activo del reloj hacia adelante en el tiempo.

- Riesgo:La violación conduce a metastabilidad o captura de datos incorrectos.

- Requisito:El retardo en el camino de datos debe ser lo suficientemente corto para permitir la ventana de retención.

⚡ Retardo de propagación

Este es el tiempo que tarda una señal en viajar desde la entrada de una puerta lógica hasta su salida. Varía según la capacitancia de carga y la resistencia interna del transistor.

- tpd (Alto a Bajo):Tiempo para transicionar de 1 a 0.

- tpd (Bajo a Alto):Tiempo para transicionar de 0 a 1.

- Desviación:Diferencias en el retardo entre caminos paralelos.

🚨 Escenarios críticos de temporización

Algunos escenarios presentan desafíos importantes que requieren un análisis cuidadoso. Estas situaciones a menudo implican interacciones entre diferentes dominios de reloj o limitaciones físicas del hardware.

🔄 Atraso de reloj

El atraso de reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Esto puede ocurrir debido a diferencias en la ruta de señalización o a distancias físicas.

- Atraso positivo: La señal de reloj de destino llega más tarde que la señal de reloj de origen.

- Atraso negativo: La señal de reloj de destino llega antes que la señal de reloj de origen.

- Impacto: Puede reducir efectivamente los márgenes de tiempo de configuración o aumentar las violaciones de tiempo de retención.

🌊 Metastabilidad

La metastabilidad es un estado en el que la salida de un flip-flop no es ni alta ni baja. Suele ocurrir cuando se violan los tiempos de configuración o retención, especialmente en cruces asíncronos.

- Resolución: El circuito finalmente se resuelve en un estado estable, pero el tiempo que tarda es impredecible.

- Solución: Utilice sincronizadores (flip-flops de múltiples etapas) para reducir la probabilidad de fallo.

- MTBF: El tiempo medio entre fallos se calcula en función de las tasas de resolución de la metastabilidad.

📉 Ruidos

Los ruidos son picos de corta duración en la señal que pueden confundirse con transiciones válidas. A menudo ocurren debido a diferencias en los tiempos de propagación a lo largo de diferentes caminos.

- Causas:Longitudes de camino desiguales o condiciones de carrera.

- Efecto: Puede provocar cambios de estado no deseados en la lógica de salida.

- Mitigación: Utilice lógica de filtrado o asegúrese de un cierre de tiempo adecuado.

🔍 Análisis de formas de onda

Al revisar un diagrama de tiempos, un enfoque sistemático garantiza que no se omita ningún detalle. Los ingenieros deben rastrear el flujo de señales de datos y de control para identificar discrepancias.

🔍 Análisis paso a paso

- Identifique el reloj: Localice la señal de reloj principal. Determine si está activada por flanco ascendente o descendente.

- Rastree las rutas de datos: Siga las líneas de datos desde la fuente hasta el destino.

- Verifique las señales de control:Verifique que las habilitaciones, reinicios y borrados se activen correctamente.

- Mida los intervalos:Calcule el tiempo entre eventos específicos para verificar los requisitos de configuración y retención.

- Verifique las transiciones de estado:Asegúrese de que el estado de salida coincida con la función lógica esperada.

🔍 Lectura de desencadenadores de borde

Comprender cómo reacciona un componente ante los bordes de señal es fundamental.

- Desencadenado por borde positivo: La acción ocurre en la transición de bajo a alto.

- Desencadenado por borde negativo: La acción ocurre en la transición de alto a bajo.

- Desencadenado por nivel: La acción ocurre mientras la señal permanezca en un nivel específico.

🛠️ Normas de documentación

Una documentación clara garantiza que los diseños sean comprendidos por otros ingenieros. La consistencia en la notación y la etiquetación evita malentendidos durante la depuración o la transferencia.

📝 Convenciones de etiquetado

- Nombres de señal:Utilice convenciones de nombrado consistentes (por ejemplo,

clk,rst_n,data_in). - Polaridad:Indique claramente las señales activas-bajo, a menudo con una barra o sufijo.

- Unidades:Indique claramente las unidades de tiempo (ns, µs, ms) en el eje del tiempo.

- Escalado:Asegúrese de que la escala de tiempo sea adecuada para los eventos mostrados.

📝 Claridad visual

- Espaciado:Evite líneas superpuestas siempre que sea posible.

- Contraste:Utilice colores distintos o grosores de línea para diferentes tipos de señales.

- Anotaciones:Agregue notas que expliquen comportamientos complejos o restricciones específicas.

- Cuadrícula:Utilice un fondo de cuadrícula para ayudar a medir intervalos de tiempo.

🚧 Flujo de resolución de problemas

Cuando un diseño no cumple con los requisitos de tiempo, un proceso estructurado de resolución de problemas ayuda a aislar la causa raíz. Esto implica examinar el diagrama frente a las restricciones físicas.

🚧 Identificación de violaciones

- Verifique el tiempo de preparación:¿La data está llegando demasiado tarde en relación con el reloj?

- Verifique el tiempo de retención:¿La data está cambiando demasiado pronto después del reloj?

- Verifique la frecuencia del reloj:¿El período del reloj es más corto que el mínimo requerido?

🚧 Estrategias de mitigación

- Registros de pipeline:Inserte registros adicionales para romper caminos combinacionales largos.

- Gating de reloj:Reduzca la actividad para reducir el consumo de energía y posiblemente mejorar el tiempo.

- Inserción de búferes:Agregue búferes para equilibrar los retrasos en caminos paralelos.

- Restricciones de tiempo:Defina caminos falsos para excluir lógica que no afecta el flujo de datos.

📈 Mejores prácticas para el diseño

Adoptar buenas prácticas durante la fase de diseño reduce la probabilidad de problemas de temporización más adelante en el ciclo de desarrollo. La planificación proactiva es más eficiente que la corrección reactiva.

- Estandarizar interfaces:Utilice protocolos conocidos para la transferencia de datos para simplificar la verificación de temporización.

- Minimizar rutas asíncronas:Mantenga las interacciones asíncronas al mínimo para reducir los riesgos de metastabilidad.

- Documentar supuestos:Indique claramente las frecuencias de reloj y los niveles de voltaje en las especificaciones del diseño.

- Revisar regularmente:Realice revisiones de temporización en cada hito importante del proyecto.

🎯 Resumen de los conceptos clave

Los diagramas de temporización son herramientas esenciales para visualizar el comportamiento temporal de los sistemas digitales. Revelan cómo interactúan las señales de datos y de control con el tiempo, destacando restricciones críticas como los tiempos de setup y hold. Al comprender la anatomía de estos diagramas, los ingenieros pueden identificar patrones, predecir errores y garantizar un rendimiento robusto del sistema.

Los puntos clave incluyen la distinción entre patrones síncronos y asíncronos, la importancia de la gestión del desfase de reloj y la necesidad de estándares claros de documentación. Adherirse a estos principios facilita el diseño confiable y simplifica el proceso de verificación.

El análisis continuo de los datos de onda garantiza que los diseños permanezcan dentro de los límites operativos. A medida que la tecnología avanza y aumentan las velocidades de reloj, la precisión requerida en el análisis de temporización se vuelve aún más crítica. Dominar estos conceptos permite la creación de arquitecturas digitales estables y de alto rendimiento.