Dans le paysage complexe de la conception matérielle numérique, la clarté est primordiale. Les ingénieurs et les concepteurs s’appuient sur des représentations visuelles pour communiquer le comportement des signaux au fil du temps. Le diagramme temporel constitue l’un des outils les plus essentiels à cet effet. Il transforme la logique abstraite en un calendrier visuel, révélant la danse entre les états haut et bas à travers divers composants. Toutefois, à mesure que les systèmes gagnent en complexité, ces diagrammes peuvent devenir accablants. Ce guide explore une stratégie modulaire pour décomposer et analyser efficacement les diagrammes temporels, garantissant précision et fiabilité dans la vérification du matériel.

Comprendre le flux des signaux de données et de contrôle est essentiel pour éviter les défaillances fonctionnelles. Que vous conceviez une interface de microcontrôleur ou un protocole de communication à haute vitesse, la capacité à lire et à créer ces diagrammes distingue une conception solide d’une fragile. En adoptant une perspective structurée et modulaire, les équipes peuvent gérer la complexité et réduire le risque de violations temporelles.

Comprendre les bases des diagrammes temporels ⏱️

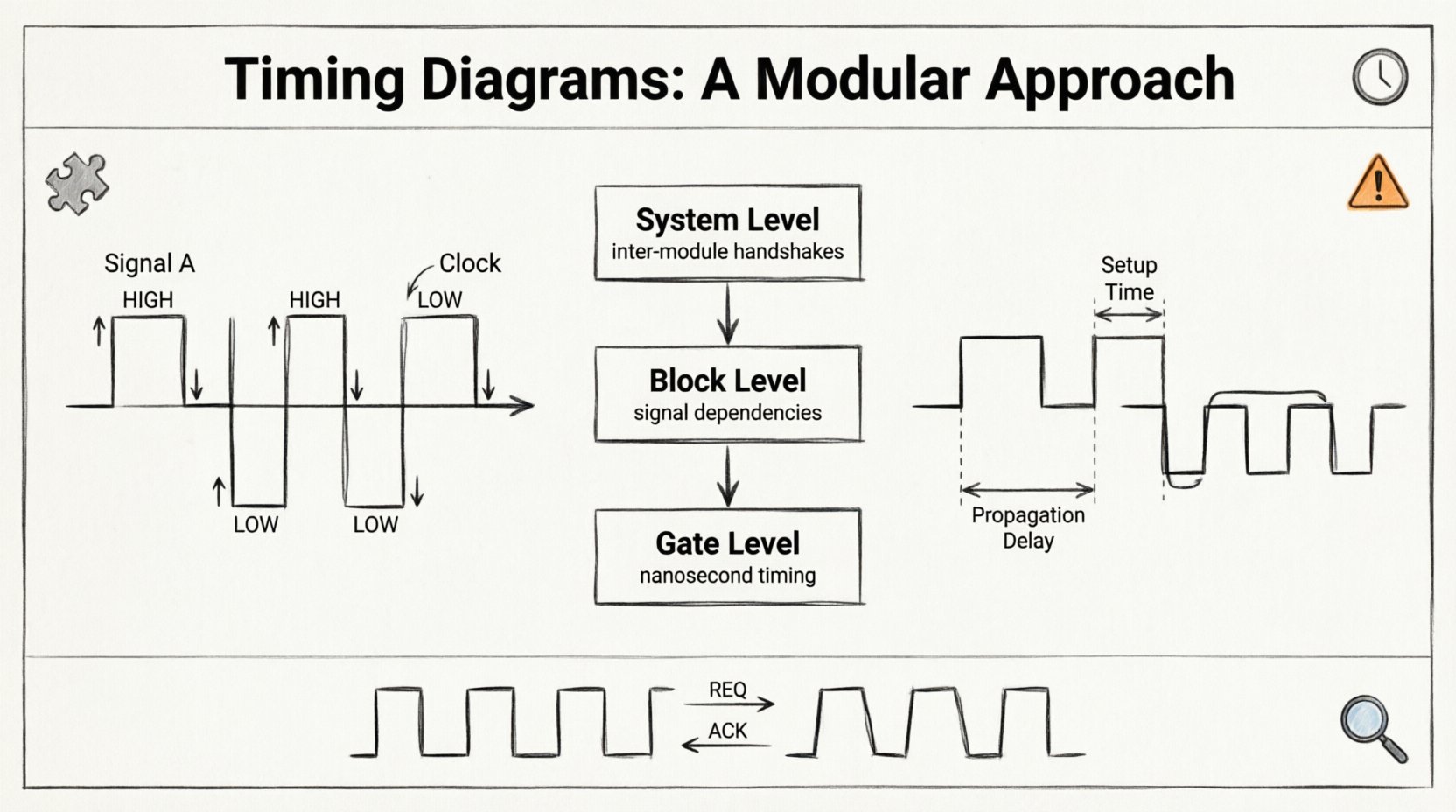

Un diagramme temporel est une représentation graphique du changement d’état des signaux au fil du temps. Il représente le temps sur l’axe horizontal et les états des signaux sur l’axe vertical. Ce format visuel permet aux ingénieurs de vérifier les relations entre différents signaux au sein d’un circuit numérique. L’objectif principal est de garantir que les données sont stables et valides au moment où elles sont échantillonnées par le composant récepteur.

Plusieurs éléments clés constituent la base de tout diagramme temporel :

- Lignes de signaux :Les lignes horizontales représentent des fils individuels ou des bus transportant des signaux spécifiques tels que l’horloge, les données ou le contrôle.

- Axe du temps :La progression horizontale indique le passage du temps, souvent marqué en nanosecondes ou en cycles d’horloge.

- Niveaux logiques :Les signaux sont généralement binaires, représentés par Haut (1) ou Bas (0). Parfois, des états indéfinis ou des états d’impédance élevée sont également affichés.

- Transitions :Les lignes verticales indiquent le moment où un signal passe d’un état à un autre, comme les fronts montants ou descendants.

- Annotations :Les étiquettes textuelles définissent souvent des contraintes spécifiques, des délais ou des blocs fonctionnels au sein du diagramme.

Sans une compréhension claire de ces bases, l’interprétation des interactions complexes devient difficile. Un diagramme temporel n’est pas simplement un dessin ; c’est un contrat entre l’émetteur et le récepteur. Il fixe les règles selon lesquelles les données doivent circuler pour être traitées correctement.

La stratégie modulaire pour les conceptions complexes 🧩

Les systèmes numériques modernes sont rarement simples. Ils se composent de plusieurs sous-systèmes, chacun ayant ses propres exigences temporelles. Tenter de représenter l’ensemble du système dans un seul diagramme conduit souvent à un encombrement et à la confusion. Une approche modulaire décompose la conception en morceaux gérables. Cette méthode améliore la lisibilité et simplifie le processus de débogage.

Pourquoi la modularité est importante

Décomposer un système en modules permet aux concepteurs de se concentrer sur des interfaces spécifiques sans se perdre dans le bruit de l’ensemble de l’architecture. Lorsqu’une violation temporelle se produit, un diagramme modulaire facilite l’isolement de la source du problème. Il réduit la charge cognitive et favorise la collaboration entre différentes équipes d’ingénieurs travaillant sur des blocs distincts.

Les avantages de cette approche incluent :

- Isolement des problèmes :Les problèmes peuvent être identifiés dans un bloc spécifique plutôt que dans l’ensemble du système.

- Réutilisabilité :Les schémas temporels standardisés pour les modules courants peuvent être réutilisés sur différents projets.

- Évolutivité :De nouvelles fonctionnalités peuvent être ajoutées sous forme de nouveaux modules sans devoir redessiner l’ensemble du diagramme.

- Efficacité de l’équipe :Des équipes différentes peuvent travailler simultanément sur leurs diagrammes temporels respectifs.

Définition des limites des modules

Pour mettre en œuvre efficacement cette stratégie, des limites claires doivent être établies. Chaque module doit avoir des entrées et des sorties définies. Le diagramme de temporisation d’un seul module doit se concentrer sur les signaux traversant cette limite. Les détails internes peuvent être abstraits, sauf s’ils ont un impact direct sur le temporisation de l’interface.

| Niveau du module | Zone d’attention | Granularité des détails |

|---|---|---|

| Niveau système | Communication entre modules | Séquences de handshake de haut niveau |

| Niveau bloc | Chemins internes de données | Dépendances spécifiques des signaux |

| Niveau porte | Retards de propagation | Temporisation exacte en nanosecondes |

En organisant les diagrammes selon ces niveaux, les ingénieurs peuvent maintenir une hiérarchie claire des informations. Cette structure garantit que le niveau de détail approprié est disponible à la bonne étape du processus de conception.

Décodage des états et des transitions des signaux 📊

Une fois la structure modulaire en place, la prochaine étape consiste à analyser les signaux spécifiques. Tous les signaux ne se comportent pas de la même manière. Certains sont continus, tandis que d’autres sont déclenchés par front. Comprendre la nature de chaque signal est essentiel pour la construction précise des diagrammes.

Les catégories courantes de signaux incluent :

- Signaux d’horloge : Le battement du système. Ce sont des signaux périodiques qui provoquent des changements d’état. Ils ont généralement des exigences strictes en fréquence et en rapport cyclique.

- Signaux de données : L’information réelle qui est transférée. Ils doivent être stables pendant des fenêtres spécifiques par rapport à l’horloge.

- Signaux de contrôle : Des signaux qui activent ou désactivent une fonctionnalité, tels que Chip Select ou Enable.

- Signaux de réinitialisation : Des signaux d’initialisation qui obligent le système à entrer dans un état connu.

Les transitions sur ces lignes sont critiques. Un front montant déclenche souvent une action, tandis qu’un front descendant peut la terminer. Dans les systèmes asynchrones, la relation entre ces fronts est moins prévisible, ce qui nécessite une analyse plus détaillée.

Visualisation du retard de propagation

Aucun signal ne change instantanément. Les limitations physiques causent un retard de propagation. Quand un signal quitte un composant, il faut du temps pour parcourir le câble et arriver au composant suivant. Les diagrammes de temporisation doivent tenir compte de cette latence. Si un diagramme montre un signal qui change à l’instant T, le récepteur ne le verra peut-être pas avant T + Δt.

Ignorer le retard de propagation peut entraîner des erreurs importantes en simulation et en implémentation. Les ingénieurs doivent modéliser ces retards pour garantir que les temps de préparation et de maintien sont respectés sur toute la longueur du chemin.

Contraintes de temporisation critiques expliquées ⚠️

La cause la plus fréquente de défaillance dans la conception numérique est la violation de temporisation. Ces violations se produisent lorsque les signaux ne respectent pas les fenêtres de stabilité requises. Deux contraintes principales régissent ce comportement : le temps de setup et le temps de hold.

Temps de setup

Le temps de setup est la durée minimale pendant laquelle les données doivent rester stables avant l’edge actif de l’horloge. Si les données arrivent trop tard, le bascule peut ne pas capturer la bonne valeur. Cette contrainte est essentielle pour déterminer la fréquence maximale de fonctionnement d’un système. Si la période d’horloge est plus courte que le délai de propagation plus le temps de setup, le système échouera.

Les points clés à considérer pour le temps de setup incluent :

- Une analyse du chemin le plus long est nécessaire pour identifier le pire des cas.

- Les variations de procédé, de tension et de température affectent le délai.

- Le jitter d’horloge peut réduire la fenêtre de setup disponible.

Temps de hold

Le temps de hold est la durée minimale pendant laquelle les données doivent rester stables après l’edge actif de l’horloge. Si les données changent trop tôt, la bascule peut capturer une valeur incorrecte ou entrer dans un état métastable. Contrairement au temps de setup, le temps de hold est indépendant de la fréquence d’horloge. Il dépend du délai interne du composant et du chemin externe.

Les violations de temps de hold sont souvent plus difficiles à corriger car elles ne peuvent pas être résolues en ralentissant l’horloge. En revanche, elles nécessitent d’ajouter un délai au chemin des données ou de réviser la logique.

Résumé des contraintes de temporisation

| Contrainte | Définition | Impact sur la fréquence | Méthode de résolution |

|---|---|---|---|

| Temps de setup | Stable avant l’edge d’horloge | Limite la fréquence maximale | Optimiser le chemin logique |

| Temps de hold | Stable après l’edge d’horloge | Indépendant de la fréquence | Ajouter un délai de tampon |

| Délai de propagation | Temps de parcours à travers la logique | Affecte les deux | Optimisation du circuit |

Péchés courants et violations 🚫

Même avec une approche modulaire, des erreurs peuvent s’infiltrer. Reconnaître les pièges courants aide à les prévenir pendant la phase de conception. Plusieurs types de violations sont fréquemment rencontrés lors de la vérification matérielle.

- Métastabilité :Surviens lorsque un signal change exactement au moment de l’edge d’horloge. La sortie du bascule devient imprévisible. Cela est fréquent lors du passage entre des domaines d’horloge.

- Glitches :Pulsations courtes et involontaires causées par des différences dans les chemins logiques. Elles peuvent déclencher des changements d’état erronés.

- Désynchronisation d’horloge :Lorsque le signal d’horloge arrive à différents composants à des moments différents. Cela réduit la fenêtre de temps effective.

- Conditions de course :Lorsque le résultat dépend de la séquence des événements, ce qui est imprévisible dans les conceptions asynchrones.

Résoudre ces problèmes exige une analyse soigneuse du diagramme de temporisation. Recherchez les fenêtres superposées où la stabilité n’est pas garantie. Assurez-vous que les séquences de réinitialisation sont correctement suivies pour éviter des états indéfinis.

Mise en œuvre du flux de travail modulaire 🛠️

Pour appliquer efficacement cette méthodologie, suivez un flux de travail structuré. Cela garantit que chaque aspect du temporisation est couvert sans redondance.

- Définir les interfaces :Listez clairement toutes les entrées et sorties de chaque module.

- Identifier les domaines d’horloge :Déterminez quels signaux appartiennent à quel domaine d’horloge.

- Cartographier les chemins de données :Suivez le chemin depuis la source jusqu’à la destination.

- Appliquer les contraintes :Définissez les exigences de setup et de hold pour chaque bascule.

- Valider les transitions :Vérifiez l’alignement des bords et les largeurs d’impulsion.

- Revoir l’intégration :Assurez-vous que les diagrammes de module s’alignent lorsqu’ils sont combinés.

Chaque étape s’appuie sur la précédente. Omettre une étape peut entraîner des lacunes dans la couverture. Par exemple, ignorer les domaines d’horloge peut entraîner des échecs de synchronisation difficiles à déboguer ultérieurement.

Gestion des domaines d’horloge multiples 🌐

À mesure que les conceptions grandissent, des fréquences d’horloge multiples deviennent nécessaires. Certaines parties du système fonctionnent rapidement, tandis que d’autres fonctionnent lentement. La synchronisation de ces domaines est l’un des aspects les plus complexes de l’analyse de temporisation.

Lorsque les signaux passent d’un domaine d’horloge à un autre, le diagramme de temporisation doit refléter la relation entre les deux horloges. Si les horloges sont asynchrones, une attention particulière est nécessaire pour éviter la métastabilité. Des techniques telles que les chaînes de synchronisation ou les protocoles de main-hand sont utilisées pour gérer ce transfert en toute sécurité.

Les stratégies clés pour les conceptions multi-horloges incluent :

- Codage de Gray :Utilisation du codage de Gray pour transmettre en toute sécurité des compteurs multi-bits entre les domaines.

- Tampons FIFO : Utilisation de files d’attente First-In-First-Out pour déconnecter les horloges de lecture et d’écriture.

- Signaux d’échange de main : Utilisation de paires demande/accusé de réception pour garantir la validité des données.

Les diagrammes de temporisation pour ces scénarios doivent montrer explicitement les fronts d’horloge des deux domaines. Cela permet aux ingénieurs de vérifier si les données restent stables assez longtemps pour que l’horloge réceptrice puisse les capturer.

Débogage avec des données visuelles 🔍

Lorsqu’un design échoue, les diagrammes de temporisation sont la première chose à examiner. Le débogage exige de la patience et une approche systématique. Commencez par isoler le module défaillant. Comparez le diagramme attendu avec la forme d’onde réelle.

Recherchez les écarts dans :

- Chronologie du signal par rapport à l’horloge.

- Largeur d’impulsion des signaux de contrôle.

- Transitions d’état pendant la réinitialisation.

- Glitches sur les lignes de données.

Les outils fournissent souvent des fonctionnalités de zoom pour inspecter des détails au niveau du nanoseconde. Utilisez ces fonctionnalités pour vérifier l’instant exact où une violation se produit. Corrélez les données visuelles avec la logique pour comprendre la cause racine.

Pensées finales sur l’intégrité du design 💡

Les diagrammes de temporisation sont bien plus que des dessins techniques ; ils sont le plan directeur des systèmes numériques fiables. En adoptant une approche modulaire, les ingénieurs peuvent gérer la complexité et maintenir la clarté. Cette méthode favorise l’évolutivité et réduit la probabilité d’erreurs coûteuses.

Le succès dans la conception matérielle repose sur l’attention aux détails. Chaque nanoseconde compte. Chaque transition a de l’importance. En appliquant rigoureusement ces principes, les équipes peuvent concevoir des systèmes qui fonctionnent de manière prévisible dans des conditions réelles. La décomposition modulaire de l’analyse de temporisation garantit qu’aucun détail n’est négligé, aboutissant à des solutions matérielles robustes et efficaces.

Le perfectionnement continu de ces compétences est nécessaire à mesure que la technologie évolue. De nouvelles normes et des vitesses plus élevées exigent des techniques d’analyse mises à jour. Restez informé des meilleures pratiques émergentes afin de maintenir un avantage concurrentiel dans le domaine de l’ingénierie numérique.