Comprendre l’évolution des signaux au fil du temps est fondamental en électronique numérique. Pour les ingénieurs étudiants, maîtriser l’interprétation des diagrammes de timing n’est pas seulement un exercice académique ; c’est une compétence essentielle pour concevoir des systèmes fiables. Ces représentations visuelles décrivent le comportement des signaux sur un axe temporel, révélant les relations entre les cycles d’horloge, la validité des données et les signaux de contrôle. Sans une bonne maîtrise de ces techniques, même des circuits simples peuvent échouer dans des conditions réelles.

Ce guide couvre les principes fondamentaux nécessaires pour lire, créer et analyser efficacement des diagrammes de timing. Nous explorerons les mécanismes de conception synchrone et asynchrone, l’importance des temps de préparation et de maintien, ainsi que la manière d’éviter les pièges courants qui entraînent l’échec des circuits. À la fin de cet article, vous disposerez d’une solide base pour aborder des problèmes complexes de logique numérique.

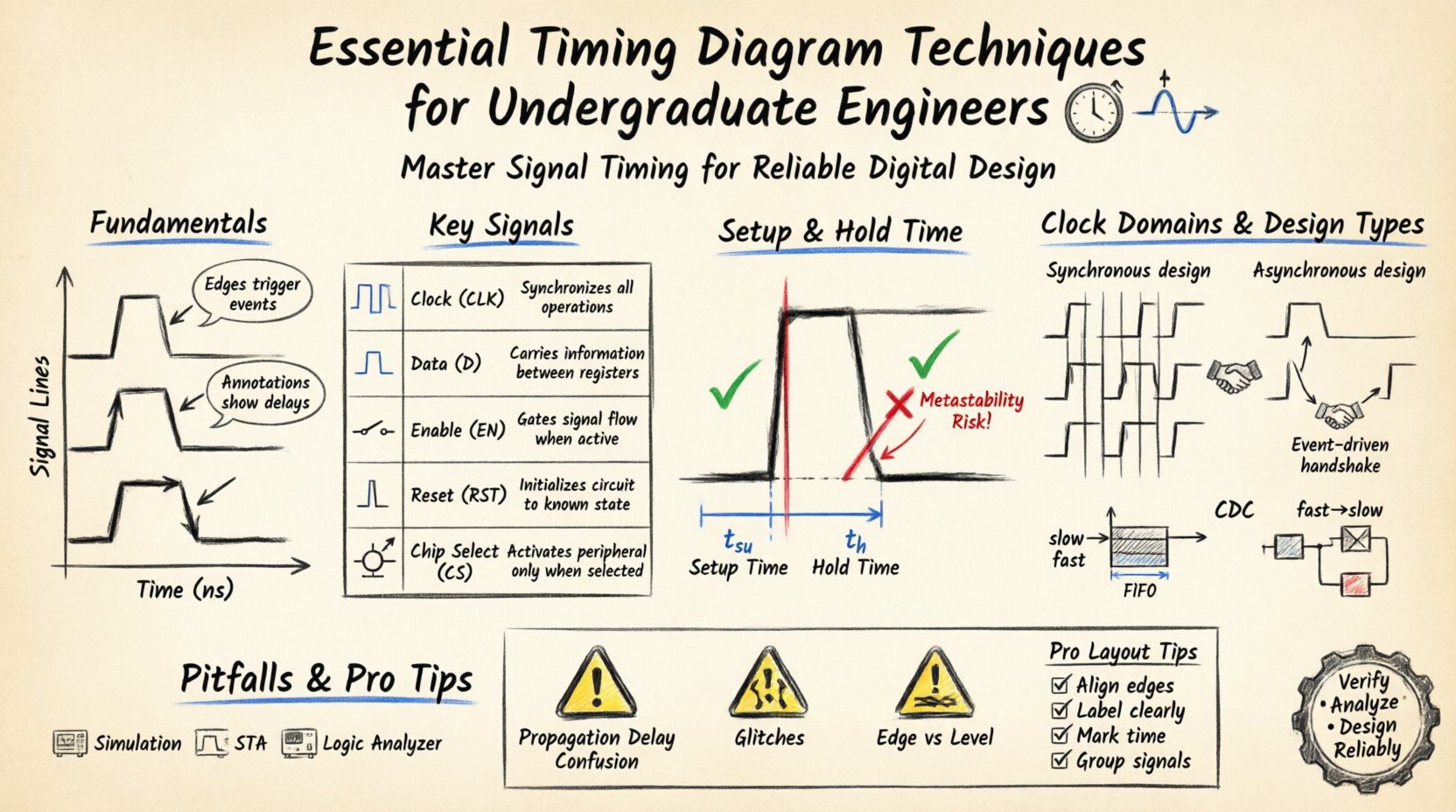

1. Fondamentaux des diagrammes de timing 📐

Un diagramme de timing est une représentation graphique des signaux au fil du temps. Il permet aux ingénieurs de visualiser l’état de diverses lignes dans un circuit numérique. Contrairement aux schémas logiques qui montrent les connexions, les diagrammes de timing montrent le comportement. Ils sont essentiels pour le débogage, la vérification des conceptions et la communication des interactions entre signaux dans les modules matériels.

Composants clés d’un diagramme de timing

- Axe du temps (axe des abscisses) :Représente l’évolution du temps. Il est généralement marqué en nanosecondes (ns) ou en cycles d’horloge.

- Lignes de signal (axe des ordonnées) :Lignes horizontales représentant des fils individuels ou des bus. Chaque ligne correspond à un nom de signal spécifique.

- Niveaux logiques :Les signaux sont généralement binaires, représentés par Haut (1) ou Bas (0). Parfois, des états « High-Z » (impédance élevée) apparaissent dans les conceptions de bus.

- Bords :Les transitions verticales indiquent un changement d’état. Les fronts montants (de Bas à Haut) et les fronts descendants (de Haut à Bas) sont essentiels pour déclencher des événements.

- Annotations :Les étiquettes textuelles indiquent souvent des délais, des instants précis ou des conditions affectant le signal.

Pourquoi le timing est-il important en logique numérique

Les systèmes numériques reposent sur une synchronisation précise. Si un signal arrive trop tôt ou trop tard par rapport à un front d’horloge, le système peut mal interpréter les données. Les diagrammes de timing rendent ces contraintes visibles. Ils aident à répondre à des questions telles que :

- Les données sont-elles stables avant le front d’horloge ?

- Combien de temps un signal met-il à se propager à travers une porte ?

- Deux horloges provenant de domaines différents s’interfèrent-elles mutuellement ?

2. Signaux et composants clés ⚡

Avant d’analyser des formes d’onde complexes, vous devez reconnaître les signaux standards utilisés en génie électronique numérique. Ces signaux déterminent la manière dont les données se déplacent et à quel moment elles sont considérées comme valides.

Types courants de signaux

| Nom du signal | Fonction | Comportement typique |

|---|---|---|

| Horloge (CLK) | Source de synchronisation | Pulsation régulière entre 0 et 1 |

| Données (D) | Support d’information | Change d’état en fonction de l’entrée ou de la logique |

| Activer (EN) | Active un module | Haut pour autoriser le fonctionnement, bas pour désactiver |

| Réinitialisation (RST) | Initialise l’état | Pulsation active basse ou active haute au démarrage |

| Sélection de puce (CS) | Sélectionne un périphérique | Active basse pour adresser un composant spécifique |

Comprendre l’état actif des signaux de contrôle est crucial. Certains signaux sont actifs haut, ce qui signifie qu’ils fonctionnent lorsque la tension est élevée. D’autres sont actifs bas, indiqués par une barre au-dessus du nom (par exemple, /RESET ou RST_N), ce qui signifie qu’ils fonctionnent lorsque la tension est basse.

3. Analyse des temps de setup et de hold 🕒

L’un des aspects les plus critiques de l’analyse du timing concerne les temps de setup et de hold. Ces paramètres définissent la fenêtre dans laquelle les données doivent être stables par rapport à une transition d’horloge. Le non-respect de ces contraintes entraîne une corruption des données ou une métastabilité.

Temps de setup (tsu)

Le temps de setup est la durée minimale pendant laquelle les données doivent être stables avantl’arrivée de l’edge actif de l’horloge. Si les données changent trop près de l’edge d’horloge, le bascule peut ne pas capturer la bonne valeur.

- Exigence :Les données doivent être stables pendant tsuavant le front montant.

- Conséquence de la violation : L’ensemble peut capturer des données incorrectes ou entrer dans un état indéfini.

Temps de maintien (th)

Le temps de maintien est la durée minimale pendant laquelle les données doivent rester stablesaprès l’arête active de l’horloge. Le bascule a besoin d’un instant pour capter la valeur avant que de nouvelles données n’arrivent éventuellement.

- Exigence :Les données doivent rester stables pendant th après l’arête montante.

- Conséquence de la violation : Similaire aux violations de configuration, cela provoque des erreurs de données ou une métastabilité.

Visualisation des temps de configuration et de maintien

Lors de la lecture d’un diagramme de temporisation, observez le signal de données par rapport à l’arête de l’horloge. La ligne de données doit être plate et inchangée pendant la fenêtre de configuration (avant) et la fenêtre de maintien (après). Si la ligne de données bascule dans ces fenêtres, le design est probablement défectueux.

4. Croisement de domaines d’horloge ⏱️

Dans les systèmes complexes, différentes parties du circuit peuvent fonctionner à des vitesses ou fréquences d’horloge différentes. Le déplacement des données entre ces domaines d’horloge distincts est appelé croisement de domaines d’horloge (CDC). Ce processus introduit des défis importants en matière de temporisation.

Types de domaines d’horloge

- Même fréquence, même phase :Conception synchrone. Une analyse de temporisation simple s’applique.

- Même fréquence, phase différente : Nécessite des vérifications d’alignement de phase.

- Fréquences différentes : Nécessite des techniques de synchronisation telles que des échanges de signaux ou des mémoires tampon FIFO.

Gestion du CDC dans les diagrammes de temporisation

Lors de l’analyse de diagrammes comportant plusieurs domaines d’horloge, assurez-vous de distinguer clairement les lignes d’horloge. Les données passant d’un domaine lent à un domaine rapide peuvent être risquées si elles ne sont pas gérées. À l’inverse, un passage rapide vers lent peut entraîner une perte de données si le récepteur échantillonne trop rapidement.

- Protocoles d’échange de signaux : Utilisez des signaux valides/prêts pour confirmer la fin du transfert de données.

- Mémoires tampon FIFO : Déconnectez les taux de production et de consommation.

- Synchroniseurs : Utilisez des bascules à plusieurs étages pour réduire le risque de métastabilité.

5. Conception synchrone vs asynchrone 🔄

L’architecture du design détermine l’apparence des diagrammes de temporisation. Comprendre la différence aide à prévoir le comportement des signaux.

Conception synchrone

La plupart de la logique numérique est synchrone. Tous les changements d’état se produisent sur le front d’un signal d’horloge central.

- Prévisibilité : Plus facile à analyser car le temporisation est contrôlée.

- Diagrammes de temporisation : Motifs réguliers, en grille. Les changements de données s’alignent sur les fronts d’horloge.

- Limites : Le décalage d’horloge peut devenir un problème dans les grands designs.

Conception asynchrone

Les changements d’état se produisent en fonction de l’arrivée des signaux, et non d’une horloge globale. C’est courant dans les protocoles d’échange de main et la gestion des interruptions.

- Flexibilité : Peut être plus rapide pour des tâches spécifiques car il attend uniquement les données.

- Diagrammes de temporisation : Irreguliers. Les signaux dépendent des événements précédents, et non de tranches de temps fixes.

- Risques : Suceptible aux conditions de course et aux aléas si la conception n’est pas soigneusement réalisée.

6. Pièges et erreurs courants ❌

Même les ingénieurs expérimentés commettent des erreurs lors de l’interprétation ou de la création de diagrammes de temporisation. Être conscient de ces erreurs courantes peut épargner un temps de débogage important.

1. Ignorer le délai de propagation

Les signaux ne changent pas instantanément. Les portes ont un délai de propagation. Si vous dessinez un diagramme en supposant des changements immédiats, votre simulation ne correspondra pas à la réalité.

- Solution : Toujours inclure des valeurs de délai entre les transitions logiques dans vos diagrammes.

2. Interpréter incorrectement les signaux actifs bas

Un signal étiqueté /CS est bas quand il est actif. Si vous supposez qu’il est haut, votre logique sera inversée.

- Résolution :Vérifiez le datasheet ou le schéma pour les états actifs. Recherchez les bulles sur les portes logiques.

3. Ignorer les parasites

Les parasites sont des impulsions courtes et involontaires. Ils peuvent survenir lorsque les signaux parcourent des chemins différents avec des délais variables.

- Résolution :Utilisez une logique sans risque ou ajoutez des étages de filtrage dans la conception.

4. Confusion entre front et niveau

Certains circuits sont déclenchés sur le front montant, d’autres sur le front descendant, et d’autres sur le niveau lui-même.

- Résolution :Vérifiez la condition de déclenchement dans la spécification du composant.

7. Lecture et création de diagrammes professionnels 📝

Une communication claire est essentielle en génie. Un diagramme de temporisation bien dessiné transmet des informations complexes en un coup d’œil. Voici les meilleures pratiques pour les créer.

Meilleures pratiques pour le layout

- Aligner les bords :Assurez-vous que les signaux associés changent à des intervalles constants.

- Étiqueter clairement :Utilisez les noms des signaux, et non seulement des lignes génériques.

- Indiquer le temps :Indiquez la durée des cycles ou des délais spécifiques.

- Regrouper les signaux :Organisez les signaux associés (comme les lignes de bus de données) ensemble.

Processus de création étape par étape

- Identifier les horloges :Dessinez les lignes d’horloge en premier. Elles constituent le fondement du temporisation.

- Ajouter les signaux de contrôle :Placez les lignes d’activation, de réinitialisation et de sélection de puce.

- Tracer les données :Ajoutez les lignes de données en fonction du flux logique.

- Annoter :Ajoutez des notes pour les temps de préparation/conservation ou des délais spécifiques.

- Révision : Vérifiez les violations et la cohérence logique.

8. Analyse de scénarios du monde réel 🔍

Examinons un scénario impliquant une opération de lecture de mémoire. C’est une tâche courante pour les ingénieurs travaillant avec des microcontrôleurs.

Cycle de lecture de mémoire

Lors d’une lecture de mémoire, le processeur envoie une adresse, active une commande de lecture et attend les données.

- Bus d’adresse : Valide avant l’edge d’horloge.

- Sélection de puce : Passe à bas pour activer la mémoire.

- Commande de lecture : Passe à bas pour initier le transfert.

- Bus de données : Reste en état haute impédance jusqu’à ce que la mémoire le pilote.

- Timing : Les données doivent être stables avant que le processeur ne les échantillonne.

Considérations sur l’intégrité du signal

À mesure que la fréquence augmente, l’intégrité du signal devient un facteur majeur. Les réflexions, les couplages indésirables et le bruit peuvent déformer les formes d’onde. Les diagrammes de timing dans les conceptions à haute vitesse doivent tenir compte de ces problèmes au niveau physique.

- Taux de montée/descente : À quelle vitesse le signal évolue. Trop rapide provoque du bruit ; trop lent entraîne des erreurs de timing.

- Niveaux de tension : Assurez-vous que les seuils logiques sont respectés malgré les variations de température et de tension.

9. Concepts avancés de temporisation 🧠

Pour ceux souhaitant approfondir leurs connaissances, plusieurs concepts avancés étendent l’analyse de temporisation de base.

Métastabilité

La métastabilité se produit lorsque une bascule ne parvient pas à se stabiliser sur un état 0 ou 1 stable dans le délai requis. Cela se produit généralement lorsque les données changent trop près de l’edge d’horloge.

- Probabilité : C’est un événement probabiliste, pas déterministe.

- Atténuation : Utilisez des chaînes de synchronisation (plusieurs bascules en série) pour réduire la probabilité à presque zéro.

Désynchronisation d’horloge

La désynchronisation d’horloge est la différence entre les temps d’arrivée du signal d’horloge dans différentes parties du circuit. Un déséquilibre positif (arrivée plus tardive) peut aider le temps de préparation mais nuire au temps de maintien. Un déséquilibre négatif fait l’inverse.

- Impact sur la conception : La désynchronisation doit être prise en compte dans les budgets de temporisation.

- Mesure : Utilisez des oscilloscopes ou des outils de simulation pour mesurer la désynchronisation.

Jitter

Le jitter est la déviation du front d’horloge par rapport à sa position idéale. Il réduit les marges effectives de préparation et de maintien.

- Types :Jitter périodique, jitter cycle à cycle et jitter aléatoire.

- Impact : Un jitter élevé limite la fréquence d’opération maximale d’un système.

10. Outils et méthodologies 🛠️

Bien que l’analyse manuelle soit éducative, l’ingénierie moderne repose sur des outils. Toutefois, comprendre la théorie sous-jacente est ce qui vous permet d’utiliser efficacement ces outils.

Logiciels de simulation

Les langages de description matérielle (HDL) permettent la simulation. Ces outils génèrent automatiquement des diagrammes temporels à partir du code. Vous devez comprendre la sortie pour vérifier la correction du code.

Analyse statique de temporisation (STA)

Les outils d’analyse statique de temporisation vérifient mathématiquement que toutes les voies respectent les exigences de temporisation sans simulation. Ils vérifient les violations de préparation et de maintien à travers tous les coins (température, tension).

Débogage avec des analyseurs logiques

Les débogueurs matériels captent des signaux réels provenant d’une carte. Ils affichent des diagrammes temporels correspondant à la réalité, ce qui aide à identifier des problèmes au niveau de la couche physique que la simulation pourrait manquer.

Conclusion 🏁

Les diagrammes temporels sont le langage du comportement des signaux numériques. Ils combler le fossé entre la logique abstraite et la réalité physique. Pour les ingénieurs étudiants, consacrer du temps à maîtriser ces techniques rapporte des bénéfices tout au long de votre carrière. Que vous conceviez un compteur simple ou un processeur complexe, la capacité à lire et analyser les contraintes de temporisation est incontournable.

En vous concentrant sur les temps de préparation et de maintien, en comprenant les domaines d’horloge et en évitant les pièges courants, vous construisez une base solide. N’oubliez jamais de vérifier les états actifs et de tenir compte des délais de propagation. Au fur et à mesure que vous progressez, vous rencontrerez des scénarios de plus en plus complexes, mais les principes fondamentaux restent les mêmes. Continuez à pratiquer l’analyse des diagrammes, et vos conceptions deviendront plus fiables et efficaces.

Poursuivez l’affinement de vos compétences en étudiant les fiches techniques et en examinant les formes d’onde de circuits du monde réel. Le domaine de l’ingénierie numérique évolue rapidement, mais les fondamentaux de l’analyse de temporisation restent constants.