Les diagrammes de temporisation sont la colonne vertébrale de la conception des systèmes numériques. Ils fournissent un langage visuel que les ingénieurs utilisent pour décrire comment les signaux évoluent dans le temps. Que vous conceviez une interface de microcontrôleur ou débogiez un protocole de communication, comprendre ces diagrammes est essentiel. Ce guide vous accompagne dans la création et l’interprétation de ces diagrammes sans complexité inutile.

Commencer peut sembler intimidant, mais avec le bon cadre, vous pouvez rapidement dessiner des diagrammes efficaces. Nous aborderons les composants fondamentaux, la logique derrière les transitions de signaux, ainsi que les paramètres critiques qui définissent la fiabilité du système. Penetrions maintenant dans les mécanismes du temporisation des signaux.

Comprendre le but fondamental 🧠

Un diagramme de temporisation est une représentation graphique de la séquence des événements dans un système. Il représente l’état des signaux par rapport à un axe commun du temps. Contrairement aux schémas qui montrent les connexions physiques, les diagrammes de temporisation se concentrent sur les relations temporelles. Cette distinction est cruciale pour déboguer des erreurs logiques qui ne se manifestent pas dans une analyse statique du circuit.

Lorsque vous dessinez ces diagrammes, vous documentez le comportement des signaux de données et de contrôle. L’objectif est de garantir qu’un signal soit prêt avant qu’un autre n’agisse sur lui. Cette synchronisation empêche la corruption des données et assure un fonctionnement stable.

-

Clarté visuelle : Ils rendent les dépendances temporelles abstraites concrètes.

-

Aide au débogage : Ils mettent en évidence les conditions de course et les violations de configuration.

-

Documentation : Ils servent de référence pour les équipes matérielles et logicielles.

-

Vérification : Ils aident à vérifier que la logique correspond aux spécifications.

Sans un diagramme clair, il est facile de manquer des problèmes de temporisation subtils qui n’apparaissent qu’à des conditions spécifiques. En standardisant la manière dont vous dessinez, vous réduisez l’ambiguïté pour toutes les personnes impliquées dans le projet.

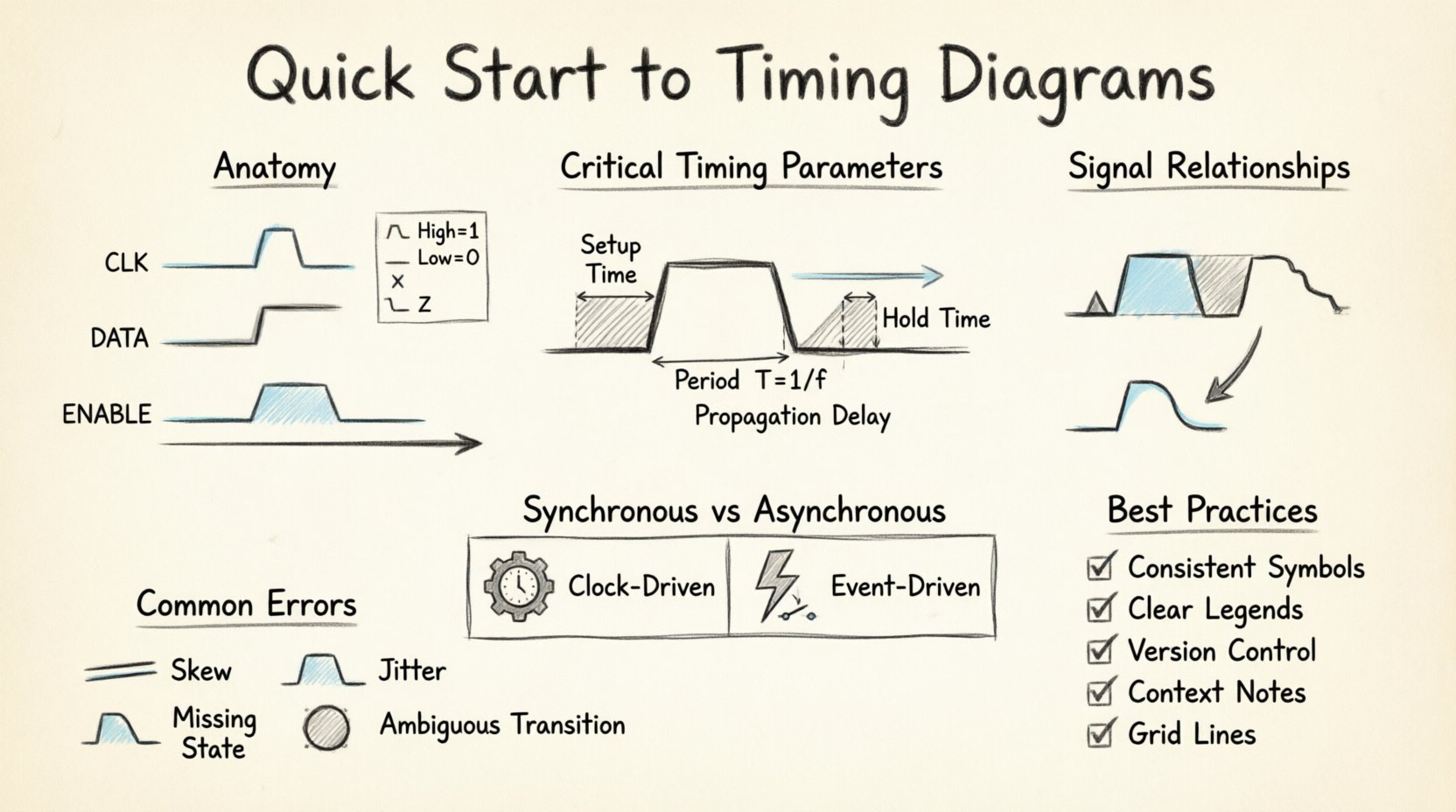

Anatomie d’un diagramme de temporisation 📐

Chaque diagramme de temporisation partage une structure commune. Maîtriser cette structure vous permet de lire facilement des formes d’onde complexes. La disposition est cohérente dans différentes disciplines ingénierie, des systèmes embarqués aux réseaux à haute vitesse.

1. L’axe du temps ⏰

L’axe horizontal représente le temps. Il s’écoule de gauche à droite. Le temps n’est pas toujours linéaire dans chaque contexte, mais dans la plupart des diagrammes standards, des distances égales représentent des intervalles de temps égaux. Vous n’avez pas besoin de marquer chaque milliseconde, mais le repérage des intervalles clés aide à échelonner les informations.

-

Direction :Toujours de gauche à droite.

-

Échelle :Peut être linéaire ou logarithmique selon la fréquence du signal.

-

Repères :Utilisez des lignes verticales pour indiquer des événements spécifiques, comme les fronts d’horloge.

2. Les lignes de signal 📊

Les signaux sont représentés par des lignes horizontales empilées verticalement. Chaque ligne correspond à un fil ou un réseau spécifique dans le circuit. Le nom du signal apparaît généralement à gauche ou à droite de la ligne.

-

Regroupement :Les signaux liés, tels que les lignes d’adresse et de données, sont souvent regroupés ensemble.

-

Étiquetage :Toujours étiqueter clairement les signaux pour éviter toute confusion entre des noms similaires.

-

Ordre :Placez le signal le plus important en haut ou en bas, selon la convention.

3. Niveaux logiques 🔋

Les signaux basculent entre des états définis. En logique numérique, ces états sont généralement haut et bas, ou 1 et 0. La position verticale de la ligne indique l’état.

|

État |

Notation courante |

Signification physique |

|---|---|---|

|

Haut |

1, H, VCC |

Rail de tension positive |

|

Bas |

0, L, GND |

Masse ou tension nulle |

|

Inconnu |

X |

État indéterminé |

|

Impédance élevée |

Z |

Déconnecté ou flottant |

Comprendre ces niveaux est la première étape pour lire le schéma. Ce sont les transitions entre ces niveaux qui marquent l’action.

Paramètres de temporisation critiques ⚙️

La temporisation ne consiste pas seulement à tracer des lignes ; elle consiste à définir des contraintes. Certains paramètres déterminent à quelle vitesse un signal peut changer et à quel moment il doit être stable. Ces contraintes sont essentielles pour garantir que le système fonctionne correctement.

1. Temps de préparation ⏳

Le temps de préparation est la durée minimale pendant laquelle un signal de données doit rester stable avant l’arrivée d’une transition d’horloge. Si les données changent trop près de l’arête d’horloge, le système pourrait capturer une valeur incorrecte. Il s’agit d’une contrainte critique dans les systèmes synchrones.

-

Définition :Temps avant l’arête active de l’horloge.

-

Violation :Provoque une métastabilité ou une capture incorrecte des données.

-

Règle de conception : Assurez-vous que les données sont stables bien avant que l’horloge ne déclenche.

2. Temps de maintien ⏳

Le temps de maintien est la durée minimale pendant laquelle un signal de données doit rester stable après l’edge de l’horloge. Si le signal change trop tôt après le déclenchement, l’élément récepteur pourrait ne pas capturer correctement la valeur.

-

Définition :Temps après l’edge actif de l’horloge.

-

Violation : Similaire au temps de préparation, entraîne des erreurs de données.

-

Règle de conception : Assurez-vous que le signal ne bascule pas immédiatement après l’horloge.

3. Délai de propagation ⏱️

Le délai de propagation est le temps nécessaire à un signal pour voyager depuis l’entrée d’un composant jusqu’à sa sortie. Aucun composant électronique n’est instantané. Ce délai s’accumule sur plusieurs étages et doit être pris en compte dans les conceptions à haute vitesse.

-

Source :Retards internes des portes et longueur des conducteurs.

-

Impact : Limite la fréquence d’opération maximale.

-

Mesure : Mesuré du point à 50 % de l’entrée au point à 50 % de la sortie.

4. Période et fréquence 🔁

Pour les signaux d’horloge, la période est le temps entre deux points identiques consécutifs sur la forme d’onde (par exemple, de front montant à front montant). La fréquence est l’inverse de la période.

-

Période : T = 1 / f

-

Cycle de travail : Pourcentage de temps pendant lequel le signal est à l’état haut au cours d’une période.

-

Stabilité : Le jitter d’horloge affecte la précision du timing.

Lecture et analyse des relations entre signaux 🔄

Une fois que vous avez compris les composants, la prochaine étape consiste à analyser comment les signaux interagissent. C’est là que le schéma devient un outil diagnostique. Vous recherchez des dépendances et des conflits potentiels.

1. Déclenchement sur front 📉

La plupart des circuits numériques se déclenchent sur des fronts spécifiques de l’horloge. Certains se déclenchent sur le front montant, tandis que d’autres utilisent le front descendant. Vous devez identifier quel front est actif pour chaque composant de votre système.

-

Front montant : Transition de bas à haut.

-

Front descendant : Transition de haut à bas.

-

Les deux fronts : Certains systèmes échantillonnent les données sur les deux transitions.

Lors du dessin, utilisez de petits triangles ou des entailles pour indiquer quel front est actif. Cela évite toute confusion lors de la mise en œuvre.

2. Fenêtres de données valides 🕒

Les données ne sont valables que dans une fenêtre spécifique. Avant le temps de préparation et après le temps de maintien, la ligne de données ne doit pas changer. En dehors de cette fenêtre, les données sont considérées comme valides. Marquer cette fenêtre sur votre schéma clarifie les attentes.

-

Fenêtre : Définie par le temps de préparation + le temps de maintien + le délai de propagation.

-

Violation : Si les données changent en dehors de cette fenêtre, des erreurs se produisent.

-

Indicateur visuel : Utilisez des zones ombrées pour mettre en évidence les périodes de données valides.

3. Signaux asynchrones 📡

Tous les signaux ne suivent pas l’horloge. Les signaux asynchrones comme les interruptions ou les réinitialisations fonctionnent de manière indépendante. Ils nécessitent une gestion soigneuse dans les diagrammes temporels pour montrer leur priorité et leur latence.

-

Priorité : Les interruptions ont souvent la priorité sur les cycles d’horloge.

-

Latence : Notez le délai entre l’assertion et la réponse.

-

Stabilité : Assurez-vous que les signaux asynchrones sont stables pour les exigences de préparation/maintien.

Systèmes synchrones vs asynchrones 📡

La distinction entre la conception synchrone et asynchrone influence la manière dont vous construisez vos diagrammes. Chaque approche a ses règles et conventions spécifiques.

|

Fonctionnalité |

Synchrones |

Asynchrones |

|---|---|---|

|

Contrôle |

Commandé par une horloge |

Commandé par des événements |

|

Prédiction |

Timing facile à prédire |

Timing plus difficile à prédire |

|

Complexité |

Logique standardisée |

Protocoles d’échange de poignées |

|

Puissance |

Plus élevée en raison de l’horloge |

Souvent plus faible |

Dans un schéma synchrone, vous verrez une ligne d’horloge dominante qui aligne tous les autres signaux. Dans un schéma asynchrone, vous verrez des échanges de poignées et des états d’attente. Les deux nécessitent une documentation précise du timing.

Erreurs courantes et comment les éviter ⚠️

Les erreurs dans les diagrammes de timing peuvent entraîner des révisions coûteuses du matériel. Être conscient des pièges courants vous aide à réaliser des représentations plus propres et plus précises.

1. Ignorer le décalage 📏

Le décalage est la différence de temps d’arrivée d’un signal à différents points. Si vous supposez que tous les signaux arrivent simultanément, vous pourriez manquer des violations de timing. Prenez toujours en compte les différences de longueur de câble et de charge.

-

Vérifiez : Comparez les temps d’arrivée aux différents récepteurs.

-

Solution : Ajoutez des tampons de retard ou ajustez les longueurs des pistes.

-

Visuel : Montrez de légers décalages dans les lignes parallèles si le décalage est significatif.

2. Ignorer le jitter ⚡

Le jitter est la variation dans le timing d’un signal. Une horloge peut ne pas être parfaitement périodique. Dans les conceptions à haute vitesse, le jitter peut réduire vos marges de timing. Représentez le jitter par une zone ombrée autour du front de l’horloge.

-

Source : Bruit d’alimentation ou interférence externe.

-

Impact : Réduit le temps de préparation et de maintien effectifs.

-

Visuel : Utilisez des lignes floues ou des bandes pour indiquer l’incertitude.

3. Transitions ambigües 🔄

Une transition qui ressemble à une ligne droite pourrait en réalité être une pente. Les signaux réels ne changent pas instantanément. Dessiner des lignes verticales parfaites implique une vitesse infinie, ce qui est physiquement impossible.

-

Meilleure pratique : Dessinez les transitions avec une légère pente si une précision est requise.

-

Convention : Les lignes verticales sont acceptables pour une représentation logique.

-

Clarté : Assurez-vous que l’intention est claire, quelle que soit la pente.

4. Transition d’état manquante 🚦

Les machines à états complexes ont souvent des états intermédiaires qui ne sont pas évidents. Si vous ne dessinez que les états de départ et d’arrivée, vous perdez des informations critiques sur la séquence.

-

Détail : Montrez tous les changements d’état pertinents.

-

Étiquettes : Annotez les états avec leurs noms ou leurs valeurs.

-

Logique : Assurez-vous que le diagramme reflète le flux logique réel.

Meilleures pratiques pour la documentation 📝

Pour garantir que vos diagrammes restent utiles pendant des années, adoptez un style cohérent. Cela facilite leur maintenance et leur partage avec d’autres ingénieurs.

-

Symboles cohérents : Utilisez les mêmes flèches et styles de ligne tout au long.

-

Légendes claires : Définissez tous les symboles personnalisés ou abréviations utilisés.

-

Contrôle de version : Étiquetez les diagrammes avec des numéros de version et des dates.

-

Contexte : Incluez une brève description du système représenté.

-

Lignes de grille : Utilisez une grille pour aider à aligner les signaux et marquer les intervalles de temps.

La cohérence réduit la charge cognitive pour quiconque lit votre travail. Elle facilite également la détection des anomalies lors de la relecture du diagramme plus tard.

Dépannage avec l’analyse de temporisation 🛠️

Lorsqu’un système échoue, les diagrammes de temporisation sont souvent le premier endroit à examiner. Ils aident à déterminer si le problème est logique ou temporel.

1. Identification des conditions de course 🏁

Une condition de course se produit lorsque la sortie dépend de l’ordre des événements. Si deux signaux arrivent en même temps à une porte, le résultat peut être imprévisible. Les diagrammes temporels révèlent ces chevauchements.

-

Rechercher : Signaux qui se croisent simultanément.

-

Résolution : Ajouter un tampon ou réorganiser la logique.

-

Prévention : Concevoir avec des marges pour éviter les transitions simultanées.

2. Détection des glitchs ⚡

Les glitchs sont des impulsions courtes qui surviennent en raison des délais de propagation. Ils pourraient déclencher un bascule involontairement. Sur un diagramme, ils apparaissent comme des pics étroits entre des niveaux stables.

-

Visuel :Impulsions étroites qui ne correspondent pas à la période d’horloge.

-

Solution :Utiliser un filtrage ou verrouiller le signal sur le bord stable.

-

Analyse :Vérifier si la largeur de l’impulsion dépasse le temps de maintien.

3. Vérification des protocoles de bus 📡

Les bus comme I2C ou SPI ont des exigences de temporisation strictes. Les conditions de démarrage et d’arrêt, le stretch d’horloge et les décalages de données doivent être parfaitement alignés. Les diagrammes temporels sont la méthode standard pour vérifier ces protocoles.

-

Démarrage/Arrêt :Vérifier la transition correcte sur la ligne de données par rapport à l’horloge.

-

Stretching :S’assurer que l’esclave peut maintenir l’horloge à bas pendant la durée requise.

-

Données :Confirmer que les données sont stables pendant la phase haute de l’horloge.

Pensées finales sur l’intégrité du signal 🎯

Créer des diagrammes temporels précis est une compétence qui s’améliore avec la pratique. Elle exige une compréhension approfondie du comportement des électroniques dans le temps. En suivant les directives ci-dessus, vous pouvez créer des diagrammes à la fois informatifs et fiables.

Souvenez-vous que ces diagrammes sont des outils de communication. Ils combler le fossé entre la théorie et la mise en œuvre. Quand vous dessinez un diagramme temporel, vous racontez une histoire sur le comportement du système. Rendez cette histoire claire, précise et cohérente.

Concentrez-vous sur les paramètres essentiels : setup, hold, délai et décalage. Gardez la mise en page propre et les étiquettes sans ambiguïté. Avec ces habitudes, vous découvrirez que la réalisation de diagrammes temporels devient une étape naturelle de votre processus de conception, vous permettant de les réaliser en quelques minutes plutôt que des heures.