Comprendre le flux des signaux au sein d’un système numérique est crucial pour les ingénieurs travaillant sur du matériel, du micrologiciel ou du logiciel embarqué. Un diagramme temporel sert d’outil visuel principal pour cartographier l’interaction entre différents signaux sur une période donnée. Cette représentation visuelle permet aux équipes de vérifier que les données sont correctement capturées, que les horloges sont stables et que les transitions logiques se produisent sans conflit. Sans une compréhension précise de ces diagrammes, la fiabilité du système peut être gravement compromise. Ce guide explore les éléments essentiels qui composent un diagramme temporel, garantissant une conception et une analyse précises.

Qu’est-ce qu’un diagramme temporel ? 📊

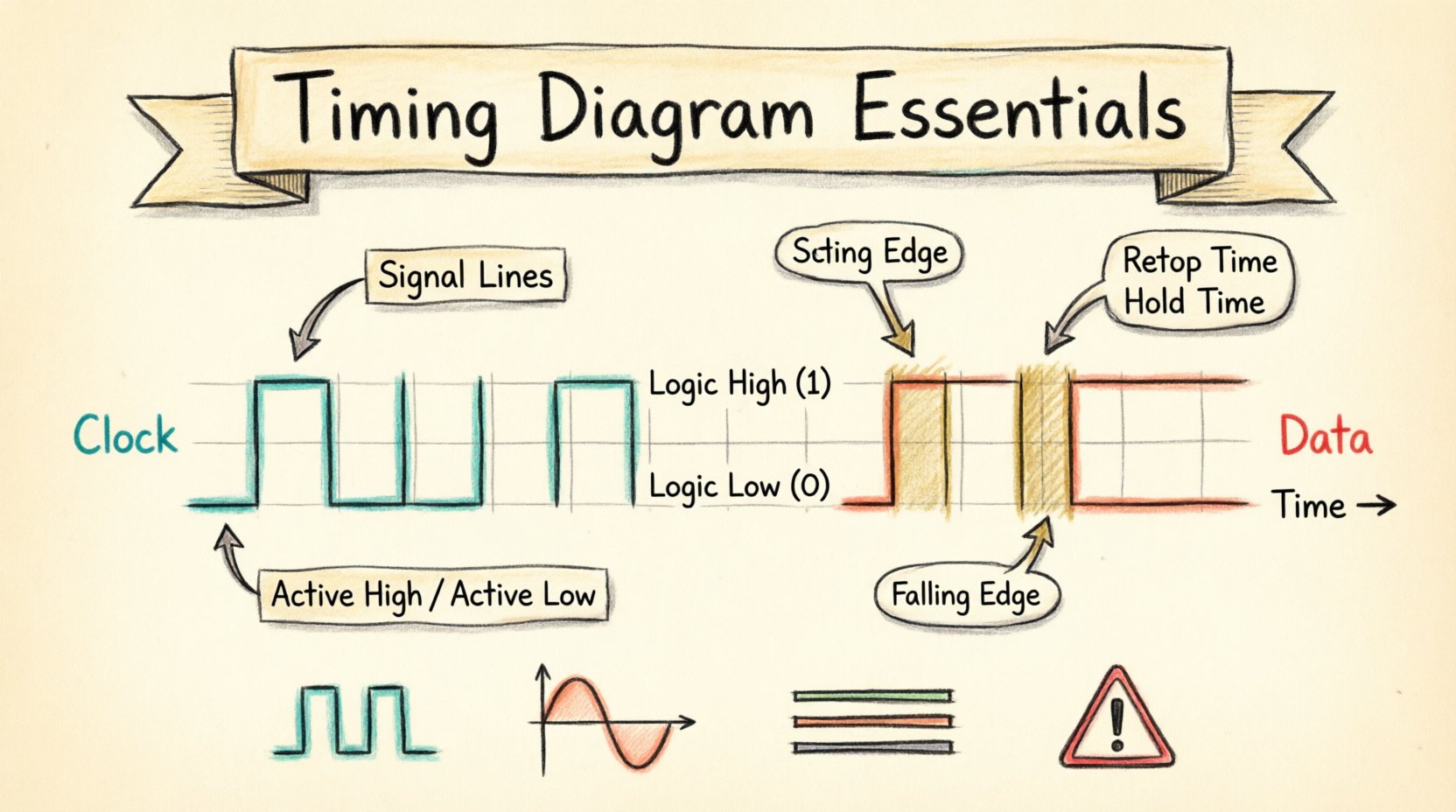

Un diagramme temporel est une illustration graphique qui montre le comportement de deux ou plusieurs signaux au fil du temps. Il cartographie la séquence des événements, indiquant quand les signaux changent d’état, combien de temps ils restent dans cet état et comment ils sont liés à une source d’horloge. En conception matérielle, ces diagrammes sont indispensables pour vérifier que les composants communiquent correctement. En logiciel, ils aident à visualiser la concurrence, les conditions de course et les points de synchronisation.

Ces diagrammes représentent généralement le temps sur l’axe horizontal (axe des x) et le niveau ou l’état du signal sur l’axe vertical (axe des y). Les lignes verticales représentent des points précis dans le temps, tandis que les lignes horizontales indiquent l’état stable d’un signal. Les transitions entre ces états sont cruciales, car elles indiquent le transfert réel de données ou les actions de contrôle qui ont lieu au sein du système.

Composants fondamentaux d’un diagramme temporel 🔧

Pour lire ou créer un diagramme temporel efficace, il faut comprendre les éléments de base. Chaque diagramme, quelle que soit sa complexité, repose sur un ensemble cohérent d’éléments pour transmettre l’information avec précision.

- Axe du temps: La ligne de base horizontale représentant l’évolution du temps. Elle s’écoule généralement de gauche à droite, indiquant le « passé » vers le « futur ».

- Lignes de signal: Des pistes horizontales attribuées à des fils spécifiques, des bus ou des variables. Chaque ligne représente le niveau logique d’un signal spécifique.

- Niveaux logiques: Les positions verticales sur la ligne de signal. En général, les états haut (1, Vcc, Vrai) et bas (0, Gnd, Faux) sont représentés.

- Transitions: Les lignes verticales reliant les niveaux logiques. Une transition montante passe du bas au haut, tandis qu’une transition descendante passe du haut au bas.

- Annotations: Des étiquettes de texte ou des repères qui clarifient des événements spécifiques, des délais ou des états.

L’axe du temps : la précision compte ⏳

L’axe du temps est la fondation du diagramme. Il ne représente pas toujours des secondes du monde réel ; il représente souvent des cycles d’horloge ou des nanosecondes selon la vitesse de conception. La cohérence dans l’échelle est essentielle. Si une section du diagramme affiche 10 nanosecondes par carré de grille, une autre section doit conserver cette échelle, sauf si elle est explicitement agrandie pour plus de détails.

Lors de l’analyse des performances du système, l’axe du temps aide à identifier les goulets d’étranglement. Par exemple, si un signal de données nécessite 50 nanosecondes pour se stabiliser, mais que l’arête d’horloge survient après 40 nanosecondes, une violation existe. L’axe permet aux ingénieurs de mesurer directement ces intervalles.

Lignes de signal et niveaux logiques 🔄

Chaque ligne de signal correspond à un fil physique ou à une variable logique. Dans les systèmes complexes, un bus peut être représenté par une ligne épaisse avec plusieurs signaux regroupés, ou par des lignes individuelles pour chaque bit. Les niveaux logiques définissent l’état du signal :

- Actif haut: Le signal est considéré comme « allumé » ou « vrai » lorsque la tension est élevée.

- Actif bas: Le signal est considéré comme « allumé » ou « vrai » lorsque la tension est faible. Cela est souvent indiqué par un cercle sur le symbole ou une convention de nommage spécifique.

Comprendre l’état actif est crucial pour interpréter les signaux de contrôle tels que « Chip Select » ou « Write Enable ». Interpréter un signal actif-bas comme actif-haut peut entraîner des échecs de conception difficiles à déboguer.

Transitions et arêtes ⚡

Les transitions se produisent lorsque un signal passe d’un niveau logique à un autre. Ces changements sont rarement instantanés dans le monde physique, mais dans un diagramme temporel, ils sont souvent dessinés comme des lignes verticales pour représenter le moment idéal du changement.

- Arête montante: La transition du bas au haut. C’est souvent le point de déclenchement pour la logique synchrone.

- Front descendant: La transition du haut au bas. Certains systèmes utilisent cette transition pour capturer les données.

- Déclenché par front: Une logique qui réagit uniquement au moment de la transition.

- Déclenché par niveau: Une logique qui réagit tant que le signal reste dans un état spécifique.

Les signaux du monde réel ont des temps de montée et de descente. Une ligne verticale parfaite est une abstraction. Dans les conceptions à haute vitesse, la pente de la transition importe car elle affecte les interférences électromagnétiques et l’intégrité du signal.

Paramètres et contraintes de temporisation 📐

Au-delà des lignes visuelles, la valeur critique d’un diagramme de temporisation réside dans les paramètres quantitatifs définis aux côtés des signaux. Ces paramètres définissent les limites physiques dans lesquelles le matériel doit fonctionner.

Temps de préparation et temps de maintien ⚙️

Ce sont les deux contraintes les plus courantes dans la conception de logique séquentielle, en particulier lorsque les données sont capturées par une bascule sur un front d’horloge.

- Temps de préparation: La durée minimale pendant laquelle le signal de données doit rester stable avant le front actif de l’horloge. Si les données changent trop près du front d’horloge, la bascule peut ne pas capturer la bonne valeur.

- Temps de maintien: La durée minimale pendant laquelle le signal de données doit rester stable après le front actif de l’horloge. Si les données changent trop tôt après le front, la capture peut être corrompue.

| Paramètre | Définition | Conséquence de la violation |

|---|---|---|

| Temps de préparation | Temps pendant lequel les données doivent être stables avant le front d’horloge | Métastabilité ou capture incorrecte des données |

| Temps de maintien | Temps pendant lequel les données doivent être stables après le front d’horloge | Métastabilité ou capture incorrecte des données |

| Retard de propagation | Temps nécessaire au signal pour traverser une porte | Réduction de la marge de temporisation, fréquence maximale plus faible |

| Désynchronisation horaire | Différence de temps d’arrivée du signal d’horloge | Réduction de la fenêtre de temporisation effective |

Retard de propagation ⏱️

Le retard de propagation est le temps nécessaire pour qu’un changement à l’entrée affecte la sortie. Dans un diagramme de temporisation, cela apparaît comme l’écart entre une transition d’horloge et le changement de données correspondant. Ce retard est dû à des limitations physiques, telles que la capacité des fils et la vitesse de commutation des transistors.

Lors de la conception d’un système, la somme des retards de propagation le long d’un chemin doit être inférieure à la période d’horloge moins le temps de préparation. Si le retard est trop long, le système ne peut pas fonctionner à la vitesse d’horloge souhaitée.

Désynchronisation horaire et jitter 📉

La désynchronisation horaire fait référence à la différence de temps d’arrivée du signal d’horloge dans différentes parties du circuit. Dans un diagramme idéal, la ligne d’horloge est verticale et simultanée pour tous les composants. En réalité, les différences de routage causent la désynchronisation. Un désynchronisation positive signifie que l’horloge arrive plus tard à la destination, ce qui peut aider le temps de préparation mais nuit au temps de maintien.

Le jitter est la variation dans le moment des transitions du signal. Il s’agit d’un bruit qui fait que la transition se produit plus tôt ou plus tard que prévu. Un jitter élevé réduit la marge de temporisation effective, ce qui oblige le système à fonctionner plus lentement pour maintenir la stabilité.

Types de signaux et de bus 📡

Les différents systèmes utilisent des méthodes de signalisation différentes. Le diagramme de temporisation doit refléter ces différences pour être précis.

Signaux numériques

La plupart des diagrammes de temporisation se concentrent sur la logique numérique. Ces signaux sont binaires, passant entre 0 et 1. La clarté du diagramme dépend de la marquage clair des seuils logiques. Certains signaux peuvent présenter des états intermédiaires ou des conditions « indifférentes », généralement marquées par une X.

Signaux analogiques

Bien que moins courants dans les diagrammes de temporisation purement numériques, les signaux analogiques tels que les rails de tension ou les sorties de capteurs sont parfois inclus. Ils sont représentés par des lignes inclinées ou courbées plutôt que par des sauts abrupts, indiquant une variation continue plutôt qu’un changement d’état discret.

Bus et données parallèles

Lorsque plusieurs bits se déplacent simultanément, ils sont souvent regroupés. Un diagramme de temporisation de bus montre l’état de tous les bits en même temps. Il est essentiel de préciser la largeur du bus (par exemple, 8 bits, 32 bits) et de montrer la fenêtre de données valide où tous les bits sont stables simultanément.

Lecture d’un diagramme de temporisation : un guide étape par étape 🔍

Interpréter ces diagrammes nécessite une approche systématique pour éviter de manquer des détails critiques.

- Identifier l’horloge: Localisez la référence principale de temporisation. Tous les autres événements doivent être mesurés par rapport à cette ligne.

- Déterminer la sensibilité aux transitions: Vérifiez si le système est déclenché par la transition montante ou descendante de l’horloge.

- Suivre la validité des données: Recherchez la période où les lignes de données sont stables. Il s’agit de la « fenêtre valide ».

- Vérifier les signaux de contrôle: Identifiez les lignes d’activation, de réinitialisation ou de sélection de puce qui contrôlent le transfert des données.

- Mesurer les intervalles: Utilisez l’axe du temps pour mesurer les délais, les temps de préparation et les largeurs d’impulsion.

Violations de temporisation courantes et erreurs ⚠️

Même avec une planification soigneuse, des violations de temporisation se produisent. Reconnaître les signes sur un diagramme est la première étape pour les corriger.

- Violation de préparation: Les données arrivent trop tard pour le prochain front d’horloge. La solution consiste souvent à ralentir l’horloge ou à optimiser le chemin logique afin de réduire le délai.

- Violation de maintien: Les données changent trop tôt après le front d’horloge. Cela est souvent plus difficile à corriger, car cela peut nécessiter l’ajout d’un délai dans le chemin des données ou dans le chemin de l’horloge.

- Métastabilité: Un état où la sortie d’un bascule est ni 0 ni 1 pendant une période indéfinie. Cela se produit généralement lorsque les temps de préparation ou de maintien sont violés.

- Glitches: Des impulsions courtes et involontaires causées par des conditions de course dans la logique combinatoire. Elles peuvent déclencher des changements d’état erronés si elles ne sont pas filtrées.

Conception asynchrone vs. synchrone 🔄

Les diagrammes de temporisation ont l’air différents selon la méthodologie de conception.

Conception synchrone

Les événements sont synchronisés par une horloge globale. Le diagramme de temporisation montre des lignes d’horloge claires et périodiques. Les données ne changent que sur les fronts d’horloge. Cette approche simplifie l’analyse car la fenêtre de temporisation est fixe.

Conception asynchrone

Les événements sont synchronisés par des signaux d’échange (comme Request et Acknowledge). Le diagramme de temporisation montre des intervalles irréguliers entre les événements. Bien que plus flexible, ces diagrammes sont plus difficiles à analyser car il n’y a pas de référence temporelle fixe.

Application dans les protocoles 📡

Les protocoles de communication reposent fortement sur une temporisation précise. Comprendre le diagramme est essentiel pour implémenter ces normes.

Communication série

Les interfaces série transmettent les données un bit à la fois. Le diagramme de temporisation montre la période du bit. La relation entre l’horloge et la ligne de données (par exemple, données valides sur front montant) définit les règles du protocole.

Communication parallèle

Les interfaces parallèles transmettent plusieurs bits en même temps. Le diagramme de temporisation doit indiquer le temps de préparation pour l’ensemble du bus. Tous les bits doivent être stables avant que l’arête de verrouillage ne se produise.

Meilleures pratiques pour la documentation 📝

Créer une documentation claire garantit que d’autres ingénieurs peuvent comprendre le système sans ambiguïté.

- Utilisez des étiquettes cohérentes: Nommez les signaux exactement comme ils apparaissent dans le code ou le schéma.

- Incluez les unités: Spécifiez toujours les unités de temps (ns, µs, cycles) sur l’axe.

- Mettez en évidence les chemins critiques: Utilisez des traits gras ou des couleurs pour indiquer les signaux les plus sensibles au temps.

- Annotez les violations: Si une violation est connue, marquez-la clairement plutôt que de la cacher.

- Tenez-le à jour: Mettez à jour les diagrammes chaque fois que la conception change. Les diagrammes obsolètes sont une source majeure de bogues.

Considérations avancées : domaines horaires multiples 🌐

Les systèmes modernes fonctionnent souvent avec plusieurs domaines horaires fonctionnant à des vitesses différentes. Un diagramme de temporisation pour ces systèmes doit montrer clairement la relation entre les horloges.

- Transitions entre horloges: Les données passant d’un domaine rapide à un domaine lent nécessitent une synchronisation soigneuse pour éviter la perte de données.

- Relations de phase: Si deux horloges partagent une source mais ont des phases différentes, le diagramme doit montrer le décalage de phase.

- Logique d’échange de signaux: Les ponts asynchrones entre domaines reposent sur des signaux d’échange. Le diagramme de temporisation doit montrer le cycle complet de demande-confirmation.

Le rôle de la simulation dans l’analyse de temporisation 💻

Avant la fabrication du matériel, les simulations vérifient les diagrammes de temporisation. Les ingénieurs utilisent des visualisateurs de formes d’onde pour comparer le comportement attendu aux résultats simulés.

- Analyse statique de temporisation: Calcule les retards dans le pire des cas sans simuler les formes d’onde réelles.

- Simulation dynamique de temporisation: Exécute une version virtuelle du circuit pour générer des formes d’onde réelles.

- Simulation post-couche: Tient compte des longueurs physiques des fils et de la capacité après la conception du circuit intégré.

Ces outils permettent aux ingénieurs de valider le diagramme de temporisation par rapport à la réalité physique. Si la simulation révèle une violation de configuration, la conception doit être révisée avant la fabrication.

Conclusion sur la précision de temporisation ✅

Maîtriser la création et l’interprétation des diagrammes de temporisation est une compétence fondamentale pour les professionnels techniques. Ces diagrammes combler le fossé entre la logique abstraite et la réalité physique. Ils garantissent que les signaux arrivent au moment voulu, dans l’état correct, et avec une stabilité suffisante pour que le système fonctionne. En respectant les éléments et contraintes décrits dans ce guide, les équipes peuvent réduire les erreurs et améliorer la fiabilité du système. Une attention aux détails dans ces représentations visuelles rapporte des bénéfices en stabilité et performance du produit final.

Qu’il s’agisse de travailler sur des interfaces mémoire à haute vitesse, des microcontrôleurs à faible consommation ou des bus de données complexes, les principes restent les mêmes. Le temps est la constante, et les signaux sont les variables. Comprendre leur relation est la clé du succès en ingénierie.