Les systèmes numériques dépendent d’une synchronisation précise pour fonctionner correctement. Sans une synchronisation exacte, la corruption des données, les plantages du système et les défaillances de sécurité deviennent inévitables. Un diagramme de temporisation fournit une représentation visuelle de la manière dont les signaux évoluent dans le temps, offrant une vue claire des relations entre les cycles d’horloge, la validité des données et les signaux de contrôle. Ce guide explore le rôle crucial des diagrammes de temporisation dans divers secteurs, en détaillant des exemples concrets et des solutions techniques aux défis courants.

🔍 Comprendre les fondamentaux

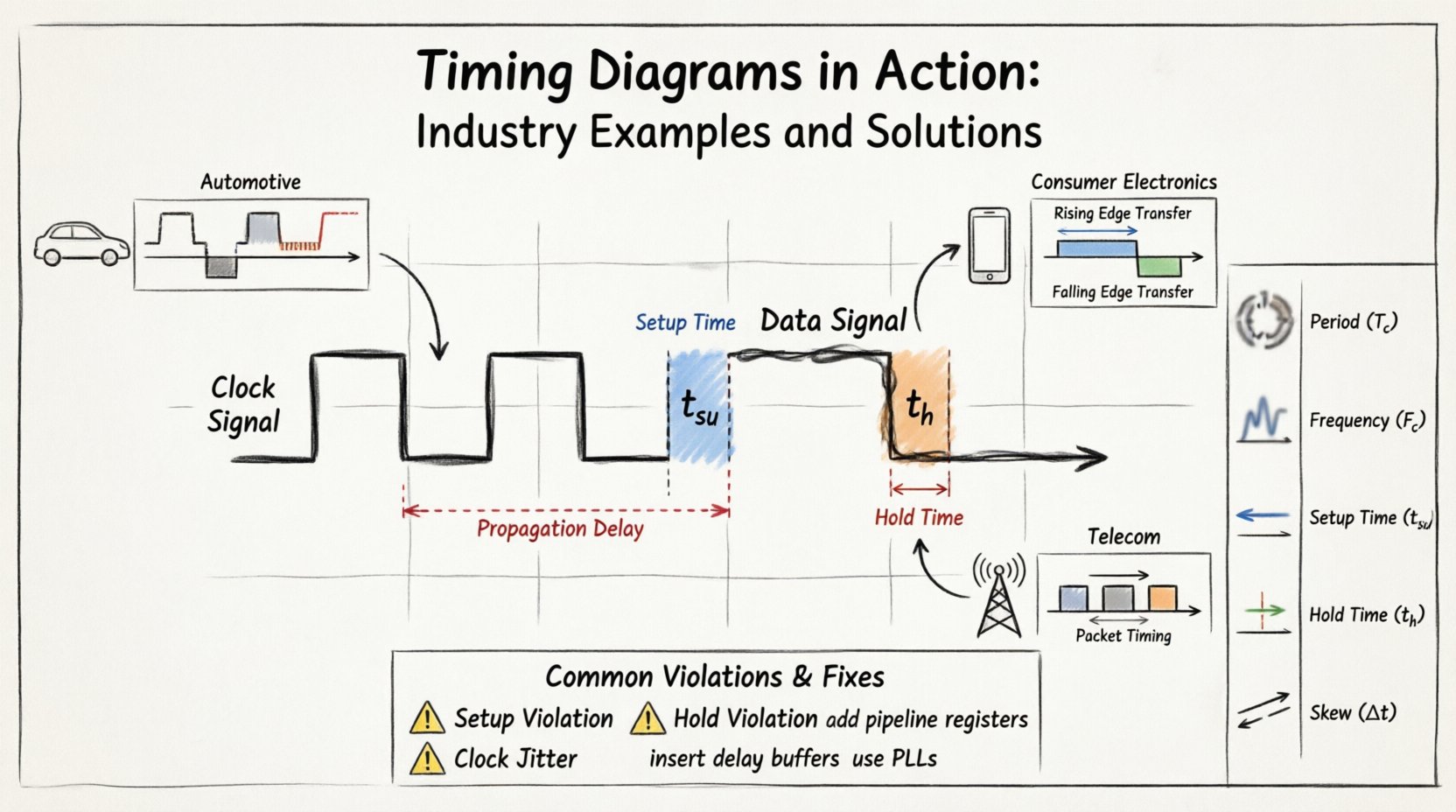

Avant de s’immerger dans des applications spécifiques, il est essentiel de maîtriser les composants fondamentaux d’un diagramme de temporisation. Ces diagrammes représentent le comportement des signaux par rapport à une horloge de référence. Ils ne sont pas simplement des dessins ; ce sont des contraintes mathématiques qui déterminent le comportement du matériel.

- Bords des signaux : La transition du bas vers le haut (front montant) ou du haut vers le bas (front descendant) déclenche des changements d’état dans la logique séquentielle.

- Période d’horloge : La durée entre deux bords consécutifs de même polarité définit le temps disponible pour que la logique se stabilise.

- Délai de propagation : Le temps nécessaire à un signal pour voyager depuis une broche d’entrée jusqu’à une broche de sortie à travers des portes logiques.

- Temps de préparation et temps de maintien : Des contraintes critiques garantissant que les données sont stables avant et après le front d’horloge.

Lorsque ces paramètres sont violés, le circuit peut entrer dans un état métastable, entraînant un comportement imprévisible. Les ingénieurs utilisent des diagrammes de temporisation pour vérifier que la mise en œuvre physique d’un design respecte ces exigences logiques.

🚗 Électronique automobile : temporisation critique pour la sécurité

L’industrie automobile exige le plus haut niveau de fiabilité. Les véhicules contiennent des dizaines d’unités de contrôle électroniques (ECU) qui communiquent via des bus tels que CAN (réseau de zone de contrôle), LIN (réseau d’interconnexion local) et FlexRay. L’analyse du temps ici ne concerne pas seulement la vitesse ; elle porte sur la déterminisme et la sécurité.

1. Arbitrage du bus CAN

Le bus CAN permet à plusieurs nœuds de communiquer sur un seul fil. Le diagramme de temporisation de l’arbitrage CAN révèle comment la priorité est déterminée lors de la contention du bus.

- Dominant vs. Récessif : Les niveaux logiques sont représentés par des états de tension. Un bit dominant (0) remplace un bit récessif (1).

- Synchronisation : Les nœuds s’alignent sur le bit de début de trame à l’aide de segments de synchronisation.

- Point d’échantillonnage : Les données sont échantillonnées à un pourcentage spécifique de la durée du bit afin d’éviter le bruit.

Si le point d’échantillonnage est trop proche de l’arête, le bruit peut provoquer des erreurs de bit. S’il est trop tardif, les données peuvent ne pas être stables. Les diagrammes de temporisation aident les ingénieurs à fixer correctement le point d’échantillonnage, généralement autour de 80 % de la durée du bit.

2. Échantillonnage ADC dans la fusion de capteurs

Les véhicules modernes utilisent plusieurs capteurs (radar, lidar, caméras) pour créer une perception de l’environnement. Les convertisseurs analogique-numérique (ADC) doivent échantillonner les signaux à des intervalles précis pour éviter le repliement de spectre.

- Jitter d’horloge : Les variations dans le timing des fronts d’horloge introduisent du bruit dans le signal numérisé.

- Latence : Le temps entre l’entrée du capteur et la sortie des données traitées doit être minimisé pour un contrôle en temps réel.

- Interleaving :Plusieurs ADC fonctionnent souvent en parallèle. Les diagrammes de temporisation assurent que leurs phases sont alignées afin d’éviter des lacunes dans les données.

📱 Électronique grand public : Interfaces à haute vitesse

Les appareils grand public privilégient les performances et l’efficacité énergétique. Les interfaces telles que la mémoire DDR et les liaisons d’affichage nécessitent des fenêtres de temporisation serrées pour atteindre un débit élevé sans augmenter la consommation d’énergie.

1. Interfaces mémoire DDR

La mémoire à double débit (DDR) transfère les données sur les fronts montants et descendants de l’horloge. Cela double le débit effectif, mais divise par deux la fenêtre de temps pour la stabilité des données.

| Paramètre | Définition | Conséquence de la violation |

|---|---|---|

| Temps de préparation | Temps pendant lequel les données doivent être stables avant le front de l’horloge | Perte de transfert de données, blocage du système |

| Temps de maintien | Temps pendant lequel les données doivent rester stables après le front de l’horloge | Données corrompues, inversion de bits |

| Désynchronisation d’horloge | Différence de temps d’arrivée de l’horloge entre différents circuits intégrés | Marge de temporisation réduite, instabilité |

| Cycle de fonctionnement | Ratio du temps haut sur la période totale | Performance déséquilibrée, augmentation de la jitter |

Dans les mémoires DDR4 et DDR5, le bus de commandes et d’adresses fonctionne souvent à une fréquence plus faible que le bus de données. Les diagrammes de temporisation doivent tenir compte des signaux d’impulsion source-synchrones (DQS) qui accompagnent les données pour indiquer les fenêtres valides.

2. Interfaces d’affichage (MIPI DSI)

Les appareils mobiles utilisent l’interface série d’affichage MIPI (DSI) pour relier le processeur à l’écran. Cette interface utilise des voies différentielles à haute vitesse.

- Mode commande basse consommation :Mode à faible consommation pour l’envoi de commandes, reposant sur une temporisation stricte pour les séquences de réveil.

- Mode données haute vitesse :Transmission à haute vitesse où la récupération de l’horloge est effectuée directement sur le flux de données.

- Temps de retour : Le temps nécessaire pour passer du mode transmission au mode réception sur la même voie.

Un décalage dans ces diagrammes de temporisation entraîne des artefacts à l’écran, des clignotements ou une perte totale de la sortie vidéo.

📡 Télécommunications : Latence et bande passante

Dans les télécommunications, le temporisation équivaut à la latence. Les délais de livraison des paquets et la synchronisation à travers les réseaux distribués sont essentiels pour des services comme le 5G et le trading à haute fréquence.

1. Signaux PCIe

La norme Peripheral Component Interconnect Express (PCIe) est largement utilisée pour connecter des composants à haute vitesse. Elle utilise des voies sérielles avec des horloges intégrées ou des horloges synchronisées à la source.

- Égalisation :L’intégrité du signal se dégrade avec la distance. Les diagrammes de temporisation montrent comment les filtres d’égalisation compensent les pertes.

- Entraînement de lien :Une séquence d’états temporisés pour établir la vitesse du lien et la largeur des voies.

- Contrôle de flux :Les fenêtres de temporisation pour le contrôle de flux basé sur les crédits empêchent les débordements de tampon.

2. PHY Ethernet

L’Ethernet standard repose sur une horloge partagée ou une récupération d’horloge. L’Ethernet Gigabit et au-delà utilisent le codage 8b/10b pour garantir un nombre suffisant de transitions pour la récupération d’horloge.

- Périodes d’inactivité :Des fenêtres de temporisation définies où aucune donnée n’est envoyée afin de maintenir la synchronisation.

- Délimiteur de début de trame :Un motif binaire spécifique qui marque le début d’un paquet, nécessitant un temps de détection précis.

- Intervalle entre paquets :Un délai obligatoire entre les paquets pour permettre au matériel de se réinitialiser.

⚠️ Violations de temporisation courantes et solutions

Même avec une conception soigneuse, des violations de temporisation surviennent. Identifier la cause racine nécessite d’analyser le diagramme de temporisation pour voir où les signaux s’écartent des attentes.

1. Violations de temps de préparation

Surviennent lorsque les données arrivent trop tard pour être capturées par l’arête de l’horloge.

- Causes :Profondeur excessive de logique, délais de câblage longs ou décalage d’horloge.

- Solutions :

- Insérer des registres de pipeline pour briser les longues trajectoires.

- Optimiser la synthèse logique pour réduire le nombre de portes.

- Ajuster la fréquence d’horloge pour fournir plus de temps.

2. Violations de temps de maintien

Se produit lorsque les données changent trop rapidement après l’edge d’horloge, écrasant la valeur capturée.

- Causes :Delais de chemin court, décalage d’horloge (clock skew) où l’horloge de capture arrive trop tard.

- Solutions :

- Insérer des buffers de retard dans le chemin de données.

- Utiliser des techniques de retiming pour équilibrer les chemins.

- S’assurer que le réseau de distribution d’horloge présente un décalage minimal.

3. Décalage d’horloge et jitter

Le décalage d’horloge est la différence entre les temps d’arrivée du signal d’horloge sur différents registres. Le jitter est la variation à court terme de l’edge d’horloge.

- Impact :Réduit la marge de temps effective disponible pour les données.

- Solutions :

- Utiliser des générateurs d’horloge à faible jitter.

- Concevoir des arbres d’horloge équilibrés avec des pistes de longueur égale.

- Mettre en œuvre des boucles à verrouillage de phase (PLL) pour nettoyer les signaux d’horloge.

✅ Meilleures pratiques pour l’implémentation

Obtenir un timing robuste nécessite une approche systématique tout au long du cycle de conception. La documentation et la vérification sont aussi importantes que le circuit lui-même.

1. Définir les contraintes de timing tôt

Ne pas attendre la phase d’implémentation pour définir les exigences de timing. Documenter les fréquences d’horloge, les délais d’entrée et les délais de sortie dans la spécification du design. Cela garantit que tous les intervenants comprennent les limites du système.

2. Utiliser l’analyse statique du timing

Les outils d’analyse statique du timing (STA) calculent les chemins de délai au pire cas sans simuler chaque combinaison d’entrée. Cette méthode est efficace et couvre tous les états possibles, garantissant qu’aucune violation de timing ne soit manquée.

3. Valider avec la simulation

Bien que le STA soit puissant, la simulation dynamique fournit une vue du comportement des signaux dans des conditions spécifiques. Utilisez la simulation pour vérifier les chemins critiques, en particulier ceux impliquant de la logique asynchrone ou des machines d’état complexes.

4. Considérations de conception physique

Le layout physique de la puce ou de la carte influence directement le timing.

- Longueur des pistes :Les pistes plus longues introduisent une plus grande capacité et une résistance accrue, augmentant ainsi le délai.

- Couplage crosstalk :Les signaux voisins peuvent induire du bruit, provoquant des transitions erronées.

- Bruit sur l’alimentation :Les baisses de tension peuvent ralentir les vitesses de commutation des portes.

🛠️ Dépannage de scénarios du monde réel

Lorsqu’un système ne parvient pas à respecter les contraintes de timing, un processus de débogage structuré est nécessaire. Les étapes suivantes décrivent une approche logique pour résoudre les problèmes de timing.

- Étape 1 : Identifier le chemin.Localisez le chemin spécifique entre registres qui cause l’échec. Consultez le rapport de timing pour le slack le plus négatif.

- Étape 2 : Analyser les formes d’onde.Utilisez un visualiseur de diagramme de timing pour examiner les transitions réelles des signaux. Comparez-les aux valeurs attendues.

- Étape 3 : Vérifier l’horloge.Vérifiez la qualité du signal d’horloge. Recherchez des perturbations, des distorsions du rapport cyclique ou des parasites.

- Étape 4 : Revue des contraintes.Assurez-vous que les contraintes dans le fichier de conception correspondent à la réalité physique du matériel.

- Étape 5 : Itérer.Apportez des modifications à la logique ou au layout, puis relancez l’analyse de timing.

📊 Résumé des paramètres de timing

Pour faciliter la consultation rapide, voici un résumé des paramètres de timing clés utilisés dans divers secteurs.

| Paramètre | Symbole | Unité typique | Description |

|---|---|---|---|

| Période | Tc | ns | Intervalle entre deux fronts consécutifs de l’horloge |

| Fréquence | Fc | Hz | Inverse de la période |

| Temps de préparation | tsu | ns | Stabilité des données requise avant l’edge de l’horloge |

| Temps de maintien | th | ns | Stabilité des données requise après l’edge de l’horloge |

| Délai de propagation | tpd | ns | Temps nécessaire au signal pour traverser la logique |

| Désynchronisation | Δt | ps | Différence de temps d’arrivée de l’horloge |

🔄 Gestion des conceptions asynchrones

Tous les systèmes ne fonctionnent pas sur une seule horloge. Les conceptions asynchrones impliquent des données qui traversent différents domaines d’horloge. Cela introduit le risque de métastabilité, où une bascule entre dans un état indéfini.

- Chaînes de synchronisation : Utilisez un synchroniseur à plusieurs étages (généralement deux bascules) pour permettre au signal de se stabiliser avant d’être utilisé.

- Protocoles d’échange de mains : Mettez en œuvre des mécanismes de demande-confirmation pour garantir que le récepteur est prêt avant l’envoi des données.

- Tampons FIFO : Utilisez des structures de mémoire FIFO pour déconnecter les vitesses du producteur et du consommateur.

Les diagrammes de temporisation pour les conceptions asynchrones montrent la relation entre les deux horloges indépendantes. L’essentiel est de s’assurer que le chemin des données dispose de suffisamment de temps pour se stabiliser avant que l’horloge réceptrice ne l’échantillonne.

🌟 Réflexions finales

Les diagrammes de temporisation sont la charpente de la vérification des systèmes numériques. Ils combler le fossé entre la logique abstraite et la réalité physique. En comprenant les subtilités du temps de préparation, du temps de maintien, de la désynchronisation d’horloge et du jitter, les ingénieurs peuvent concevoir des systèmes robustes, efficaces et fiables.

Que ce soit dans les systèmes de sécurité automobile, les appareils grand public ou les infrastructures de télécommunications, les principes restent les mêmes. La précision dans le temporisation conduit à la précision dans les performances. Un suivi continu et le respect des meilleures pratiques garantissent que les conceptions restent fonctionnelles tout au long de leur cycle de vie. À mesure que la technologie évolue et que les vitesses augmentent, l’importance de l’analyse détaillée du temporisation ne fera que croître.

Pour les équipes souhaitant améliorer la qualité de leurs conceptions, consacrer du temps aux diagrammes de timing précis et aux flux de vérification est essentiel. Cela réduit les risques, diminue les coûts de débogage et garantit que le produit final répond à ses spécifications. Avec les bons outils et méthodologies, les défis liés au timing deviennent des contraintes gérables plutôt que des obstacles.