Les systèmes numériques reposent sur une synchronisation précise pour fonctionner correctement. Lorsque les signaux arrivent au mauvais moment, des erreurs logiques se produisent, entraînant un comportement imprévisible. Comprendre comment analyser et corriger ces problèmes est essentiel pour quiconque étudie la logique numérique, l’ingénierie informatique ou l’électronique. Ce guide traite des concepts fondamentaux et des étapes pratiques pour identifier et résoudre les problèmes de synchronisation rencontrés dans les circuits séquentiels et la transmission de données.

Comprendre les signaux d’horloge et leurs fronts ⏱️

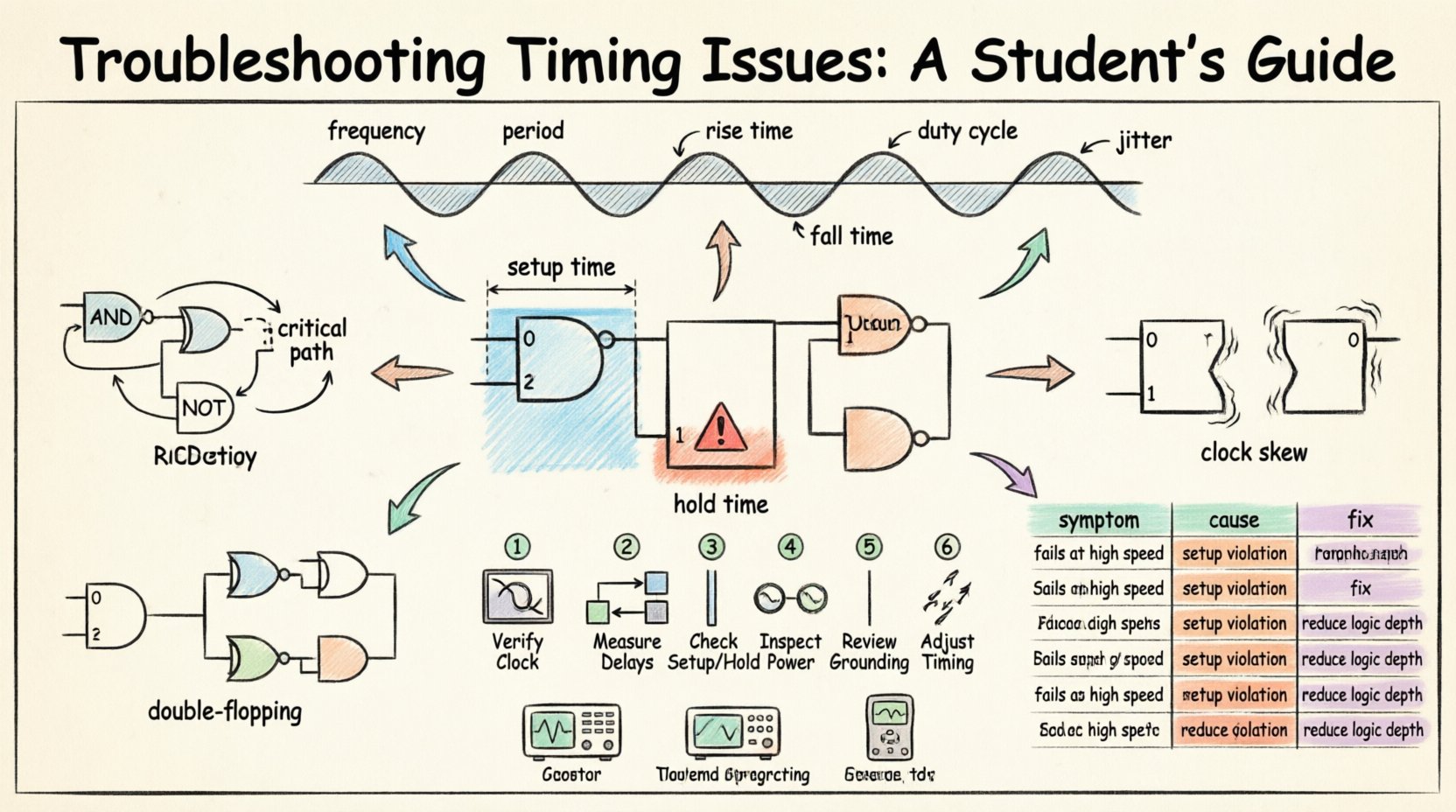

Au cœur de la plupart des conceptions numériques se trouve le signal d’horloge. Cette onde périodique détermine quand les données sont échantillonnées et quand les changements d’état ont lieu. La résolution des problèmes commence souvent par la vérification de l’intégrité de ce signal fondamental.

- Fréquence et période : La fréquence d’horloge détermine la vitesse de fonctionnement. La période est la durée temporelle d’un cycle complet. Si le circuit nécessite une horloge de 100 MHz, la période est de 10 nanosecondes. Toute déviation ici affecte toute la logique en aval.

- Temps de montée et temps de descente : Une onde carrée parfaite est théorique. Les signaux réels ont des temps de montée et de descente finis. Si la transition est trop lente, le signal peut passer trop de temps dans la région de tension indéfinie, entraînant des commutations multiples ou des erreurs logiques.

- Cycle de travail : Il s’agit du rapport entre le temps pendant lequel le signal est à l’état haut et la période totale. Un cycle de travail de 50 % est la norme, mais certaines conceptions exigent des cycles asymétriques. Les écarts peuvent décaler les marges de temps nécessaires pour les exigences de mise en place ou de maintien.

Lors de l’inspection d’un circuit, utilisez un oscilloscope ou un analyseur logique pour visualiser la forme d’onde de l’horloge. Recherchez des pics de bruit, des oscillations ou un jitter excessif. Le jitter désigne l’écart entre le front de l’horloge et sa position idéale dans le temps. Un jitter élevé réduit la marge de temps effective disponible pour que les données se stabilisent.

Violations de temps de mise en place et de maintien ⚠️

Ce sont les violations de synchronisation les plus fréquentes rencontrées dans la conception de logique séquentielle. Les bascules et les verrous ont des exigences spécifiques concernant le moment où les données doivent être stables par rapport au front de l’horloge.

Temps de mise en place

Le temps de mise en place est la durée minimale avant le front de l’horloge pendant laquelle les données doivent être stables. Si les données changent trop près du front de l’horloge, la bascule peut ne pas capturer la bonne valeur.

- La contrainte : Le délai de propagation de la logique combinatoire alimentant la bascule doit être inférieur à la période d’horloge moins le temps de mise en place.

- Le symptôme : Le système pourrait fonctionner à des fréquences plus faibles, mais échouer à mesure que la vitesse augmente. Des erreurs aléatoires de bits apparaissent souvent en sortie.

- La solution : Réduire la profondeur logique entre les registres, augmenter la période d’horloge ou utiliser des composants plus rapides.

Temps de maintien

Le temps de maintien est la durée minimale après le front de l’horloge pendant laquelle les données doivent rester stables. Si les données changent trop tôt après le front de l’horloge, la bascule peut perdre la valeur capturée.

- La contrainte : Le délai de propagation de la logique combinatoire doit être supérieur au temps de maintien de la bascule de destination.

- Le symptôme : Les violations de maintien surviennent souvent indépendamment de la fréquence. Cela est dû au fait que le délai est absolu, et non relatif à la période.

- La solution : Ajouter des tampons de retard dans le chemin des données pour ralentir le signal, ou reconfigurer la logique pour réduire le délai.

Il est crucial de distinguer ces deux cas. Les violations de mise en place dépendent de la fréquence, tandis que les violations de maintien dépendent du chemin. Une erreur courante consiste à essayer de corriger une violation de maintien en ralentissant l’horloge ; cela ne fonctionnera pas et pourrait même aggraver la situation.

Delais de propagation et analyse des chemins 📉

Les signaux ne se propagent pas instantanément. Chaque fil, porte et composant introduit un délai. Analyser ces délais est crucial pour garantir que les données arrivent à temps.

- Délai de logique combinatoire : Il s’agit du temps nécessaire à un signal pour traverser des portes telles que ET, OU et NON. Les longues chaînes de portes engendrent une latence importante.

- Délai d’interconnexion : Sur une carte physique, les fils présentent une capacité et une résistance. Les traces plus longues introduisent davantage de délai. Cela est souvent modélisé comme un réseau RC.

- Délai entre broches : Le temps allant d’une entrée d’horloge à une sortie de données dans un composant. Cela est généralement indiqué dans les fiches techniques.

Lors du dépannage, tracez le chemin critique. Il s’agit du chemin de délai le plus long entre deux éléments séquentiels. Si ce chemin critique dépasse la période d’horloge, la conception échouera. Pour le trouver, calculez la somme des délais pour tous les chemins possibles et identifiez le maximum.

Dérive d’horloge et jitter 📶

Même si la source d’horloge est parfaite, le signal pourrait arriver à différents composants à des moments différents. Ce phénomène est connu sous le nom de dérive.

- Dérive d’horloge : Cela se produit lorsque le signal d’horloge parcourt des distances différentes pour atteindre différents bascules. Une dérive positive retarde l’horloge de capture, ce qui allonge le temps de préparation mais réduit le temps de maintien. Une dérive négative réduit le temps de préparation mais allonge le temps de maintien.

- Jitter d’horloge : Des variations à court terme dans le timing de l’arête d’horloge. Le jitter réduit le budget de temps disponible pour la préparation des données.

- Drift : Des changements lents de la fréquence d’horloge au fil du temps dus aux fluctuations de température ou d’alimentation électrique.

La dérive est souvent gérée par la synthèse de l’arbre d’horloge dans les conceptions complexes. Dans les projets étudiants, elle est généralement minimisée en acheminant les traces d’horloge de manière équilibrée et en les maintenant courtes. Si une dérive est suspectée, mesurez l’horloge à plusieurs points du circuit simultanément.

Métastabilité et entrées asynchrones 🌀

Lorsque les données changent au même moment que l’arête d’horloge, une bascule entre dans un état métastable. Elle ne se stabilise pas immédiatement sur 0 ou 1, mais reste à un niveau de tension intermédiaire.

- Le risque :La métastabilité peut se propager dans le système, provoquant des erreurs logiques difficiles à reproduire.

- Signaux asynchrones :Les entrées provenant d’interrupteurs externes ou de ports de communication ne sont souvent pas synchronisées avec l’horloge interne. Elles doivent être synchronisées.

- Double bascule : Une technique courante pour résoudre la métastabilité consiste à faire passer le signal à travers deux bascules en série. La première capte l’état métastable, et la seconde le résout lors du cycle suivant.

Traitez toujours les entrées asynchrones comme des sources potentielles de métastabilité. N’appelez pas directement ces entrées sur une logique qui nécessite un timing strict. Utilisez des circuits de synchronisation pour assurer un transfert de données sécurisé entre des domaines d’horloge différents.

Un workflow de dépannage étape par étape 🛠️

Lorsqu’un problème de timing survient, suivez une approche structurée pour isoler la cause. Les modifications aléatoires sont peu susceptibles de donner des résultats.

- Vérifiez l’horloge : Vérifiez la fréquence, le cycle de travail et l’amplitude. Assurez-vous que le signal est stable et propre.

- Mesurez les délais :Utilisez un analyseur logique pour capturer les signaux d’entrée et de sortie. Mesurez le délai de propagation réel du chemin.

- Vérifiez les temps de setup et de hold : Calculez si le chemin respecte les contraintes de setup et de hold en fonction des délais mesurés.

- Vérifiez l’alimentation : Les baisses de tension peuvent ralentir les portes. Assurez-vous que l’alimentation est stable et fournit un courant suffisant.

- Revoyez le blindage : Un mauvais blindage peut introduire du bruit qui simule des erreurs de temporisation. Vérifiez les boucles de masse et les chemins de retour partagés.

- Ajustez la temporisation : Si la conception est souple, ajustez la fréquence d’horloge ou ajoutez des tampons pour équilibrer le chemin.

La documentation est essentielle pendant ce processus. Enregistrez les formes d’onde et les mesures. Ces données aident à comparer le comportement attendu avec les performances réelles.

Tableau de référence des erreurs courantes 📊

Utilisez ce tableau comme référence rapide pour diagnostiquer des symptômes spécifiques.

| Symptôme observé | Cause probable | Action recommandée |

|---|---|---|

| Le système échoue à haute vitesse | Violation du temps de setup | Réduisez la profondeur logique ou augmentez la période d’horloge |

| Le système échoue à basse vitesse | Violation du temps de hold | Ajoutez des tampons de délai au chemin de données |

| Inversions aléatoires de bits | Bruit ou jitter du signal | Vérifiez l’écranage et la stabilité de l’alimentation |

| Sortie bloquée ou redémarrée | Métastabilité | Mettez en œuvre des chaînes de synchronisation |

| Comportement instable | Désynchronisation d’horloge | Équilibrer les longueurs des pistes d’horloge |

| Aucune sortie du tout | Horloge non activée | Vérifier la distribution d’horloge et les signaux d’activation |

Outils et instruments 📏

Bien que les outils de simulation soient utiles, la vérification physique nécessite souvent des équipements spécifiques. Comprendre comment utiliser correctement ces instruments fait partie des compétences en dépannage.

- Oscilloscope :Essentiel pour visualiser les niveaux de tension et la forme du signal. Utilisez des sondes à haute impédance pour éviter de charger le circuit.

- Analyseur logique :Meilleur pour les signaux numériques. Il capte l’état logique (0 ou 1) au fil du temps. Il peut déclencher sur des motifs spécifiques pour isoler les erreurs.

- Compteur de fréquence :Utilisé pour vérifier la fréquence exacte de la source d’horloge si un oscilloscope n’est pas disponible.

Assurez-vous que les sondes sont correctement compensées. Une sonde non compensée peut déformer la forme du signal, entraînant des conclusions erronées sur les temps de montée et les délais.

Considérations finales sur l’intégrité du signal 🔒

Les problèmes de temporisation sont souvent des symptômes de problèmes plus larges d’intégrité du signal. À mesure que les circuits deviennent plus rapides, les propriétés physiques de la carte deviennent plus importantes.

- Couplage indésirable :Les signaux sur des fils adjacents peuvent s’interférer mutuellement. Maintenez les lignes à haute vitesse séparées des lignes sensibles.

- Adaptation d’impédance :Si l’impédance de la piste ne correspond pas à celle du conducteur ou du récepteur, des réflexions se produisent. Ces réflexions peuvent ressembler à des délais de temporisation.

- Effets thermiques :À mesure que les composants chauffent, leurs caractéristiques électriques changent. Cela peut modifier les délais de propagation et entraîner des échecs de temporisation sous charge.

Concevoir pour la temporisation exige une vision globale. Ce n’est pas seulement une question de portes logiques ; c’est une question du support physique par lequel les signaux voyagent. En suivant ces principes, les étudiants peuvent construire des systèmes robustes qui fonctionnent de manière fiable dans diverses conditions.

Une pratique régulière avec des équipements réels aide à intégrer ces concepts. La théorie fournit le cadre, mais le dépannage pratique développe l’intuition nécessaire pour résoudre efficacement des problèmes complexes de temporisation.