Dalam arsitektur perangkat lunak modern dan desain sistem, memvisualisasikan bagaimana komponen berinteraksi seiring waktu sangat penting. Sebuah diagram waktumemberikan gambaran tepat mengenai perilaku sinyal, transisi status, dan batasan temporal dalam suatu sistem. Bagi insinyur perangkat lunak, menguasai diagram ini berarti memahami latensi, konkurensi, dan urutan kejadian yang tepat yang mendorong keandalan sistem.

Berbeda dengan bagan alir tingkat tinggi, diagram waktu berfokus pada kapandaripada hanya apa. Mereka sangat penting untuk mendiagnosis kondisi persaingan, mengoptimalkan waktu respons API, dan memastikan integrasi perangkat keras-perangkat lunak berjalan sesuai rencana. Panduan ini menguraikan mekanisme, aplikasi, dan praktik terbaik untuk membuat dan membaca diagram waktu secara efektif.

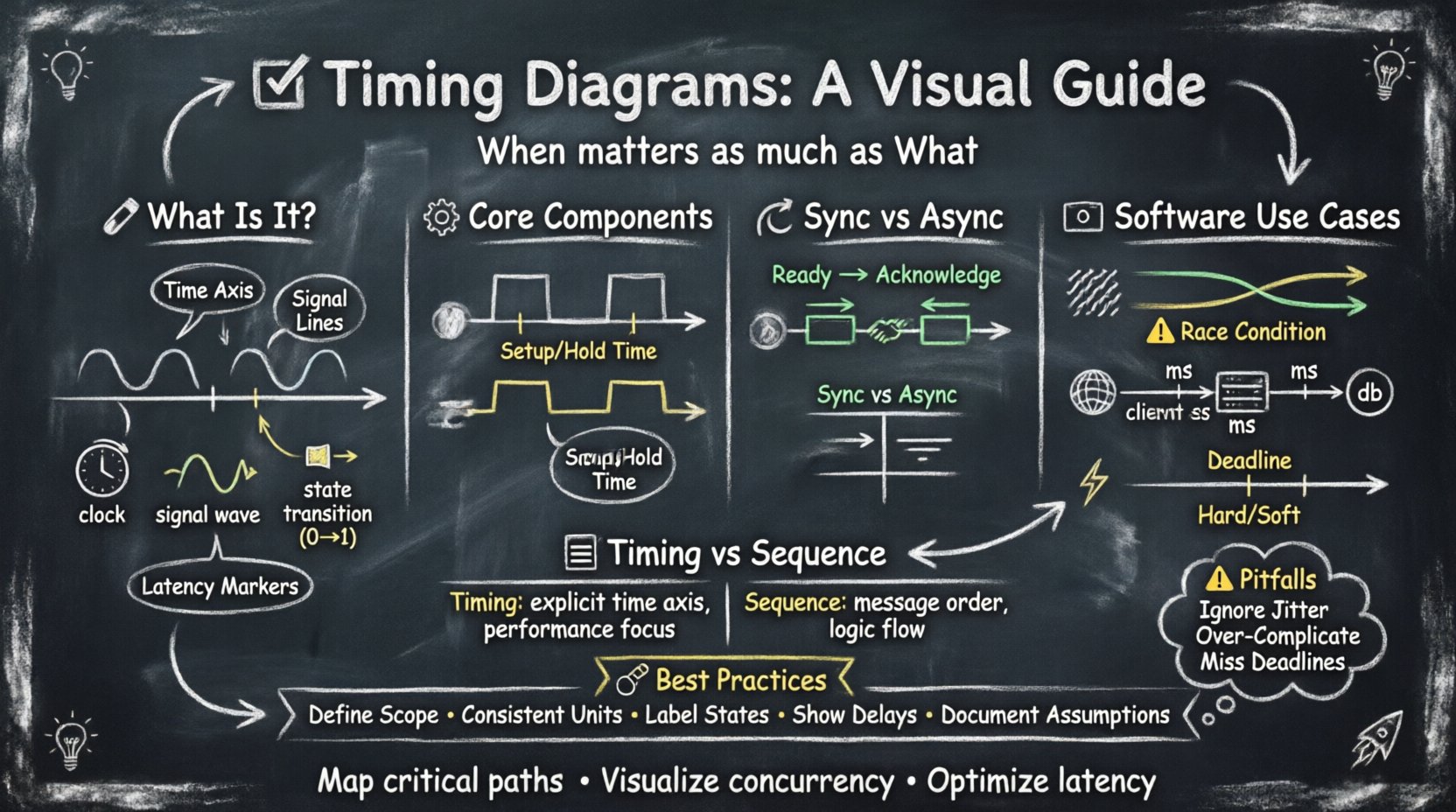

🔍 Apa Itu Diagram Waktu?

Diagram waktu adalah representasi grafis yang menunjukkan bagaimana sinyal berubah seiring waktu. Diagram ini memplot waktu pada sumbu horizontal dan status sinyal pada sumbu vertikal. Visualisasi ini membantu insinyur menganalisis hubungan waktu antara bagian-bagian berbeda dalam suatu sistem, baik yang melibatkan register perangkat keras, paket jaringan, atau thread perangkat lunak.

Ciri kunci meliputi:

- Sumbu Waktu:Mewakili perkembangan kejadian, biasanya mengalir dari kiri ke kanan.

- Garis Sinyal:Garis vertikal yang mewakili variabel, kabel, atau aliran data tertentu.

- Perubahan Status:Transisi horizontal yang menunjukkan perubahan dari 0 ke 1, atau dari idle ke aktif.

- Penanda Latensi:Indikator yang menunjukkan jeda antara permintaan dan respons.

Bagi insinyur perangkat lunak, diagram ini menjadi jembatan antara logika abstrak dan waktu eksekusi fisik. Mereka mengungkapkan hambatan yang sering disembunyikan oleh diagram urutan.

⚙️ Komponen Utama Diagram Waktu

Membuat diagram waktu yang jelas membutuhkan perhatian terhadap elemen-elemen tertentu. Setiap komponen menyampaikan informasi penting mengenai perilaku sistem.

1. Sinyal dan Status

Sinyal mewakili jalur data atau kontrol. Dalam konteks perangkat lunak, ini bisa mewakili pemanggilan fungsi, kunci thread, atau paket jaringan. Status menentukan status saat ini dari suatu sinyal:

- Aktif Tinggi:Sinyal bernilai benar, diaktifkan, atau mengirim data.

- Aktif Rendah:Sinyal bernilai salah, dinonaktifkan, atau sedang menunggu.

- High-Z (Impedansi Tinggi): Sinyal terputus atau mengambang.

- Tidak diketahui:Statusnya tidak pasti.

2. Skala dan Satuan Waktu

Akurasi tergantung pada skala. Mikrodetik penting untuk sistem waktu nyata, sementara milidetik mungkin sudah cukup untuk API web. Konsistensi dalam satuan mencegah salah tafsir.

- Skala Tetap:Interval seragam di seluruh diagram.

- Skala Relatif:Berfokus pada durasi antara peristiwa tertentu.

- Skala Logaritmik:Digunakan ketika peristiwa meliputi rentang waktu yang sangat berbeda.

3. Peristiwa dan Transisi

Peristiwa memicu perubahan status. Sudut naik menunjukkan transisi dari rendah ke tinggi. Sudut turun menunjukkan transisi dari tinggi ke rendah. Dalam perangkat lunak, ini setara dengan interupsi yang aktif, kunci yang diperoleh, atau paket yang tiba.

⏱️ Komunikasi Sinkron vs. Asinkron

Diagram waktu sangat berguna untuk membedakan antara interaksi sinkron dan asinkron. Memahami perbedaan ini kunci dalam merancang sistem terdistribusi yang tangguh.

Waktu Sinkron

Sistem sinkron bergantung pada sinyal jam bersama. Peristiwa terjadi pada interval tertentu yang ditentukan oleh jam ini. Pendekatan ini memastikan komponen beroperasi secara sinkron.

- Sinyal Jam:Pulsasi teratur yang menentukan waktu.

- Kesesuaian Data:Data harus stabil sebelum tepi jam memicu perubahan.

- Waktu Siap dan Waktu Tahan:Kendala yang menentukan berapa lama sebelum dan sesudah tepi jam data harus tetap stabil.

Dalam perangkat lunak, ini menyerupai sinkronisasi thread di mana operasi harus selesai sebelum siklus berikutnya dimulai. Ini dapat diprediksi tetapi dapat menimbulkan waktu kosong jika satu komponen lebih lambat.

Waktu Asinkron

Sistem asinkron tidak bergantung pada jam global. Komunikasi didorong oleh permintaan dan pengakuan. Ini memungkinkan komponen beroperasi pada kecepatan yang berbeda.

- Protokol Handshake:Sinyal seperti ‘Siap’ dan ‘Konfirmasi’ mengelola aliran.

- Latensi Variabel:Waktu respons tergantung pada beban sistem.

- Berdasarkan Peristiwa:Aksi hanya dipicu ketika kondisi terpenuhi.

Model ini sangat cocok dengan layanan web modern, di mana server memproses permintaan dan mengembalikan respons tanpa menunggu ketukan jam global.

🖥️ Diagram Waktu dalam Teknik Perangkat Lunak

Meskipun sering dikaitkan dengan perangkat keras, diagram waktu memiliki nilai penting dalam pengembangan perangkat lunak. Mereka membantu memvisualisasikan konkurensi, latensi jaringan, dan rantai ketergantungan.

1. Konkurensi dan Kondisi Persaingan

Ketika beberapa thread mengakses sumber daya bersama, waktu menjadi krusial. Diagram dapat menggambarkan jendela eksekusi yang tumpang tindih.

- Thread A:Mendapatkan kunci pada t1.

- Thread B:Menunggu kunci hingga t2.

- Konflik:Jika Thread B mencoba mengakses data sebelum t2, terjadi kondisi persaingan.

Memvisualisasikan timeline ini membantu mengidentifikasi di mana primitif sinkronisasi (mutex, semafor) diperlukan untuk mencegah kerusakan data.

2. Analisis Latensi API

Bagi insinyur backend, diagram waktu memetakan masa hidup permintaan HTTP.

- Kirim Klien:Waktu yang dibutuhkan untuk mengirim data.

- Transit Jaringan:Waktu tempuh bolak-balik (RTT).

- Pemrosesan Server:Waktu yang dihabiskan untuk menghitung logika.

- Pertanyaan Basis Data:Waktu yang dihabiskan untuk mengambil data.

- Pengiriman Respons:Waktu untuk mengembalikan data ke klien.

Memecah bagian-bagian ini memungkinkan insinyur menentukan di mana upaya optimasi harus difokuskan. Apakah bottleneck terletak pada basis data, jaringan, atau logika aplikasi?

3. Sistem Real-Time

Perangkat lunak bawaan dan sistem operasi real-time (RTOS) membutuhkan jaminan waktu yang ketat. Diagram waktu menentukan batas waktu.

- Batas Waktu Keras:Keterlambatan batas waktu menyebabkan kegagalan sistem.

- Batas Waktu Lunak:Keterlambatan batas waktu menurunkan kinerja tetapi tidak membuat sistem gagal.

Desainer menggunakan diagram ini untuk menjadwalkan tugas, memastikan proses kritis berjalan dalam jendela waktu yang telah ditetapkan.

📊 Diagram Waktu vs. Diagram Urutan

Insinyur sering keliru membedakan diagram waktu dengan diagram urutan. Keduanya menunjukkan interaksi, tetapi memiliki tujuan yang berbeda. Tabel di bawah ini menjelaskan perbedaannya.

| Fitur | Diagram Waktu | Diagram Urutan |

|---|---|---|

| Fokus Utama | Durasi waktu dan tingkat sinyal | Urutan pesan dan alur logika |

| Representasi Waktu | Sumbu waktu eksplisit (ms, µs) | Alur vertikal implisit (atas ke bawah) |

| Kongurensi | Menunjukkan eksekusi yang tumpang tindih dengan jelas | Menunjukkan paralelisme tetapi kurang presisi |

| Kasus Penggunaan | Penyesuaian kinerja, integrasi perangkat keras | Persyaratan fungsional, alur logika |

| Kompleksitas | Tinggi (memerlukan data yang akurat) | Sedang (logika abstrak) |

Gunakan diagram urutan untuk mendokumentasikan bagaimana suatu fitur bekerja. Gunakan diagram waktu untuk mendokumentasikan seberapa cepat fitur tersebut bekerja dan apakah memenuhi batasan kinerja.

🛠️ Praktik Terbaik untuk Membuat Diagram Waktu

Untuk memastikan diagram ini tetap menjadi alat yang bermanfaat daripada benda yang berantakan, ikuti panduan berikut.

1. Tentukan Lingkup dengan Jelas

Jangan mencoba menggambarkan seluruh sistem sekaligus. Fokus pada interaksi tertentu, seperti permintaan login atau operasi baca sensor. Menyempitkan lingkup mencegah kelebihan visual.

2. Gunakan Satuan yang Konsisten

Mencampurkan detik dan milidetik dalam diagram yang sama menyebabkan kebingungan. Pilih satuan yang memberikan resolusi terbaik untuk peristiwa yang diukur.

3. Beri Label pada Status Aktif

Tandai dengan jelas kapan suatu sinyal aktif. Gunakan anotasi atau pewarnaan (jika didukung oleh alat Anda) untuk menyoroti jendela kritis, seperti periode pengambilan kunci.

4. Tunjukkan Penundaan Secara Jelas

Jarak antar sinyal harus mewakili penundaan yang sebenarnya. Gunakan garis putus-putus atau kurung untuk menunjukkan waktu tunggu. Ini membantu mengidentifikasi di mana sistem sedang idle dibandingkan di mana sistem sedang memproses.

5. Dokumentasikan Asumsi

Catat kondisi di mana diagram tetap berlaku. Apakah ini dalam beban puncak? Dalam kondisi normal? Dokumentasi memastikan diagram tetap valid seiring perkembangan sistem.

⚠️ Kesalahan Umum yang Harus Dihindari

Menghindari kesalahan sama pentingnya dengan mengetahui cara menggambar. Berikut ini adalah kesalahan umum yang mengurangi nilai diagram waktu.

- Mengabaikan Jitter:Mengasumsikan sinyal berjalan secara sempurna halus. Sistem nyata memiliki variasi. Tunjukkan jitter di tempat yang relevan.

- Terlalu Memperumit:Memasukkan setiap sinyal kecil. Fokus pada jalur kritis.

- Mengabaikan Batas Waktu:Gagal menandai batas waktu yang ketat dapat menyebabkan sistem yang berfungsi tetapi gagal saat mengalami tekanan.

- Kurangnya Konteks:Diagram tanpa legenda atau definisi satuan menjadi tidak berguna bagi insinyur baru.

- Representasi Statis:Waktu berubah sesuai beban. Diagram statis harus diberi label kondisi beban (misalnya, “100 Permintaan/Detik”).

🔧 Menganalisis Batasan Waktu

Di luar menggambar, insinyur harus menganalisis data dalam diagram. Analisis ini mendorong optimalisasi.

1. Analisis Jalur Kritis

Identifikasi urutan peristiwa terpanjang yang saling tergantung. Jalur ini menentukan waktu minimum yang dibutuhkan untuk menyelesaikan suatu tugas. Optimalisasi jalur kritis mengurangi latensi keseluruhan.

2. Peluang Paralelisme

Cari sinyal yang dapat berjalan secara bersamaan. Jika dua tugas tidak saling tergantung, jadwalkan keduanya secara paralel untuk menghemat waktu. Diagram waktu membuat tumpang tindih ini terlihat jelas.

3. Identifikasi Kemacetan

Segment horizontal yang panjang menunjukkan waktu tunggu. Jika suatu proses menunggu terlalu lama untuk suatu sumber daya, maka sumber daya tersebut adalah kemacetan. Pertimbangkan caching, antrian, atau peningkatan perangkat keras.

📝 Contoh Praktis: Waktu Permintaan Basis Data

Pertimbangkan skenario di mana aplikasi web melakukan permintaan ke basis data. Diagram waktu untuk alur ini mungkin tampak seperti ini:

- Kedatangan Permintaan: Klien mengirimkan permintaan pada t=0.

- Load Balancer: Mengarahkan permintaan pada t=5ms.

- Server Aplikasi: Memproses logika pada t=10ms.

- Koneksi DB: Membangun koneksi pada t=15ms.

- Eksekusi Query: Berjalan selama 50ms.

- Pengembalian Respons: Data dikirim kembali pada t=65ms.

Dalam contoh ini, waktu eksekusi query mendominasi latensi total. Diagram waktu menunjukkan bahwa mengoptimalkan indeks basis data lebih efektif daripada mengoptimalkan logika load balancer.

🚀 Pikiran Akhir tentang Visualisasi Waktu

Diagram waktu adalah alat yang kuat bagi insinyur yang perlu memahami perilaku temporal sistem mereka. Mereka melampaui kebenaran logis untuk menangani kinerja dan keandalan. Dengan memvisualisasikan sinyal, status, dan penundaan, tim dapat membuat keputusan yang terinformasi mengenai arsitektur dan optimasi.

Ketika merancang sistem yang kompleks, selalu pertimbangkan aspek waktu. Fungsi yang berjalan secara logis bisa gagal di bawah tekanan jika batasan waktu diabaikan. Sertakan diagram ini dalam dokumentasi desain Anda untuk memastikan kejelasan dan ketepatan.

Ingat, tujuannya bukan hanya menggambar gambar, tetapi memahami aliran waktu dalam perangkat lunak Anda. Pemahaman ini mengarah pada sistem yang tidak hanya berfungsi, tetapi juga responsif dan stabil.

Mulailah dengan memetakan interaksi kritis Anda. Identifikasi di mana waktu paling penting. Gunakan alat visual ini untuk menyampaikan hubungan temporal yang kompleks kepada tim Anda. Dengan latihan, diagram waktu akan menjadi bagian integral dari alat insinyur Anda.