Di dunia yang rumit dari elektronika digital dan desain sistem, komunikasi antar komponen sangat bergantung pada hubungan temporal yang tepat. Diagram waktu berfungsi sebagai bahasa visual yang menggambarkan hubungan-hubungan tersebut. Ini adalah representasi grafis yang menunjukkan bagaimana sinyal berubah seiring waktu. Tanpa alat ini, melakukan debugging interaksi perangkat keras atau memverifikasi perilaku logika akan hampir mustahil. Panduan ini mengeksplorasi elemen-elemen penting, parameter, dan strategi membaca yang diperlukan untuk memahami diagram-diagram ini secara efektif.

Apa Sebenarnya Diagram Waktu Itu? 📐

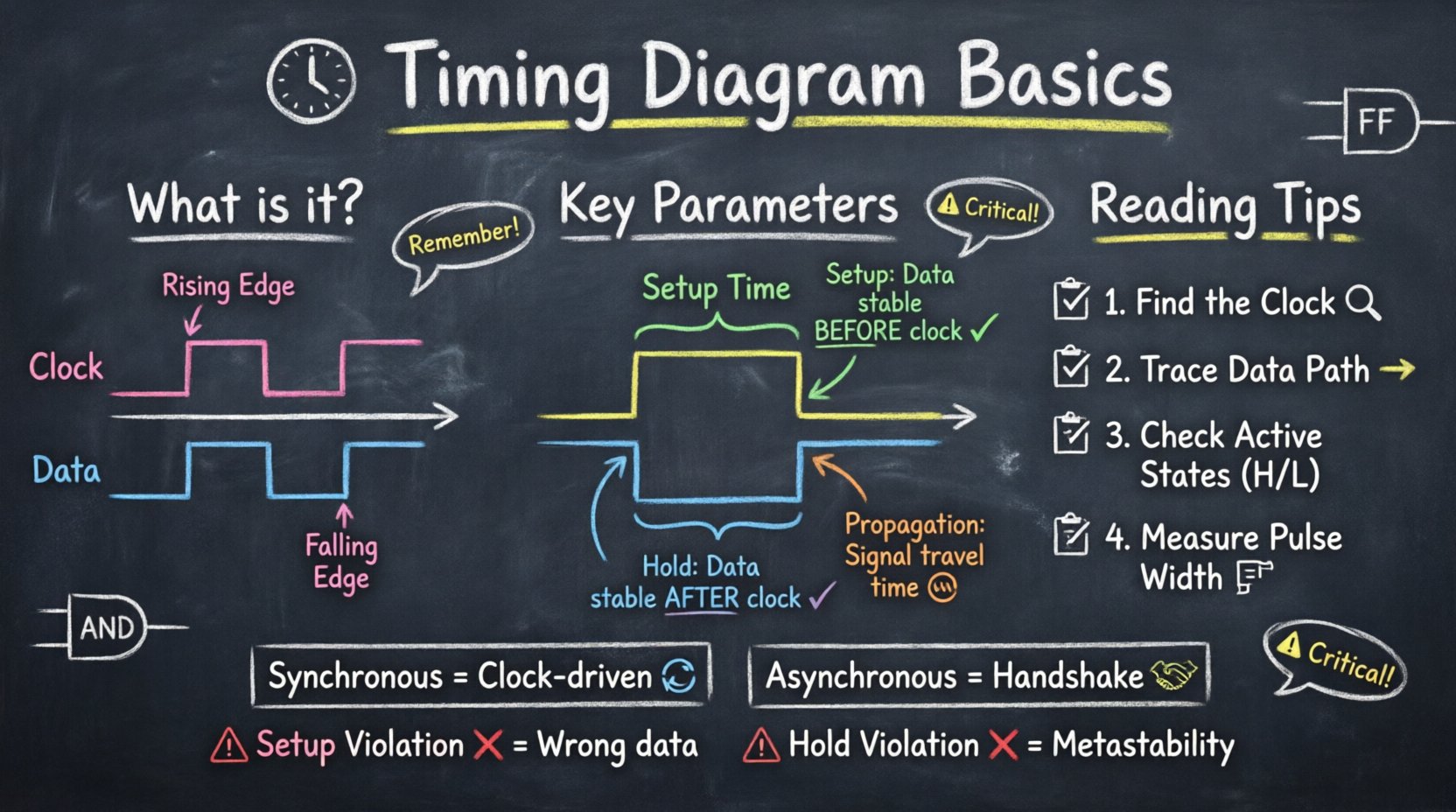

Diagram waktu adalah jenis grafik tertentu yang digunakan untuk menggambarkan hubungan antara dua atau lebih sinyal dalam periode waktu tertentu. Berbeda dengan tabel keadaan logika yang mencantumkan keadaan dalam bentuk grid, diagram waktu memetakan keadaan-keadaan tersebut ke sumbu waktu horizontal. Pendekatan visual ini memungkinkan insinyur melihat urutan kejadian, durasi pulsa, dan sinkronisasi antara bagian-bagian berbeda dalam rangkaian.

Diagram-diagram ini sangat penting dalam beberapa konteks:

- Desain Perangkat Keras:Untuk memverifikasi bahwa data stabil sebelum tepi jam tiba.

- Analisis Protokol:Untuk memahami standar komunikasi seperti I²C, SPI, atau UART.

- Verifikasi Sistem:Untuk memastikan mesin keadaan berpindah dengan benar tanpa kondisi persaingan (race conditions).

- Debugging:Untuk mengidentifikasi pelanggaran setup atau hold yang menyebabkan kegagalan sistem.

Dengan memvisualisasikan waktu, desainer dapat memprediksi bagaimana sistem berperilaku saat dibebani, memastikan keandalan dan kinerja.

Elemen-Elemen Utama Diagram Waktu 🎯

Untuk membaca diagram waktu, seseorang harus terlebih dahulu memahami blok-blok pembentuk dasarnya. Setiap diagram terdiri dari sinyal, waktu, dan transisi. Penataan elemen-elemen ini menceritakan kisah tentang perilaku listrik sistem.

Sinyal dan Garis

Setiap garis horizontal mewakili sinyal tertentu. Ini bisa berupa sinyal jam, jalur data, bus alamat, atau bendera kontrol. Sinyal biasanya diberi label di awal garis atau dalam legenda. Posisi vertikal garis tidak menunjukkan tingkat tegangan; melainkan, posisi vertikal relatif terhadap garis dasar menunjukkan keadaan logika.

Sumbu Waktu

Sumbu horizontal mewakili waktu. Alirannya dari kiri ke kanan. Dalam banyak diagram, interval waktu ditandai dengan garis putus-putus vertikal. Penanda-penanda ini sering sesuai dengan siklus jam. Penting untuk dicatat bahwa skala waktu tidak selalu linier. Terkadang, momen tertentu diperbesar untuk menunjukkan detail mikrodetik atau nanodetik, sementara bagian lain menunjukkan perilaku tingkat makro.

Tingkat Logika

Sinyal biasanya berpindah antara dua keadaan: Tinggi dan Rendah. Ini sesuai dengan biner 1 dan 0. Dalam beberapa konteks, Rendah bisa mewakili keadaan aktif (Active Low), sementara Tinggi mewakili keadaan aktif (Active High). Memahami keadaan aktif sangat penting untuk menafsirkan sinyal kontrol seperti Reset atau Chip Select.

Transisi dan Tepi

Garis vertikal yang menghubungkan tingkat logika mewakili transisi. Ada dua jenis tepi utama:

- Tepi Naik:Transisi dari Rendah ke Tinggi.

- Tepi Turun:Transisi dari Tinggi ke Rendah.

Tepi-tepi ini sering memicu tindakan dalam rangkaian digital. Misalnya, sebuah register bisa memperbarui datanya tepat ketika sinyal jam naik.

Parameter Waktu Kritis ⚙️

Memahami garis-garis statis hanyalah separuh pertarungan. Parameter-parameter dinamis menentukan batasan-batasan di mana sistem harus beroperasi. Melanggar parameter-parameter ini mengakibatkan kerusakan data atau kegagalan sistem.

Waktu Siap

Waktu siap adalah jumlah waktu minimum sebelum tepi clock yang sinyal data harus stabil dan sah. Jika data berubah terlalu dekat dengan tepi clock, sirkuit penerima mungkin tidak memiliki cukup waktu untuk mencatat nilai dengan benar. Parameter ini diterapkan secara ketat dalam sistem sinkron.

Waktu Tahan

Waktu tahan adalah jumlah waktu minimum setelah tepi clock yang sinyal data harus tetap stabil. Bahkan setelah clock telah memicu pengambilan, data tidak boleh berubah segera. Jika berubah terlalu cepat, latch internal atau flip-flop bisa masuk ke keadaan tidak stabil.

Keterlambatan Propagasi

Keterlambatan propagasi adalah waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input komponen ke outputnya. Ini merupakan sifat bawaan dari sifat fisik rangkaian. Ketika beberapa komponen disusun secara berurutan, keterlambatan ini menumpuk, memengaruhi frekuensi operasi maksimum sistem.

Siklus dan Frekuensi Clock

Siklus clock adalah durasi satu periode lengkap dari sinyal clock. Frekuensi adalah kebalikan dari periode ini, diukur dalam Hertz (Hz). Anggaran waktu sistem sering ditentukan oleh periode clock. Jika jumlah semua keterlambatan propagasi melebihi periode clock, sistem akan gagal beroperasi dengan benar.

| Parameter | Definisi | Dampak Pelanggaran |

|---|---|---|

| Waktu Siap | Waktu data harus stabil sebelum tepi clock | Data hilang atau penangkapan yang salah |

| Waktu Tahan | Waktu data harus stabil setelah tepi clock | Metastabilitas atau kerusakan data |

| Keterlambatan Propagasi | Waktu untuk sinyal menempuh logika | Frekuensi maksimum berkurang atau kegagalan waktu |

| Skew | Perbedaan waktu kedatangan sinyal clock | Margin waktu berkurang |

| Jitter | Variasi jangka pendek dalam waktu sinyal | Operasi tidak stabil pada kecepatan tinggi |

Membaca dan Menganalisis Sinyal 📖

Membaca diagram waktu membutuhkan pendekatan sistematis. Terburu-buru dalam memproses informasi visual dapat menyebabkan salah paham terhadap perilaku sistem. Ikuti langkah-langkah berikut untuk menganalisis diagram secara akurat.

- Identifikasi Clock: Temukan sinyal periodik yang menggerakkan sistem. Ini biasanya menjadi acuan untuk semua tindakan lainnya.

- Lacak Jalur Data:Ikuti jalur sinyal dari sumber ke tujuan. Catat di mana data dihasilkan dan di mana data dikonsumsi.

- Periksa Status Aktif:Tentukan apakah sinyal aktif tinggi atau aktif rendah. Sinyal rendah mungkin berarti “Aktifkan,” sementara sinyal tinggi mungkin berarti “Nonaktifkan.”

- Ukur Durasi:Perhatikan lebar pulsa. Apakah pulsa cukup lebar untuk dideteksi? Apakah terlalu sempit sehingga menjadi gangguan?

- Verifikasi Urutan:Pastikan sinyal kontrol berubah dalam urutan yang benar. Misalnya, sinyal Reset harus diberikan sebelum sistem mulai memproses.

Ketika menganalisis diagram yang kompleks, membantu untuk membagi timeline menjadi siklus diskret. Analisis satu periode jam pada satu waktu untuk memahami transisi keadaan.

Sistem Sinkron vs. Asinkron 🔄

Diagram waktu berbeda secara signifikan tergantung pada apakah sistem bersifat sinkron atau asinkron. Memahami perbedaan ini sangat penting untuk interpretasi yang benar.

Sistem Sinkron

Dalam sistem sinkron, semua operasi diatur oleh jam global. Setiap perubahan keadaan terjadi relatif terhadap tepi jam. Ini membuat analisis waktu lebih dapat diprediksi. Anda dapat menghitung kecepatan maksimum sistem dengan menjumlahkan penundaan jalur terpanjang antara dua register. Diagram waktu di sini sangat teratur, dengan kejadian yang sejajar secara vertikal dengan tepi jam.

Sistem Asinkron

Sistem asinkron tidak bergantung pada jam global. Sebaliknya, mereka menggunakan protokol tangan yang mengubah status sinyal berdasarkan kesiapan tahap sebelumnya. Diagram waktu untuk sistem ini tampak kurang teratur. Kejadian dipicu oleh transisi sinyal tertentu alih-alih ketukan periodik. Menganalisis ini memerlukan perhatian cermat terhadap ketergantungan antar sinyal.

Masalah dan Pelanggaran Waktu Umum ⚠️

Bahkan dengan desain yang hati-hati, masalah waktu dapat muncul. Masalah ini sering muncul sebagai kegagalan yang bersifat intermiten dan sulit direplikasi. Mengenali mereka dalam diagram waktu merupakan keterampilan penting untuk menyelesaikan masalah.

Pelanggaran Setup

Pelanggaran setup terjadi ketika data tiba terlambat untuk tepi jam. Secara visual, ini tampak seperti transisi data terjadi setelah tepi jam telah lewat. Hasilnya sering kali komponen penerima menangkap nilai yang salah atau nilai sebelumnya.

Pelanggaran Hold

Pelanggaran hold terjadi ketika data berubah terlalu cepat setelah tepi jam. Ini berarti data baru menimpa data lama sebelum komponen selesai menangkapnya. Ini sangat berbahaya karena dapat menyebabkan metastabilitas, di mana tegangan output mengambang antara level tinggi dan rendah.

Skew dan Jitter

Skew jam terjadi ketika sinyal jam tiba di komponen yang berbeda pada waktu yang berbeda. Jika skew terlalu besar, jendela waktu efektif untuk setup dan hold berkurang. Jitter mengacu pada ketidakstabilan waktu tepi jam. Jitter tinggi membuat sulit untuk menjamin margin waktu, sehingga mengharuskan kecepatan jam yang lebih lambat.

Praktik Terbaik untuk Integritas Sinyal 🛡️

Untuk memastikan kinerja yang kuat, insinyur harus mematuhi praktik terbaik saat mendesain dan menganalisis waktu. Panduan ini membantu meminimalkan risiko dan meningkatkan stabilitas sistem.

- Minimalkan Panjang Jalur:Jalur yang lebih panjang meningkatkan penundaan propagasi dan kerentanan terhadap gangguan. Buat jalur sinyal sependek mungkin jika memungkinkan.

- Sesuaikan Impedansi:Pastikan impedansi jalur transmisi sesuai dengan driver dan penerima untuk mencegah pantulan.

- Gunakan Permukaan Tanah: Permukaan tanah yang padat menyediakan jalur kembali impedansi rendah, mengurangi kebisingan dan gangguan silang.

- Perhitungkan Suhu: Komponen elektronik berperilaku berbeda pada suhu yang berbeda. Margas desain harus mempertimbangkan kondisi termal terburuk.

- Simulasikan Sejak Awal: Gunakan alat simulasi untuk memodelkan perilaku waktu sebelum prototipe fisik dibuat. Ini membantu menangkap pelanggaran sejak awal dalam siklus desain.

Aplikasi dalam Debugging Perangkat Keras 🔍

Diagram waktu bukan hanya untuk desain; mereka adalah alat penting untuk debugging. Ketika suatu sistem gagal, insinyur menggunakan osiloskop atau analis logika untuk menangkap gelombang sinyal yang sebenarnya. Jejak yang ditangkap ini kemudian dibandingkan dengan diagram waktu yang diharapkan.

Jika gelombang nyata menyimpang dari diagram, perbedaan tersebut menunjukkan akar penyebabnya. Sebagai contoh, jika jalur data berisik selama jendela penangkapan, hal ini menunjukkan masalah catu daya atau gangguan elektromagnetik. Jika tepi jam berbentuk miring daripada tajam, hal ini mengindikasikan masalah kekuatan driver.

Dengan menghubungkan data visual dari osiloskop dengan persyaratan logis dari diagram waktu, insinyur dapat menentukan kerusakan dengan tepat. Proses ini mengubah batasan waktu abstrak menjadi bukti fisik yang nyata.

Ringkasan Konsep Kunci 💡

Menguasai dasar-dasar diagram waktu sangat penting dalam bekerja dengan sistem digital. Ini melibatkan pemahaman hubungan antara sinyal, waktu, dan keadaan logika. Dengan memperhatikan parameter seperti waktu siap, waktu tahan, dan waktu propagasi secara cermat, desainer dapat membuat sistem yang beroperasi secara andal pada kecepatan tinggi.

Kemampuan membaca dan menafsirkan diagram ini memungkinkan komunikasi yang efektif antara tim perangkat keras dan perangkat lunak. Ini menghubungkan celah antara logika teoretis dan kenyataan fisik. Baik Anda sedang mendesain rangkaian kontrol sederhana maupun mikroprosesor yang kompleks, analisis waktu tetap menjadi fondasi keberhasilan rekayasa.

Ingatlah untuk selalu memverifikasi status aktif Anda, menghargai batas jam, dan mempertimbangkan keterbatasan fisik. Dengan latihan, membaca representasi visual ini menjadi sesuatu yang alami, memungkinkan Anda mendiagnosis masalah dan mengoptimalkan kinerja dengan percaya diri.