Memahami bagaimana sistem digital berperilaku seiring waktu merupakan dasar dari teknik elektronika dan teknik komputer. Baik sedang merancang antarmuka mikrokontroler atau mendiagnosis protokol komunikasi, menggambarkan transisi sinyal sangat penting. Diagram waktu menyediakan representasi grafis dari satu atau lebih sinyal dalam periode tertentu. Diagram ini berfungsi sebagai gambaran rancangan untuk sinkronisasi, memastikan data berpindah dengan benar antar komponen.

Panduan ini mengeksplorasi mekanisme diagram waktu, komponen kritisnya, dan cara menafsirkannya untuk desain digital yang kuat. Kami akan membahas nuansa siklus jam, status sinyal, dan batasan waktu yang menentukan keandalan sistem.

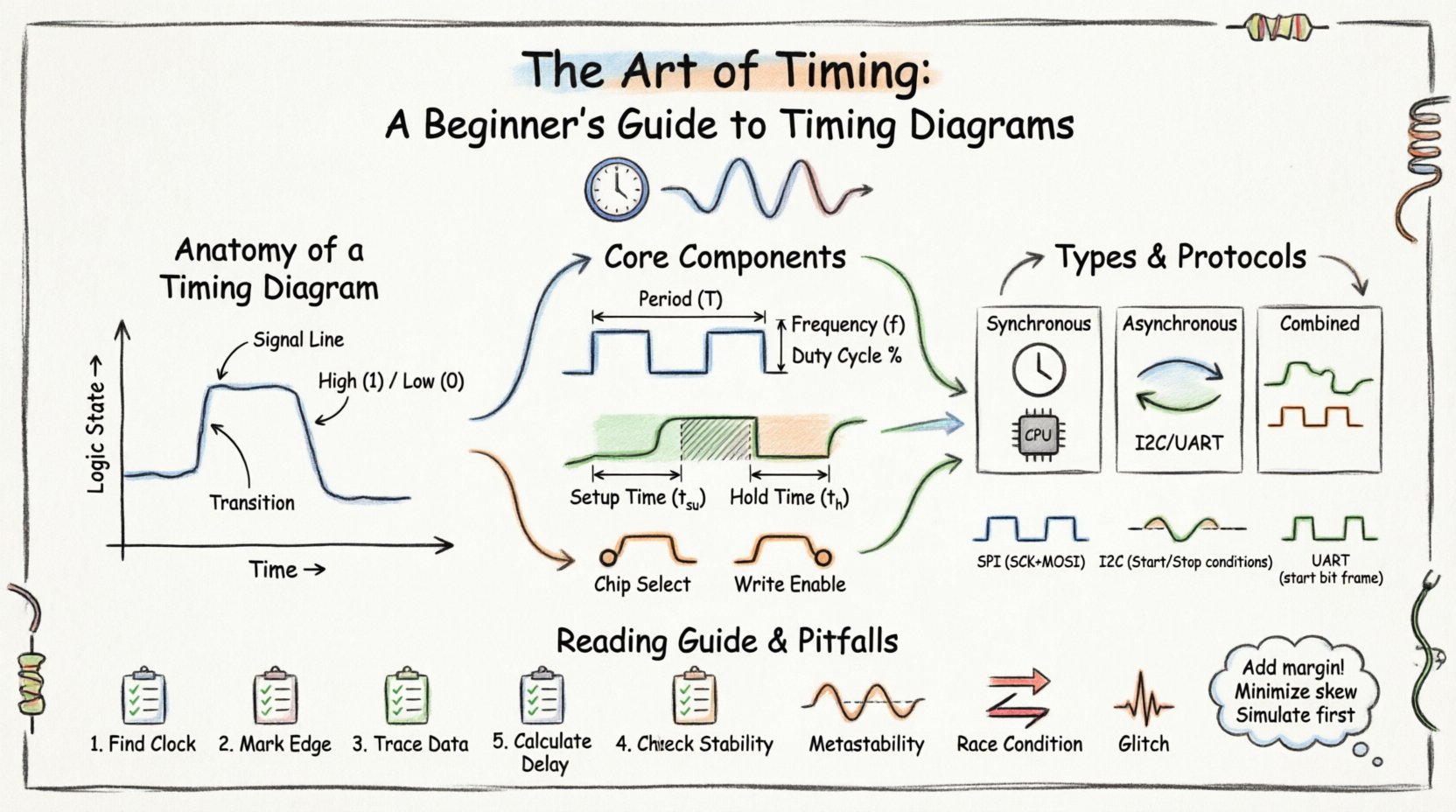

Apa Itu Diagram Waktu? 📊

Diagram waktu memetakan perilaku sinyal sepanjang sumbu horizontal, yang mewakili waktu. Sumbu vertikal mewakili status logika sinyal, biasanya Tinggi (1) atau Rendah (0). Berbeda dengan skema rangkaian yang menunjukkan koneksi, diagram waktu menggambarkan hubungan temporal.

Karakteristik utama meliputi:

- Sumbu Waktu: Biasanya horizontal, bergerak dari kiri ke kanan.

- Garis Sinyal: Setiap garis horizontal mewakili kabel tertentu, bus, atau antarmuka.

- Transisi: Garis vertikal menunjukkan perubahan status (tepi naik atau turun).

- Label: Nama atau pengenal untuk setiap garis sinyal.

Diagram-diagram ini sangat penting untuk memverifikasi bahwa data stabil sebelum tepi jam menangkapnya. Diagram ini menghubungkan kesenjangan antara logika abstrak dan kenyataan fisik.

Komponen Utama Diagram Waktu 🛠️

Untuk membaca diagram waktu secara akurat, seseorang harus memahami blok-blok pembentuknya. Setiap diagram bergantung pada elemen-elemen tertentu untuk menyampaikan informasi mengenai operasi rangkaian.

1. Sinyal Jam ⏰

Jam berfungsi sebagai detak jantung sistem sinkron. Ia menentukan kapan data harus diambil. Dalam diagram, jam biasanya muncul sebagai gelombang persegi. Periode jam menentukan kecepatan maksimum yang dapat dioperasikan sistem.

- Periode (T): Waktu yang dibutuhkan untuk satu siklus lengkap.

- Frekuensi (f): Berapa banyak siklus yang terjadi per detik (Hz).

- Duty Cycle: Persentase periode di mana sinyal berada dalam keadaan Tinggi.

2. Sinyal Data 💾

Garis data membawa informasi sebenarnya. Ini bisa berupa paralel atau serial. Dalam diagram waktu, data ditampilkan bertransisi pada titik-titik tertentu relatif terhadap jam.

- Waktu Siap: Waktu minimum yang harus dihabiskan data agar stabil sebelum tepi jam.

- Waktu Tahan: Waktu minimum data harus tetap stabil setelah tepi clock.

3. Sinyal Kendali 🎛️

Sinyal seperti Chip Select, Write Enable, atau Reset mengelola operasi perangkat. Sinyal-sinyal ini sering muncul sebagai aktif rendah (ditandai dengan bulatan atau garis atas) atau aktif tinggi.

Jenis Diagram Waktu 🔄

Tidak semua diagram waktu identik. Mereka bervariasi tergantung pada arsitektur sistem dan sinyal khusus yang dianalisis.

| Jenis | Deskripsi | Kasus Penggunaan Umum |

|---|---|---|

| Sinkron | Semua sinyal dirujuk ke satu sumber clock tunggal. | Register CPU, antarmuka SDRAM |

| Asinkron | Sinyal beroperasi tanpa referensi clock global. | I2C, UART, protokol handshaking |

| Gabungan | Menunjukkan interaksi antara sinyal yang dikendalikan clock dan yang tidak dikendalikan clock. | Arbitrase bus sistem, penanganan interupsi |

Sistem Sinkron

Dalam desain sinkron, setiap perubahan keadaan terjadi pada tepi clock. Ini membuat analisis waktu dapat diprediksi. Diagram menunjukkan data yang dilepaskan dari satu register dan tiba di register lain dalam satu siklus clock.

Sistem Asinkron

Desain asinkron bergantung pada handshaking. Sinyal “Request” naik, penerima memprosesnya, dan mengirimkan kembali “Acknowledge”. Diagram waktu di sini berfokus pada lebar pulsa dan penundaan respons daripada tepi clock.

Parameter Waktu Kritis ⚙️

Memahami metrik khusus pada diagram waktu adalah kunci otoritas teknis. Parameter-parameter ini menentukan batas kinerja.

Waktu Siap (tsu)

Waktu siap adalah jendela sebelum tepi clock aktif di mana data input harus tetap konstan. Jika data berubah terlalu dekat dengan tepi clock, flip-flop penerima mungkin tidak menangkap nilai dengan benar.

- Pelanggaran:Jika data berubah dalam jendela waktu siap, sistem akan gagal.

- Kendala: Data harus valid setidaknya tsu sebelum tepi jam.

Waktu Tahan (th)

Waktu tahan adalah jendela setelah tepi jam aktif di mana data harus tetap stabil. Bahkan setelah jam memicu pengambilan, data tidak boleh bergerak segera.

- Pelanggaran: Jika data berubah terlalu cepat setelah tepi jam, nilainya hilang.

- Kendala: Data harus tetap valid setidaknya th setelah tepi jam.

Keterlambatan Propagasi (tpd)

Ini adalah waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input ke output melalui gerbang logika atau komponen. Dalam diagram waktu, ini sering divisualisasikan sebagai jarak antara transisi input dan transisi output yang dihasilkan.

- Keterlambatan Logika: Waktu yang dihabiskan untuk pemrosesan di dalam chip.

- Keterlambatan Kabel: Waktu yang dihabiskan untuk menempuh perjalanan melalui jalur papan sirkuit.

Skew ⚡

Skew terjadi ketika sinyal jam tiba di komponen yang berbeda pada waktu yang berbeda. Ini menciptakan ketidaksesuaian dalam waktu yang terasa. Skew yang tinggi dapat mengurangi margin setup dan hold yang tersedia.

Cara Membaca Diagram Waktu 🧐

Menginterpretasi diagram membutuhkan pendekatan sistematis. Ikuti langkah-langkah ini untuk menganalisis perilaku sinyal apa pun.

- Identifikasi Jam: Temukan sinyal periodik. Ini adalah titik acuan Anda.

- Tandai Tepi Aktif: Tentukan apakah sistem memicu pada tepi naik (0 ke 1) atau tepi turun (1 ke 0).

- Lacak Transisi Data:Perhatikan kapan jalur data berubah keadaan relatif terhadap tepi clock.

- Periksa Stabilitas:Pastikan data datar selama jendela setup dan hold.

- Hitung Penundaan:Ukur jarak horizontal antara perubahan input dan respons output.

Kemungkinan Adegan Contoh:

Bayangkan sebuah chip memori menulis data. Diagram menunjukkan:

- Sebuah Sinyal Enable Tulissinyal turun ke rendah.

- Sebuah Jalur Alamatjalur stabil sebelum tepi clock.

- Jalur Datajalur berubah nilai setelah tepi clock memicu.

- Sebuah Pulsa Write Strobepulsa yang menunjukkan durasi operasi penulisan.

Pelanggaran dan Kesalahan Waktu Umum ❌

Bahkan dengan desain yang hati-hati, pelanggaran waktu tetap terjadi. Mengenali mereka dalam diagram membantu mendiagnosis kegagalan sistem.

Metastabilitas

Ketika suatu sinyal melanggar waktu setup atau hold, flip-flop dapat memasuki keadaan metastabil. Ia tidak membaca sebagai Tinggi maupun Rendah, tetapi mengambang pada tegangan yang tidak pasti. Dalam diagram, ini mungkin tampak seperti transisi lambat atau sinyal yang tidak mencapai tegangan rel dalam waktu yang diharapkan.

Kondisi Balapan

Ini terjadi ketika dua sinyal bersaing untuk memengaruhi output yang sama. Jika waktu salah satu sinyal tiba sedikit lebih awal dari yang lain, hasilnya berubah. Diagram menunjukkan ini sebagai transisi yang tumpang tindih yang menciptakan keadaan yang tidak dapat diprediksi.

Gangguan

Pulsa pendek yang tidak diinginkan yang muncul pada jalur sinyal. Ini sering disebabkan oleh perbedaan penundaan propagasi dalam jalur logika paralel. Dalam diagram, mereka tampak sebagai lonjakan kecil yang tidak sesuai dengan logika yang dimaksudkan.

Waktu dalam Protokol Komunikasi 📡

Protokol yang berbeda memiliki persyaratan waktu yang unik. Memahami hal ini sangat penting untuk integrasi.

SPI (Interfacing Periferal Serial)

SPI adalah protokol sinkron. Ia menggunakan Clock (SCK), Master Out Slave In (MOSI), dan Master In Slave Out (MISO). Diagram waktu untuk SPI mendefinisikan:

- Kapan clock mulai berpindah.

- Kapan data diambil (MSB terlebih dahulu atau LSB terlebih dahulu).

- Keadaan idle dari jalur clock.

I2C (Sirkuit Terpadu Antar)

I2C menggunakan jalur clock (SCL) dan data (SDA). Ini adalah jenis open-drain, yang berarti perangkat menarik jalur ke rendah tetapi mengandalkan resistor untuk menariknya ke tinggi. Diagram waktu untuk I2C sangat penting untuk mendefinisikan:

- Kondisi Mulai: SDA berubah dari tinggi ke rendah saat SCL berada pada tinggi.

- Kondisi Berhenti: SDA berubah dari rendah ke tinggi saat SCL berada pada tinggi.

- ACK/NACK: Tanggapan dari perangkat slave.

UART (Penerima dan Pengirim Asinkron Universal)

UART bersifat asinkron, sehingga tidak memiliki jalur clock. Diagram waktu berfokus pada durasi bit. Bit awal memulai frame, diikuti oleh bit data, paritas opsional, dan bit berhenti.

Praktik Terbaik untuk Analisis Waktu ✅

Untuk memastikan desain kuat, ikuti praktik rekayasa berikut ini.

- Margin Kesalahan: Rancang dengan waktu setup dan hold yang lebih besar dari minimum yang dibutuhkan. Faktor lingkungan seperti suhu dan tegangan dapat menurunkan kinerja.

- Minimalkan Skew:Rancang jalur clock dengan hati-hati agar tiba secara bersamaan di komponen-komponen.

- Gunakan Buffer: Jika sinyal menempuh jarak terlalu jauh, gunakan buffer untuk memulihkan kekuatan sinyal dan mengurangi ketidakpastian penundaan.

- Verifikasi dengan Simulasi: Sebelum membangun perangkat keras, simulasi diagram waktu untuk menangkap pelanggaran lebih awal.

- Dokumentasikan dengan Jelas: Pastikan diagram waktu dalam dokumentasi diberi label dengan satuan (ns, µs) dan titik acuan.

Pertimbangan Lanjutan untuk Desain Kecepatan Tinggi 🚀

Ketika laju data meningkat, waktu menjadi lebih kompleks. Pada frekuensi tinggi, sifat fisik rangkaian mendominasi.

Integritas Sinyal

Refleksi dan crosstalk dapat merusak sinyal. Diagram waktu mungkin menunjukkan sinyal yang meloncat terlalu jauh atau bergetar. Insinyur harus mempertimbangkan kesesuaian impedansi untuk mencegah distorsi ini.

Jitter

Jitter adalah penyimpangan tepi sinyal dari posisi idealnya. Jitter tinggi mengurangi margin setup dan hold yang efektif. Pada diagram waktu, ini tampak sebagai tepi yang ‘kabur’ atau ‘blurry’ alih-alih garis vertikal yang tajam.

Sirkuit Pengunci Fasa (PLL)

PLL menyinkronkan jam internal dengan referensi eksternal. Diagram waktu untuk PLL menunjukkan waktu penguncian dan karakteristik noise fase, yang sangat penting untuk menjaga integritas data pada tautan berkecepatan tinggi.

Ringkasan Konsep Kunci 📝

Diagram waktu adalah bahasa sinkronisasi digital. Mereka menerjemahkan logika abstrak menjadi batasan temporal yang nyata. Dengan menguasai interpretasi diagram ini, insinyur dapat memprediksi perilaku dan mencegah kegagalan.

- Waktu adalah dimensi:Semua diukur relatif terhadap jam atau titik referensi.

- Stabilitas adalah kunci:Sinyal harus tetap stabil selama jendela setup dan hold.

- Keterlambatan penting:Keterlambatan propagasi memengaruhi frekuensi operasi maksimum.

- Variasi ada:Suhu dan tegangan memengaruhi parameter waktu.

Baik bekerja pada sistem embedded sederhana maupun prosesor yang kompleks, kemampuan membaca dan membuat diagram waktu merupakan kompetensi utama. Ini menjamin bahwa perangkat keras fisik berfungsi persis seperti yang dimaksudkan oleh desain logika.