Di dunia elektronika digital dan desain sistem, waktu bukan hanya sebuah dimensi; itu adalah parameter kritis yang menentukan apakah suatu rangkaian berfungsi dengan benar atau gagal secara kacau.Diagram waktuberfungsi sebagai bahasa visual yang digunakan insinyur untuk berkomunikasi tentang bagaimana sinyal berperilaku seiring waktu. Baik Anda sedang merancang antarmuka mikrokontroler, mendiagnosis bus memori, atau menganalisis transmisi data berkecepatan tinggi, memahami diagram ini adalah hal yang tak bisa ditawar.

Panduan ini mengeksplorasi mekanisme diagram waktu, menguraikan perilaku sinyal yang kompleks menjadi komponen-komponen yang mudah dipahami. Kami akan bergerak dari definisi dasar hingga teknik analisis lanjutan, memastikan Anda memiliki alat untuk menafsirkan gelombang dengan presisi.

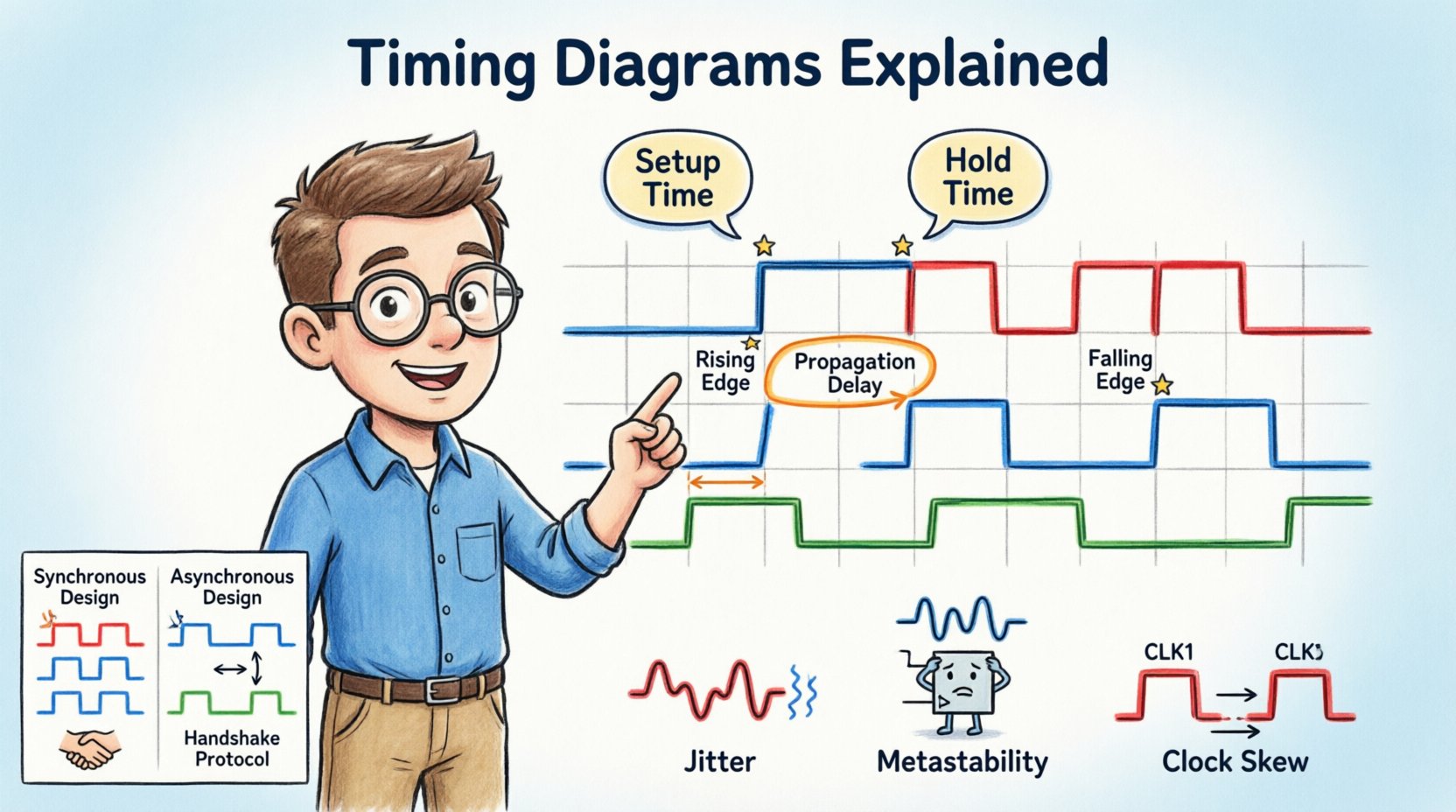

🔍 Apa itu Diagram Waktu?

Diagram waktu adalah representasi grafis dari urutan perubahan sinyal dalam sistem digital. Berbeda dengan skematik, yang menunjukkan bagaimana komponen terhubung, diagram waktu menggambarkankapankapan koneksi-koneksi tersebut berubah keadaan. Diagram ini memetakan aktivitas sinyal sepanjang sumbu waktu horizontal, memungkinkan desainer memverifikasi bahwa data stabil sebelum tepi clock atau bahwa sinyal kontrol diberikan pada saat yang tepat.

Diagram ini sangat penting untuk:

- Memverifikasi interaksi antara perangkat keras dan perangkat lunak.

- Mendiagnosis protokol komunikasi.

- Memastikan persyaratan waktu setup dan hold terpenuhi.

- Mendokumentasikan perilaku sistem untuk pemeliharaan di masa depan.

Tanpa pemahaman yang jelas tentang waktu, bahkan rangkaian yang secara logis benar dapat gagal karena persaingan sinyal atau metastabilitas.

🛠️ Komponen Utama Diagram Waktu

Untuk membaca diagram waktu secara efektif, Anda harus mengidentifikasi blok-blok pembentuk dasarnya. Setiap elemen membawa informasi khusus mengenai keadaan dan aliran sistem digital.

1. Sumbu Waktu

Garis horizontal mewakili perkembangan waktu. Biasanya mengalir dari kiri ke kanan. Dalam dokumen teknis yang rinci, sumbu ini dapat diberi tanda dengan satuan waktu tertentu (nanosekon, picosekon) atau siklus clock.

2. Jalur Sinyal

Garis vertikal mewakili sinyal-sinyal individu, seperti jalur clock, bus data, atau jalur kontrol (seperti chip select atau baca/tulis). Setiap garis sesuai dengan node tertentu dalam rangkaian.

3. Tingkat Logika

Sinyal biasanya berada dalam salah satu dari dua keadaan:

- Tinggi (Logika 1 / VCC):Sering diwakili oleh garis di bagian atas jalur sinyal.

- Rendah (Logika 0 / GND):Diwakili oleh garis di bagian bawah jalur sinyal.

Beberapa sistem menggunakanLogika Rendah Aktiflogika, di mana sinyal melakukan fungsinya ketika tegangan rendah. Dalam diagram, hal ini sering ditandai dengan bulatan di nama sinyal atau notasi khusus.

4. Transisi

Transisi adalah saat-saat ketika suatu sinyal berubah dari Tinggi ke Rendah atau Rendah ke Tinggi.

- Sudut Naik:Transisi dari Rendah ke Tinggi. Sangat penting untuk memicu kejadian.

- Sudut Turun:Transisi dari Tinggi ke Rendah. Digunakan untuk urutan kontrol tertentu.

- Dipicu oleh Sudut:Sinyal hanya dievaluasi selama transisi, bukan pada keadaan stabil.

⚙️ Parameter Waktu Utama

Desain digital yang akurat bergantung pada pengukuran hubungan antar sinyal. Parameter berikut ini merupakan dasar analisis waktu.

1. Keterlambatan Propagasi (tpd)

Ini adalah waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input gerbang logika atau komponen ke outputnya. Tidak ada sinyal yang berubah secara instan; keterbatasan fisik menyebabkan keterlambatan.

- Signifikansi: Jika keterlambatan terlalu panjang, logika berikutnya mungkin menerima data terlambat, menyebabkan kesalahan.

- Pengukuran: Diukur dari titik tegangan 50% transisi input hingga titik tegangan 50% transisi output.

2. Waktu Persiapan (tsu)

Waktu persiapan adalah durasi minimum yang harus stabil bagi sinyal datasebelumsudut jam tiba.

- Skenario: Jika flip-flop membutuhkan data siap 5 nanosekon sebelum jam berfungsi, maka itulah waktu persiapan.

- Pelanggaran: Jika data berubah terlalu dekat dengan sudut jam, sistem tidak dapat menangkap nilai dengan benar.

3. Waktu Tahan (th)

Hold time adalah durasi minimum yang harus tetap stabil pada sinyal datasetelahsatu tepi clock tiba.

- Skenario:Flip-flop perlu “melihat” data selama periode singkat setelah pemicu agar dapat terkunci dengan aman.

- Pelanggaran:Jika data berubah segera setelah tepi clock, input mungkin tidak terkunci dengan benar.

4. Clock Skew

Clock skew terjadi ketika sinyal clock tiba di komponen yang berbeda pada waktu yang berbeda. Hal ini sering disebabkan oleh perbedaan panjang jalur pada papan sirkuit.

- Skew Positif:Clock tiba lebih lambat di tujuan.

- Skew Negatif:Clock tiba lebih awal di tujuan.

5. Jitter

Jitter adalah variasi jangka pendek dari waktu instan penting suatu sinyal dari posisi idealnya dalam waktu. Ini menambah ketidakpastian dalam analisis waktu.

📊 Perbandingan: Desain Sinkron vs. Asinkron

Memahami perbedaan antara dua filosofi desain ini sangat penting untuk menafsirkan diagram waktu dengan benar.

| Fitur | Waktu Sinkron | Waktu Asinkron |

|---|---|---|

| Sinyal Kendali | Menggunakan clock global | Menggunakan sinyal handshaking |

| Keprediksiannya | Sangat dapat diprediksi | Bervariasi tergantung beban |

| Kompleksitas | Membutuhkan distribusi clock | Membutuhkan logika handshaking yang kompleks |

| Konsumsi Daya | Bisa tinggi (pemutaran jam) | Sering lebih rendah (dorongan aktivitas) |

| Diagram Waktu | Diselaraskan dengan tepi jam | Tergantung pada penyelesaian status sebelumnya |

🧐 Cara Membaca dan Menganalisis Diagram Waktu

Menganalisis gelombang membutuhkan pendekatan sistematis. Ikuti langkah-langkah berikut untuk memastikan Anda tidak melewatkan detail penting.

Langkah 1: Identifikasi Jam

Temukan sinyal jam utama. Ini biasanya menjadi acuan untuk semua waktu lainnya. Dalam sistem sinkron, setiap transisi data seharusnya secara ideal dirujuk ke tepi jam ini.

Langkah 2: Periksa Kecurigaan

Periksa adanya pulsa pendek yang tidak diinginkan (kecurigaan) pada jalur sinyal. Ini dapat menyebabkan pemicu palsu pada gerbang logika. Pada diagram yang bersih, transisi seharusnya bersih, meskipun penangkapan dunia nyata sering menunjukkan gangguan.

Langkah 3: Verifikasi Jendela Setup dan Hold

Gambar garis vertikal imajiner yang mewakili jendela setup dan hold di sekitar tepi jam aktif. Pastikan sinyal data stabil dalam zona-zona ini.

Langkah 4: Periksa Sinyal Kendali

Pastikan sinyal kendali seperti Chip Select (CS) atau Enable (EN) aktif selama seluruh durasi transfer data. Jika sinyal kendali turun saat data masih dikirim, terjadi kerusakan data.

Langkah 5: Ukur Interval

Hitung waktu antara peristiwa tertentu. Misalnya, ukur latensi dari sinyal “Permintaan” ke sinyal “Respons”. Ini membantu memvalidasi kinerja terhadap spesifikasi.

🚀 Konsep Lanjutan dalam Analisis Waktu

Seiring sistem menjadi lebih cepat dan kompleks, diagram waktu dasar berkembang menjadi kebutuhan analisis yang canggih.

1. Metastabilitas

Metastabilitas terjadi ketika flip-flop menerima input yang melanggar persyaratan waktu setup atau hold. Alih-alih menyelesaikan menjadi 0 atau 1 yang jelas, output memasuki keadaan tak terdefinisi selama durasi yang tidak dapat diprediksi.

- Penyebab:Sering terjadi ketika sinyal asinkron melintasi domain jam.

- Penanggulangan:Gunakan rantai sinkronisasi (beberapa flip-flop secara seri) untuk mengurangi kemungkinan metastabilitas.

- Visual:Pada diagram waktu, ini tampak seperti sinyal bergetar atau membutuhkan waktu yang sangat lama untuk stabil.

2. Anggaran Waktu Setup dan Hold

Insinyur menghitung anggaran waktu untuk memastikan sistem beroperasi pada frekuensi maksimum. Ini melibatkan pengurangan semua penundaan (kabel, gerbang, skew jam) dari periode jam.

Jika total penundaan melebihi waktu yang tersedia, frekuensi operasi maksimum harus dikurangi.

3. Waktu Antarmuka Kecepatan Tinggi

Antarmuka seperti memori DDR atau PCIe memerlukan waktu yang sangat presisi. Diagram ini sering mencakup:

- Diagram Mata: Superposisi banyak transisi sinyal untuk memvisualisasikan kualitas sinyal.

- Distorsi Siklus Kerja:Memastikan waktu Tinggi dan Rendah seimbang.

- Penyelarasan Fasa:Memastikan data dan clock tiba secara sinkron di seluruh bit.

4. Status Manajemen Daya

Perangkat modern memasuki mode hemat daya. Diagram waktu harus mempertimbangkan latensi bangun tidur. Sebagai contoh, sinyal yang menyalakan daya ke perangkat tambahan harus terjadi sebelum perangkat siap menerima data.

📝 Praktik Terbaik untuk Dokumentasi

Dokumentasi yang jelas mencegah kesalahan selama pengembangan dan debugging. Patuhi standar ini saat membuat atau meninjau diagram waktu.

- Skala Konsisten: Gunakan skala waktu yang konsisten di seluruh diagram yang terkait agar memudahkan perbandingan.

- Label yang Jelas: Setiap sinyal harus diberi label dengan fungsi dan polaritas logika (misalnya,

RESET#untuk Aktif Rendah). - Tingkat Zoom: Sediakan gambaran umum tingkat tinggi dan tampilan yang diperbesar dari transisi kritis (seperti jendela setup/hold).

- Kode Warna: Gunakan warna untuk membedakan antara domain tegangan yang berbeda atau sumber clock (misalnya, Merah untuk Clock, Biru untuk Data).

- Kontrol Versi: Persyaratan waktu berubah. Pastikan diagram diberi versi agar sesuai dengan revisi perangkat keras.

🛠️ Kesalahan Umum dan Pemecahan Masalah

Bahkan insinyur berpengalaman mengalami masalah waktu. Berikut adalah skenario umum dan cara menanganinya.

Kesalahan 1: Mengabaikan Penundaan Jalur

Jalur PCB memiliki panjang fisik, yang menyebabkan penundaan. Pada frekuensi tinggi, beberapa inci kabel dapat setara dengan satu siklus clock.

- Solusi: Pertimbangkan panjang jejak dalam perhitungan anggaran waktu Anda.

Kesalahan 2: Input Mengambang

Input yang tidak terhubung dapat mengambang ke tegangan menengah, menyebabkan osilasi.

- Solusi:Pastikan semua input memiliki resistor pull-up atau pull-down yang didefinisikan.

Kesalahan 3: Kondisi Balapan

Ketika dua sinyal berubah secara bersamaan, urutan kedatangan menentukan hasilnya.

- Solusi:Gunakan logika sinkronisasi atau mesin keadaan untuk mengurutkan kejadian.

Kesalahan 4: Overshoot dan Undershoot

Refleksi sinyal dapat menyebabkan tegangan melebihi sumber daya (overshoot) atau turun di bawah tanah (undershoot).

- Solusi:Terapkan resistor terminasi yang tepat dan keselarasan impedansi.

🔗 Aplikasi Dunia Nyata

Diagram waktu diterapkan di berbagai bidang teknik.

1. Antarmuka Memori

DRAM dan SDRAM membutuhkan urutan waktu yang ketat untuk operasi Baca/Tulis. Latensi CAS dan keterlambatan RAS ke CAS adalah parameter penting yang divisualisasikan dalam diagram ini.

2. Komunikasi Mikrokontroler

Protokol seperti I2C, SPI, dan UART bergantung pada hubungan waktu khusus antara jalur clock dan data. Misalnya, pada I2C, jalur data harus stabil saat clock dalam keadaan tinggi.

3. Penjadwalan Sumber Daya

Sistem yang kompleks membutuhkan sumber daya untuk menyala dalam urutan tertentu. Diagram waktu memastikan tegangan inti stabil sebelum tegangan I/O diterapkan.

🎯 Ringkasan Poin Penting

Menguasai diagram waktu membutuhkan kesabaran dan perhatian terhadap detail. Poin-poin berikut merangkum pengetahuan penting untuk desain dan analisis yang efektif.

- Waktu Sangat Kritis:Logika digital bergantung pada hubungan temporal yang tepat antar sinyal.

- Setup dan Hold:Ini adalah dua batasan paling umum yang menentukan kecepatan operasi maksimum.

- Verifikasi Visual:Diagram memungkinkan Anda melihat konflik potensial sebelum perangkat keras dibangun.

- Konteks Sangat Penting: Selalu pertimbangkan lingkungan fisik (PCB, suhu, tegangan) yang memengaruhi waktu sinyal.

- Standarisasi:Gunakan simbol dan notasi standar untuk memastikan kejelasan komunikasi di seluruh tim.

Dengan menerapkan prinsip-prinsip ini, Anda memastikan sistem digital Anda kuat, andal, dan berkinerja tinggi. Kemampuan untuk memahami dan membuat diagram ini adalah keterampilan dasar yang membedakan desain yang berfungsi dari yang gagal di lapangan.

📈 Bergerak Maju

Seiring perkembangan teknologi, batasan waktu menjadi lebih ketat. Sistem modern beroperasi pada kecepatan gigahertz di mana nanodetik sangat berpengaruh. Pembelajaran berkelanjutan mengenai integritas sinyal dan penutupan waktu diperlukan bagi insinyur yang bekerja pada perangkat keras mutakhir.

Mulailah dengan menganalisis skematik yang ada dan diagram waktu yang sesuai. Latih diri dalam mengukur interval dan mengidentifikasi pelanggaran. Seiring waktu, pola-pola ini akan menjadi intuitif, memungkinkan Anda memprediksi masalah sebelum muncul secara fisik.